command bus training(×16 die)

先提一下FSP:

LPDDR4支持两种工作频率的切换,并且会将这两种训练后的工作频率的模式寄存器的parameter信息全部保存,通过模式寄存器的配置来实现两种工作频率的切换而不会出现未训练传输不可靠的状态。

LPDDR4会提供默认的判决电压Vref(CA)值支持un-terminated、低频率的工作,但是需要训练到支持terminated、高频率工作的判决电压值。

不论LPDDR4从哪一种工作频率进入训练,LPDDR4在训练过程都会自动的切换至另一种工作频率的配置完成训练,从训练中退出之后LPDDR4继续回到进入训练前的工作频率,训练前的状态是被认为一个训练好的工作状态。训练好之后的判决电压不会被保留到训练的工作频率,需要在退出训练后写到寄存器。

训练中引脚各自作用:

DQS[0]为input,捕获DQ[6:0]的值,DQ[6:0]需要去toggle;

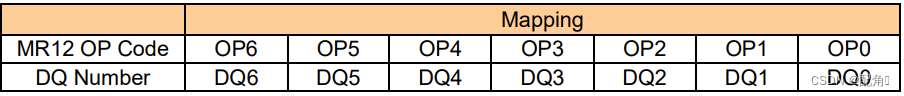

DQ[5:0]为input,设置CA判决电压的值,DQ[6]为input,设置CA判决电压的范围,mapping关系如下:

DQ[7]和DMI[0]为input,输入电平可以是有效的也可以是悬空的;

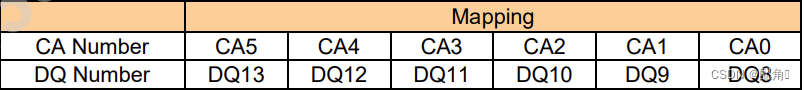

DQ[13:8]为output,返回CA bus的捕获值by CS,下图为mapping关系:

DQS[1] 、DMI[1] 、DQ[15:14]为output,SDRAM可能会驱动为有效值也可能悬空。

如何进入训练模式:首先通过MRW

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

437

437

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?