其实在武汉工资到手9000元是相对不错的待遇,尤其是针对一线城市的工资水平而言。在这个收入水平下,一般可以满足基本的生活需求,如食宿、交通和娱乐等。同时,9000元的工资也能够让人有一定的储蓄和投资能力,提升个人经济状况。然而,随着生活成本的不断上涨,9000元的工资在武汉可能无法实现很高的生活质量,需要进一步提高收入水平以应对日益增长的支出压力。

看看其它武汉网友的工资

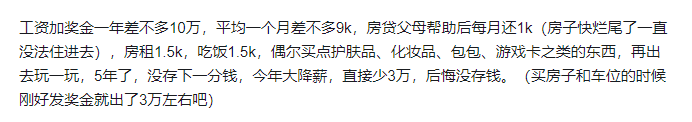

工资加奖金一年差不多10万,平均一个月差不多9k,房贷父母帮助后每月还1k(房子快烂尾了一直没法住进去),房租1.5k,吃饭1.5k,偶尔买点护肤品、化妆品、包包、游戏卡之类的东西,再出去玩一玩,5年了,没存下一分钱,今年大降薪,直接少3万,后悔没存钱。(买房子和车位的时候刚好发奖金就出了3万左右吧

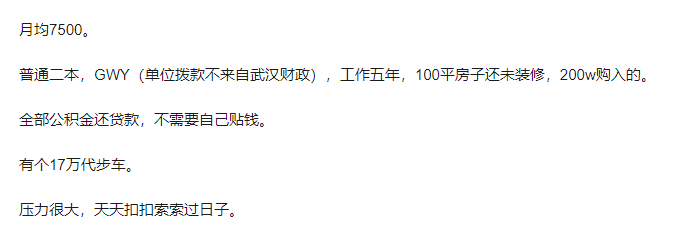

月均7500。普通二本,GWY(单位拨款不来自武汉财政),工作五年,100平房子还未装修,200w购入的。全部公积金还贷款,不需要自己贴钱,有个17万代步车。压力很大,天天扣扣索索过日子。

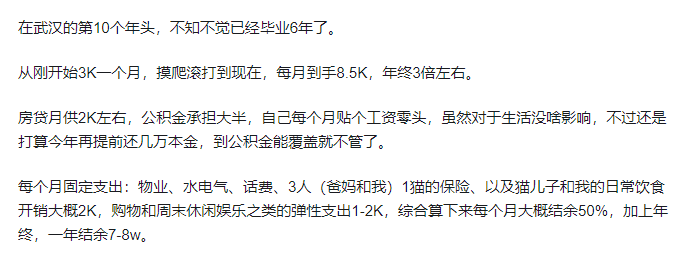

在武汉的第10个年头,不知不觉已经毕业6年了

从刚开始3K一个月,摸爬滚打到现在,每月到手8.5K,年终3倍左右。

房货月供2K左右,公积金承担大半,自己每个月贴个工资要头,虽然对于生活没啥影响,不过还是打算今年再提前还几万本金,到公积金能覆盖就不管了,

每个月固定支出:物业、水电气、话费、3人(爸妈和我)1猫的保险、以及猫儿子和我的日常饮食开销大概2K,购物和周末休闲娱乐之类的弹性支出1-2K,综合算下来每个月大概结余50%,加上年终,一年结余7-8w。

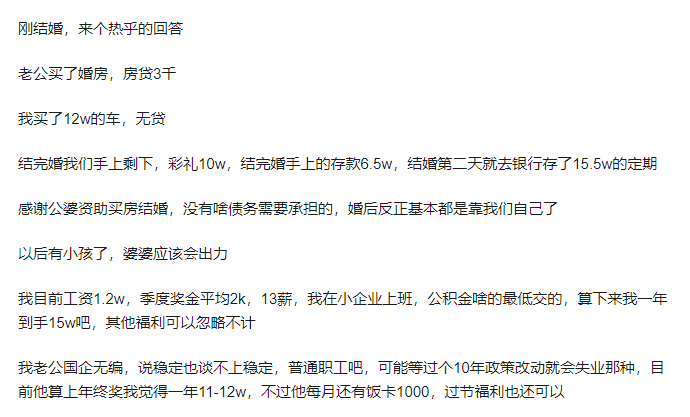

刚结婚,来个热乎的回答,老公买了婚房,房贷3千,我买了12w的车,无贷

结完婚我们手上剩下,彩礼10w,结完婚手上的存款6.5w,结婚第二天就去银行存了15.5w的定期感谢公婆资助买房结婚,没有啥债务需要承担的,婚后反正基本都是靠我们自己了,以后有小孩了,婆婆应该会出力,我目前工资1.2w,季度奖金平均2k,13薪,我在小企业上班,公积金啥的最低交的,算下来我一年到手15w吧,其他福利可以忽略不计

我老公国企无编,说稳定也谈不上稳定,普通职工吧,可能等过个10年政策改动就会失业那种,目前他算上年终奖我觉得一年11-12w,不过他每月还有饭卡1000,过节福利也还可以

有人说:在武汉月入9000块属于中等收入,比上不足,比下有余。如果是武汉本地姑娘家里有房有车,只要不瞎买奢侈品,那小日子会过得还不错。如果是外地人需要租房什么的,那就过得很一般。

还有人说:武汉社会工资中位数4000左右,到手9000你的薪水税前算起来大概12000左右快13000,三倍中位数不止,你说是个什么水平。互联网百万年薪遍地走,所以这个收入拿不出手,但是你要知道你已经远超大多数人了,比上不足比下还是有余的。富有富的活法,穷有穷的过法

其它网友说:很不错的工资收入了,足以秒杀9成武汉上班族了。不要听知乎那些人动不动30起步,哪有那么容易挣钱哟。有了这个收入,平时节省点,好好过日子,不必要的开销就省下来的,毕竟谁也不知道未来会咋样。找个差不多收入的女朋友,两个人一起生活的美滋滋的,基本上可以实现厨房自由了,未来可期呢,少年!

其实不管在哪里上班,路选择好了就踏实的去做,生活品质确实需要金钱来提升,但是人生很多快乐的时光也是钱买不来的,人生小满胜大全,祝各位职场顺利升职加薪!

下方扫码关注 Python测试社区,获取互联网职场最新资讯、趣事,提高个人情绪价值!

上一篇:你们领导干什么吃的,没有家庭吗?

1203

1203

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?