数字电子时钟设计

前言

数字电子钟是一种用数字电路设计实现的时分秒计时的装置,它与机械式的时钟相比,具有更高的,准确的和直观性,且无机械装置具有更长的使用寿命。

从原理上讲,数字电子钟是一种典型的数字电路,其中包括了组合逻辑电路和时序逻辑电路,目前数字电子钟的功能越来越强,并且有多种专门的大规模集成电路可供选择。

从学习角度考虑,这里主要用中小规模集成电路来设计数字电子钟。简易数字电子钟具有正常时间显示与计时的功能,根据课程设计任务书要求,此设计书中数字钟可以显示秒、分、时的功能,以及具有校正的功能(因为快校正设计复杂、不易实现,所以采取慢校正)。具体可利用计数器、译码器、显示器实现此数字钟,另外可以添加其他电路来实现额外功能,例如:整点报时,闹钟等。

一、 实验目的

1. 掌握数字钟的设计方法和调试方法。

2. 掌握计数器的用法。

3. 学会解决实际中出现的问题,如数字钟的校准问题。

二、 实验设备

Proteus仿真软件(采用里边的74LS90芯片,少量逻辑器件);

三、设计要求

1.设计思路清晰,给出整体设计框图,画出整机原理图;

2.给出具体设计思路,设计各单元电路、电路器件;

3.总电路设计;

4.进行实验调试,验证设计结果;

5.编写实验设计说明书;

四、实验步骤

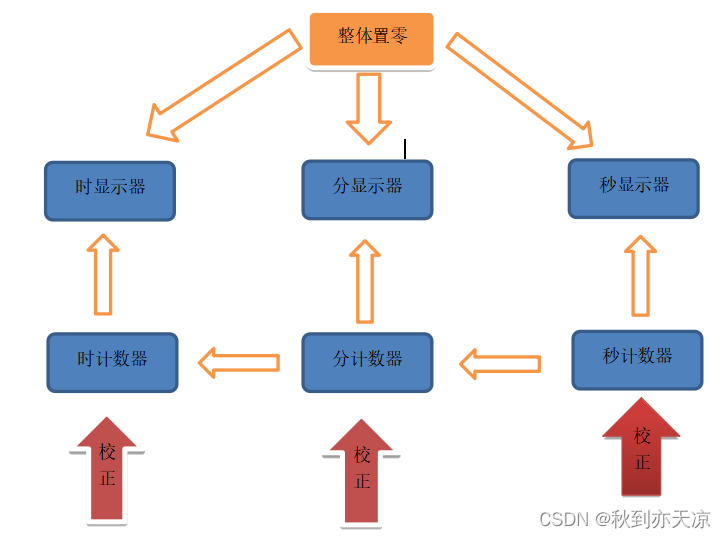

1.总体思路和基本原理

数字电子钟由以下几部分组成:秒脉冲发生器;校时电路;六十进制秒、分计数器,二十四进制时计数器;秒、分、时的译码显示部分。数字电子钟是将“时”、“分”、“秒”显示出来的计时装置,它的计时周期是24小时,显示满刻度是23时59分59秒,另外应有校时功能。

计数的基本原理是将标准秒信号送入“秒计数器”,“秒计数器”采用60进制计数器,每累计60秒发出一个“分脉冲”信号,该信号将作为“分计数器”的时钟脉冲。“分计数器”也采用60进制计数器,每累计60分钟,发出一个“时脉冲”信号,该信号将被送到“时计数器”。“时计数器”采用24进制计时器,可实现对一天24小时的累计。

整体清零的基本原理是采用多个或门的方式从而实现对74LS90芯片的两个置零端(R0,R1)的控制,使用一个连接有高电平的开关和所有置零段相连,当开关闭合所有R0,R1的状态为”1”,直接置零。

时分秒校准电路的基本原理是在接收脉冲端CLKA处连接一个双刀开关,当开关拨向原本脉冲源则正常工作,当开关拨向校准端则开始校准,校准电路也很简单,使用一个低电平脉冲和一个开关,因为CLKA是低电平有效,所以利用开关的断开和闭合来实现不断地给CLKA低电平脉冲从而实现校准功能。

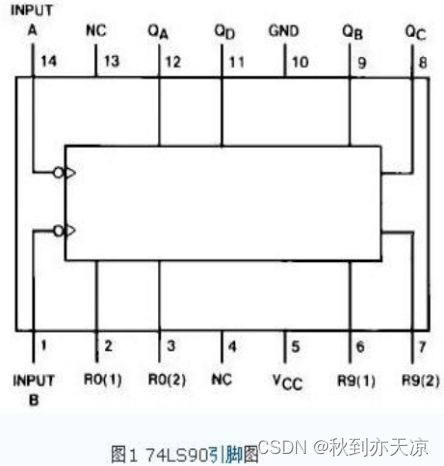

2.74ls90的逻辑符号

3.74ls90的逻辑功能描述

74ls90是异步二-五-十进制加法计数器,它既可以做二进制加法计数器,又可以做5进制和10进制加法计数器。

通过不同的连接方法,74ls90可以实现4种不同的逻辑功能,还可以借助R1,R2对计数器清零,借助S1,S2将计数器置9。

其具体功能详细如下:

(1)计数器脉冲从CP1输入,QA为输出端,为二进制计数器。

(2)计数器脉冲从CP2输入,QDQCQB作为输出端,为异步5进制,加法计数器。

(3)若将CP2与QA相连,记数器脉冲由CP1输入,QD QC QB QA作为输出端,则构成异步8421码10进制加法计数器。

(4)若将CP1与QD相连,计数器脉冲由CP2输入,QA QD QC QB为输出端,则构成异步5421码10进制加法计数器。

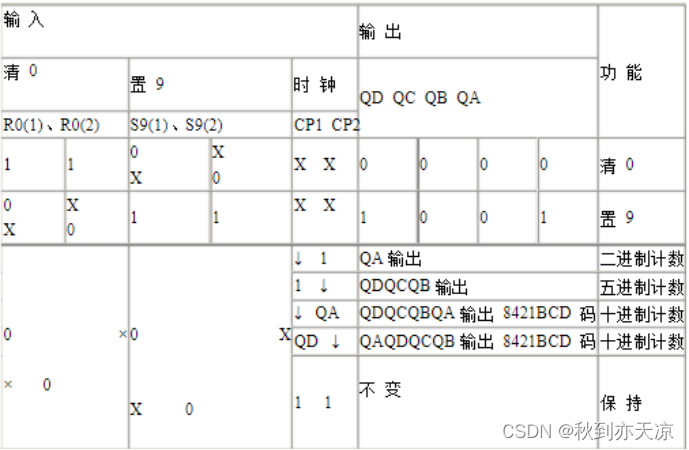

(5)清零,置九 功能

a)异步清零

当R1R2均为1,S1S2中有零时,实现异步清零功能,

即QDQBQCQA=0000

b)置九功能

当S1S2均为1,R1R2中有0时,实现异步清零功能,

即QDQCQBQA=1001

4.74ls90的功能表

5.设计框图

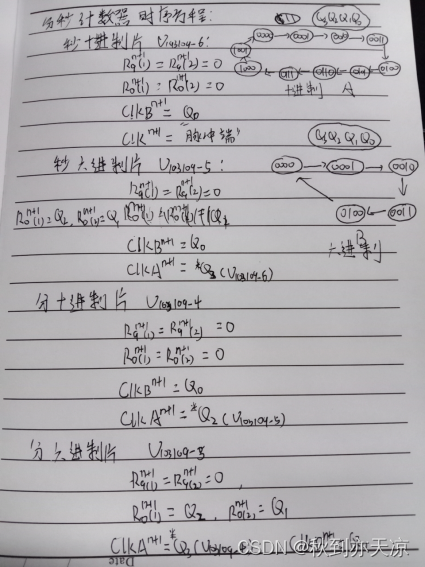

6.计数器设计

分秒计数器具体设计方案:

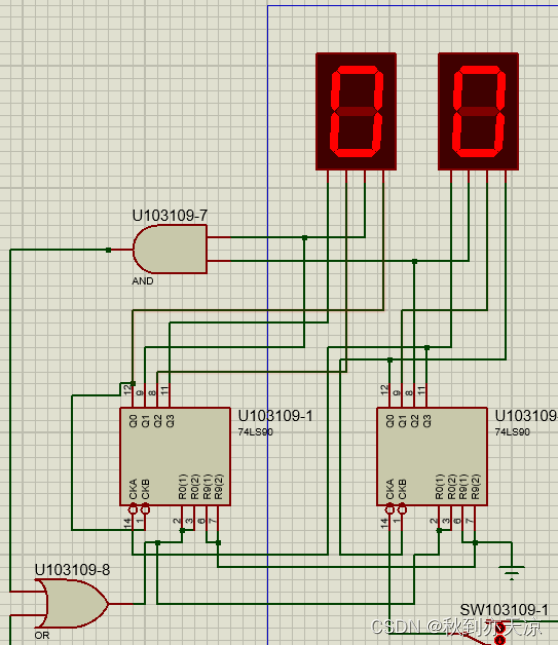

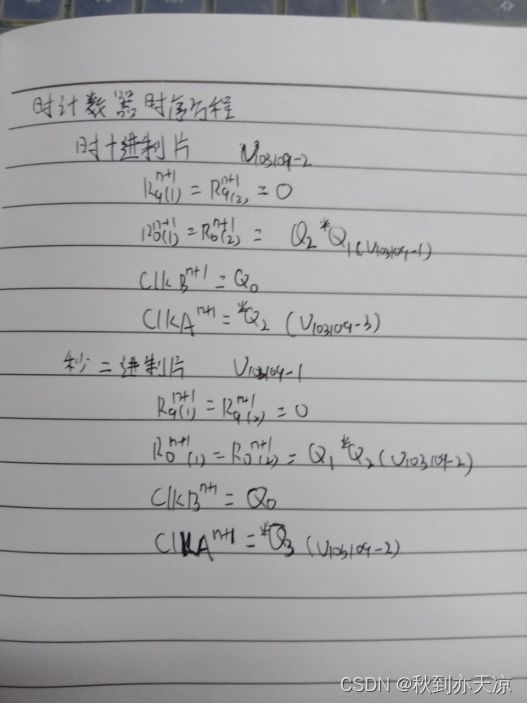

用两片74LS90芯片如图(a),一片控制个位,为十进制;另一片控制十位,为六进制。利用74LS90本身的两控制端完成十进制,在达到1001(即十进制的九)时,给第二个芯片一个脉冲,这样反复,直到第二片达到0110时第二片自身清零,这样完成一次60的计数,且回到初态,两片74LS90全部清零,继续重复计数。状态方程如图(b).

图 a

图b

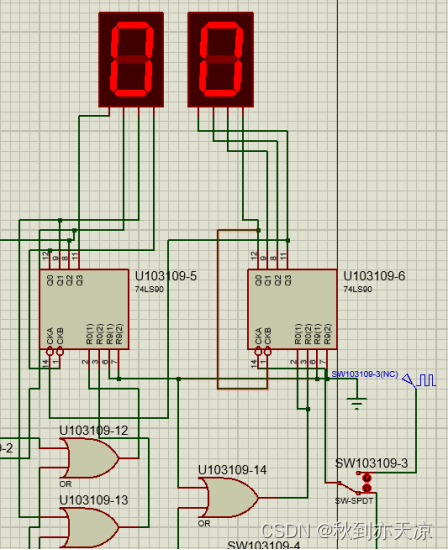

时计数器具体设计方案:

用两片74LS90芯片如图(c),一片控制个位,为十进制;另一片控制十位,为二进制。利用74LS90本身的两控制端完成十进制,在达到1001(即十进制的九)时,给第二个芯片一个脉冲,这样反复,直到第二片达到0010(即十进制的二)且第一片达到0100(即十进制的四)时第一片和第二片同时清零,这样完成一次24的计数,且回到初态,继续重复计数。状态方程如图(d).

图c

图d

7.译码器显示电路

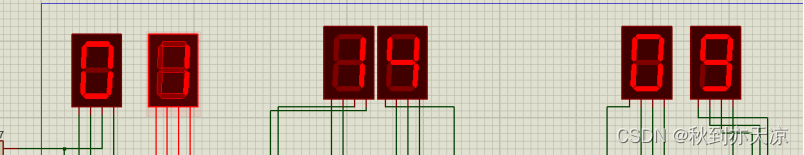

译码显示电路将计数器输出的8421BCD码转换为数码管需要的逻辑状态,并且为保证数码管正常工作提供足够的工作电流,我们采用自带译码功能的数码管,如图(e)。

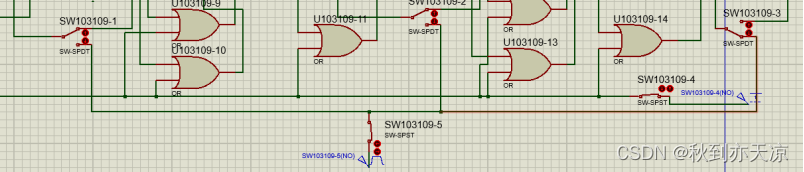

8.校时电路设计

通过三个开关分别控制时、分、秒电路的脉冲输入端CLKA,接收脉冲端CLKA处连接一个双刀开关(SW193109-1,SW130109-2,SW103109-3),如图(f),当开关拨向原本脉冲源则正常工作,当开关拨向校准端则开始校准,校准电路也很简单,使用一个低电平脉冲和一个开关,因为CLKA是低电平有效,所以利用开关(SW103109-5)的断开和闭合来实现不断地给CLKA低电平脉冲从而实现校准功能。

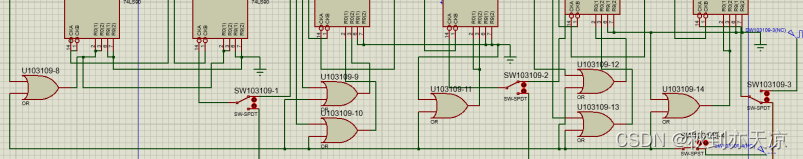

9.整体置零电路设计

如图(g)采用多个或门(U103109-8…U103109-14)的方式从而实现对74LS90芯片的两个置零端(R0,R1)的控制,使用一个连接有高电平的开关(SW103109-4)和所有或门的一个输入口相连从而实现对所有置零端的控制,当开关(SW103109-4)闭合所有R0,R1的状态为”1”,直接置零。

10.整体设计图

2万+

2万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?