FPGA uart串口收发verilog源码程序,适用于RS232 RS422,支持修改波特率,数据位,校验位。

ID:3750670799663712

在逃码农

FPGA (Field-Programmable Gate Array)技术是一种灵活可编程的硬件集成电路技术,具备高度定制化和并行处理能力。在现代通信领域,UART (Universal Asynchronous Receiver/Transmitter)串口是一种广泛应用的数据通信接口,用于在计算机与其他外部设备之间进行数据传输。

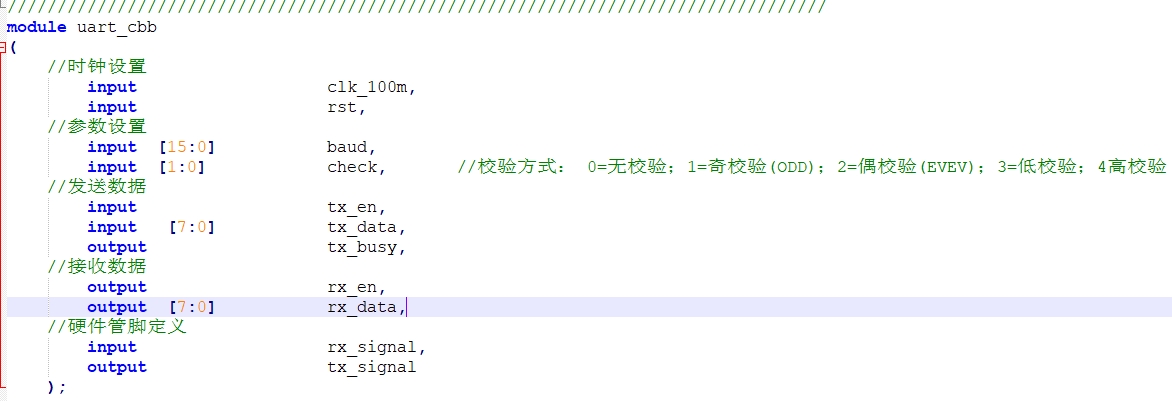

本文将详细介绍一种基于FPGA的UART串口收发Verilog源码程序,该程序适用于RS232和RS422通信标准,并支持动态修改波特率、数据位和校验位等参数。通过使用FPGA技术实现UART串口通信,不仅可以提高通信速度和灵活性,还可以减少硬件成本和板级复杂度。

首先,我们将介绍FPGA的基本原理和特点。FPGA是一种可编程逻辑器件,其主要由数百至数百万个逻辑门和存储单元组成。与传统的固定功能集成电路相比,FPGA可以通过编程在硬件级别上实现逻辑和功能的定制。因此,FPGA具备高度灵活性,可以根据具体需求进行快速设计和修改。同时,FPGA还具备并行处理能力,可以同时执行多个任务,进一步提高系统性能。

接下来,我们将介绍UART串口通信的基本原理和应用场景。UART串口是一种异步串行通信接口,通过发送和接收数据位来进行数据传输。它广泛应用于计算机与外部设备之间的通信,例如串口打印机、调制解调器、传感器和工业自动化设备等。UART串口通信具备简单、易实现和兼容性好的特点,适用于各种场景。

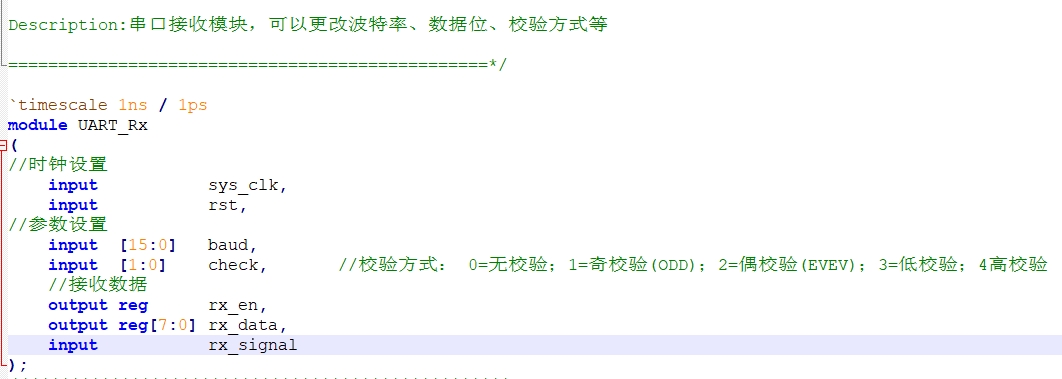

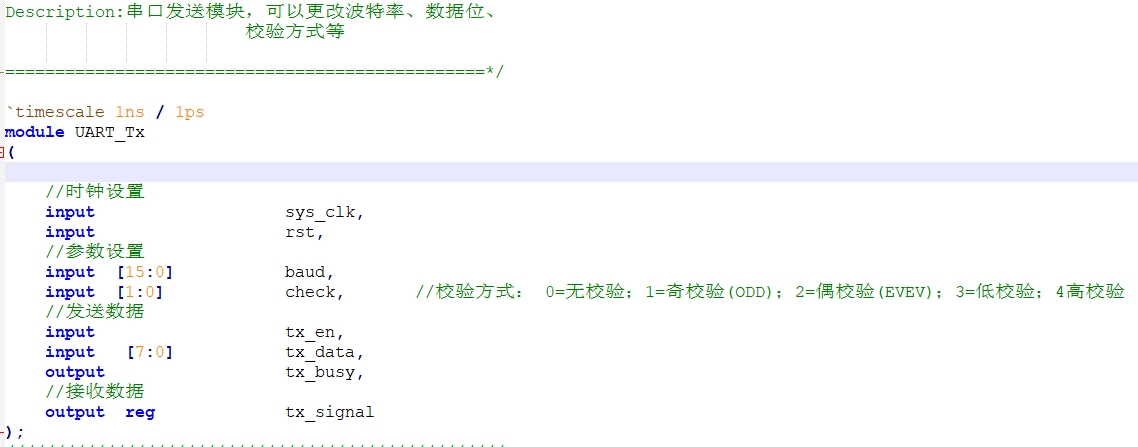

接下来,我们将详细介绍基于FPGA的UART串口收发Verilog源码程序的设计和实现。该程序使用Verilog语言进行描述,并通过FPGA开发工具进行编译和烧录。首先,我们将介绍串口收发的基本流程和控制信号,包括起始位、数据位、停止位和校验位等。然后,我们将给出基于Verilog语言的串口发送和接收模块的设计和实现。

在设计串口发送模块时,我们需要将要发送的数据经过一定的处理,包括添加起始位、数据位和校验位等。然后,通过FPGA的GPIO (General Purpose Input/Output)接口将处理后的数据发送到外部设备。在设计串口接收模块时,我们需要实时监听外部设备的数据,通过FPGA的GPIO接口接收到数据后,进行解码和校验,并将解码后的数据输出到FPGA的其他模块进行后续处理。

最后,我们将介绍程序的调试和验证方法。通过连接FPGA和计算机,我们可以通过终端程序或者串口调试工具来发送和接收数据,并对数据进行验证和调试。通过逐步调试和优化,我们可以确保程序的正确性和可靠性。

综上所述,本文详细介绍了基于FPGA的UART串口收发Verilog源码程序的设计和实现。通过使用FPGA技术可以实现对UART串口通信的灵活定制和高性能处理,提高通信速度和可靠性。该程序适用于RS232和RS422通信标准,并支持动态修改通信参数,满足不同场景的需求。通过本文的介绍和实例,读者可以更好地理解和应用FPGA技术在通信领域的应用,进一步提升工程实践能力和技术水平。

以上相关代码,程序地址:http://matup.cn/670799663712.html

2531

2531

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?