DAC8568 Controller

DAC8568 简介

PIN Description

| Name | Description |

|---|---|

| L D A C ‾ \overline{LDAC} LDAC | load DACs |

| S Y N C ‾ \overline{SYNC} SYNC | 低电平有效,电平触发控制, 该输入为输入数据的帧同步信号. 当SYNC为低,使能DAC内输入移位寄存器,并在随后的所有时钟沿采样数据。 在第32个时钟之后,DAC更新输出。 若不到32个时钟SYNC被置高(即出现SYNC上升沿),那么写序列被忽略。 |

| C L R ‾ \overline{CLR} CLR | 异步复位 |

| D I N D_{IN} DIN | 串行数据输入,数据在串行时钟输入的每个下降沿被同步到 32 位输入移位寄存器 |

| S C L K SCLK SCLK | 串行时钟,最高可达50MHz |

| A V D D AV_{DD} AVDD | 电源输入, 2.7V ~ 5.5V |

Timing Diagram

| 参数 | 最小值(ns) | 说明 |

|---|---|---|

| t1 | 10ns | 为确保成功写入,SCLK 下降沿到SYNC下降沿 |

| t2 | 20ns | SCLK周期 |

| t3 | 13ns | SYNC上升沿到第31个SCLk下降沿的时间差,确保SYNC中断 |

| t4 | 80ns | SYNC高电平最短时间要求 |

| t5 | 13ns | SYNC到SCLK下降沿的建立时间 |

| t6 | 8ns | SCLK低电平时间 |

| t7 | 8ns | SCLK高电平时间 |

| t8 | 10ns | SCLK下降沿到SYNC上升沿时间 |

| t9 | 6ns | 数据建立时间 |

| t10 | 4ns | 数据保持时间 |

| t11 | 40ns | SCLK下降沿到LDAC下降沿时间,异步LDAC更新模式 |

| t12 | 80ns | LDAC低电平脉冲宽度 |

| t13 | 4 × t 1 4\times t_{1} 4×t1 ns | 同步LDAC更新模式,LDAC下降沿到SYNC下降沿时间 |

| t14 | 40ns | 32nd SCLK下降沿到LDAC上升沿时间 |

| t15 | 80ns | CLR低电平脉冲宽度 |

串行接口

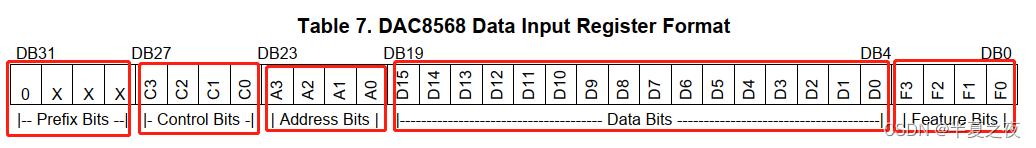

DAC7568、DAC8168 和 DAC8568 输入移位寄存器为 32 位宽:

- 4-bit 前缀位 : DB31 ~ DB28 (最高位必须置零,余下Don’t care)

- 4-bit控制位: DB27 ~ DB24 (控制DAC模式)

- 4-bit 地址位:DB23~ DB20 (选择DAC通道)

- 16-bit数据位:DB19 ~ DB4 (送入DAC DATA Buffer)

- 4-bit特征位: DB3 ~ DB0

当写入 DAC 寄存器(数据传输)时,高位优先(高位先写入),DB[3:0]被 DAC 忽略。 在串行时钟输入 SCLK 的控制下,所有 32 位数据都加载到 DAC 中。

最高位DB31必须一直置’0’且先写入DAC移位寄存器。 SYNC为低开始写操作,在之后的每个SCLK下降沿将DIN(串行数据输入PIN)上的数据写入DAC移位寄存器。

在第32个SCLK下降沿,最后一位输入写入DAC移位寄存器并锁定移位寄存器,后续的时钟不会改变移位寄存器的值。在接收到32-bit数据后,DAC开始对32-bit数据进行译码操作,不用等待SYNC的上升沿。新的写(移位寄存器)操作在下一个SYNC下降沿开始。

第 31 位序列完成之前的 SYNC 上升沿复位 SPI 接口; 不会发生数据传输。

必须满足从第 32 个 SCLK 下降沿到下一个 SYNC 下降沿的最小延迟时间的要求,才能正确地开始下一个周期。

DAC8568支持软件硬件同时更新和控制功能,DAC8568的数据更新可以以异步或者同步的方式。

- 同步模式: 在SYNC下降沿之后的第32个SCLK下降沿更新数据, 此时,LDAC引脚必须接地

- 异步模式:LDAC下降沿作为触发更新DAC, 可将多个通道内的Buffer设置预期值然后送入LDAC下降沿更新DAC的输出寄存器

控制命令

| 操作 | 控制码 | 地址码 | 特征码 |

|---|---|---|---|

| 写入选定的 DAC 输入寄存器 | 4’h0 | 4’b0xxx (0~7 对应 通道A ~ H); 4’b1xxx无效码(4‘b1111除外,此时将写入数据广播至每个通道) | don’t care |

| 更新选择的DAC寄存器 | 4’h1 | 4’b0xxx (0~7 对应 通道A ~ H); 4’b1xxx无效码(4‘b1111除外,此时将写入数据广播至每个通道) | don’t care |

| 写入选定的 DAC 输入寄存器并更新所有 DAC 寄存器 | 4’h2 | 4’b0xxx (0~7 对应 通道A ~ H); 4’b1xxx无效码(4‘b1111除外,此时将写入数据广播至每个通道) | don’t care |

| 写入选定的 DAC 输入寄存器并更新对用的 DAC 寄存器 | 4’h3 | 4’b0xxx (0~7 对应 通道A ~ H); 4’b1xxx无效码(4‘b1111除外,此时将写入数据广播至每个通道) | don’t care |

| Power Down命令 | 4’h4 | DB7 ~ DB0 对应 通道 H ~ A | DB9 ~ DB8 为2‘b00时,通过将对应bit置高上电 … |

| 写入清除代码寄存器 | 4’h5 | don’t care | 4’bxx00(zero scale) , 4’bxx01(midscale), 4’bxx10(full-scale), 4‘bxx11忽略CLR引脚 |

| 写入到LDAC寄存器 | 4’h6 | DB7 ~ DB0 对应 通道 H ~ A | 默认为零,使用LDAC更新数据 |

| 软件复位 | 4’h7 | don’t care | don’t care |

| Internal Reference 命令 | 4’h8 | ||

| Internal Reference 命令 | 4’h9 |

4781

4781

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?