本节我们将揭秘计算机的核心部件:算术和逻辑单元。了解计算机里基础的加法,左移,右移,非,与,或,异或,比较操作是如何被选择和处理的。

算术和逻辑单元

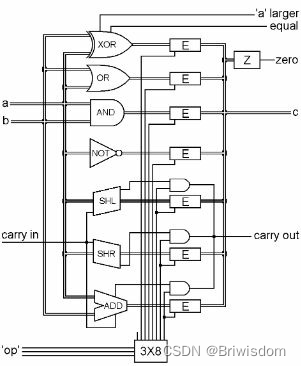

目前,我们已经见到了计算机的其中设备:加法,左移,右移,非,与,或,异或。把它们放在一个单元里,并提供一种方法来选择在任何给定时间使用哪一台设备,这被称为“算术和逻辑单元”,简称“ALU”。

所有七个设备都连接了一个输入“a”,如果设备具有两个输入,那就连接着输入端“b”。所有七个设备都始终连接到输入,但每个设备的输出都连接到其中一个使能器。开启使能器的导线连接到解码器的输出,因此在给定时间只能打开一个使能器。解码器的七个输出使单个设备能够继续使用公共输出“c”。当您根本不想选择任何设备时,将使用解码器的第八个输出。解码器的三条输入线被标记为“op”,因为它们选择了所需的“操作”。

这里的一个小问题是来自加法器的进位,以及来自移位器的“移入”和“移出”位。它们的使用方式非常相似,因此从这里开始,我们将把它们统称为进位。加法器和两个移位器将进位作为输入,并生成进位作为输出。因此,三个进位输入连接到一个ALU输入,三个输出中的一个与器件的总线输出一起被选择。查看上面3X8解码器的最右侧输出,并确认它同时启用加法器总线和加法器进位。

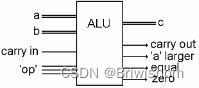

我们这里是有两个总线输入、一个总线输出、四个bit其他输入和四个bit其他输出的盒子。三个输入bit选择在输入和输出总线之间发生的“操作”。下面是一种简化的绘制方法

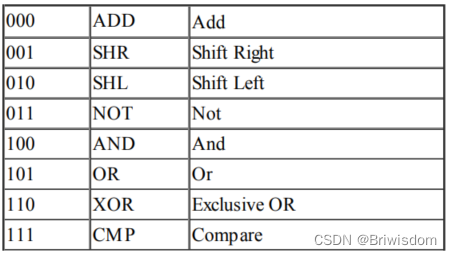

请注意,上面标记为“op”的三个单位输入可以有八种不同的组合。其中七种组合选择了前面描述的设备之一。第八种组合不选择任何输出字节,但“较大”和“相等”位仍然有效,所以第八种组合是比较器的操作。

“op”的位组合意味着什么。这听起来像是另一个代码。是的,这是一个三位代码,我们将很快使用:

算术和逻辑单元是计算机的核心。这就是计算机里所有动作发生的地方。这里面比你想象的要复杂得多。

处理器

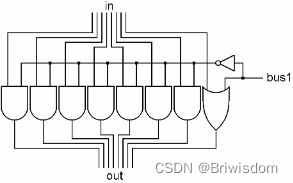

至此,计算机CPU里还有另一个非常简单的装置,它有一个总线输入、一个总线输出和一个其他输入bit。它非常类似于使能器。其中七位通过与门,其中一位通过或门。一个bit的输入决定了当一个字节试图通过这个设备时会发生什么。当“总线1”位关闭时,输入总线的所有位都不变地传递到输出总线。当“总线1”位接通时,输入字节被忽略,输出字节将为0000 0001,这是二进制数字1。我们将此设备称为“总线1”,因为当我们需要时,它会将数字1放在总线上。

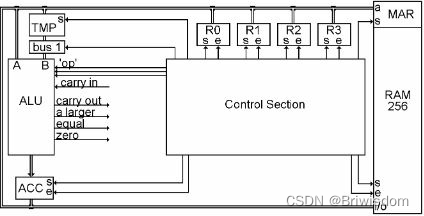

现在我们可以将这个“总线1”和ALU放入CPU。我们将改变导线进出ALU的位置,使其更适合我们的图表。总线输入位于顶部,总线输出位于底部,所有输入和输出bit位于右侧。

ALU的输出连接到ACC。ACC接收并临时存储最近ALU操作的结果。ACC的输出然后连接到总线,因此其内容可以根据需要发送到其他地方。

当我们想进行单输入ALU操作时,我们必须将ALU的三个“运算”位设置为所需的操作,将我们想要的寄存器启用到总线上,并将结果连接到ACC。

对于两个输入ALU操作,有两个步骤。首先,我们在总线上启用其中一个寄存器,并将其设置为TMP。然后,我们在总线上启用第二个寄存器,选择ALU操作,并将答案设置为ACC。

如您所见,如果我们在正确的时间打开和关闭适当的启用和设置位,我们现在可以将字节数据从RAM移动到RAM,从寄存器移动到寄存器,通过ALU移动到ACC,然后从那里移动到寄存器或RAM。这就是电脑内部发生的事情。

这里只缺少一件事,这与寄存器、ALU和RAM上的所有这些控制位有关。RAM有三个控制位,一个用于设置MAR,一个设置当前选择的字节,一个启用当前选择的输出。寄存器R0、R1、R2、R3和ACC中的每一个都有一个置位和一个使能位,TMP仅有一个设置位,总线1有一个控制位,ALU有三个选择所需操作的“操作”位。

我们需要在适当的时间打开和关闭所有这些控制位的东西,这样我们才能做一些有用的事情。标有“控制部分”的框将在接下来开始揭秘。

1729

1729

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?