本文档原版RTF文件、例程下载: http://pan.baidu.com/s/1mg88Gdi

0. 索引

1. 前言

2. 效果预览

3. 代码展示

4. 具体步骤

5. 后言

6. 附录

前言

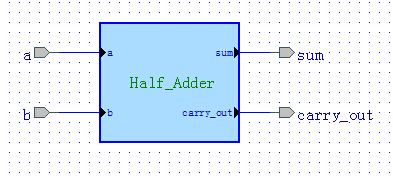

最近对VHDL产生了兴趣并开始学习,走了很多弯路,百度一下,资料太少,把上机的一些经历写出来,也好方便别人。使用工具:Active-HDL 7.2SE. 被模拟的半加器(2个二进制位相加,分别输出和、进位)引脚图:

效果预览

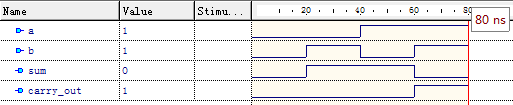

波形图(Waveform)

代码展示

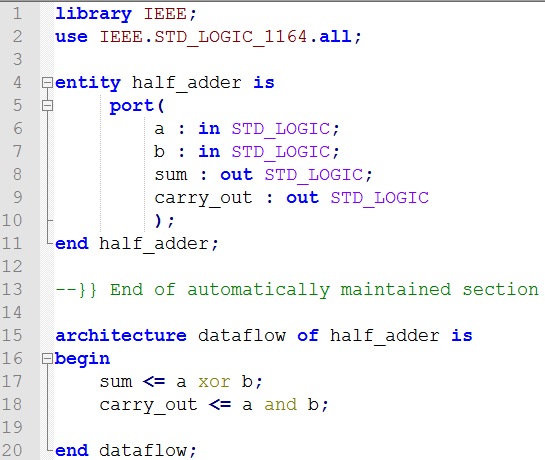

half_adder.vhd

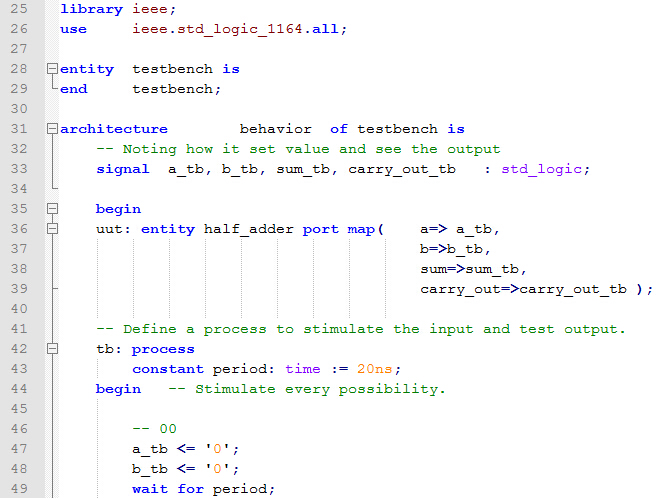

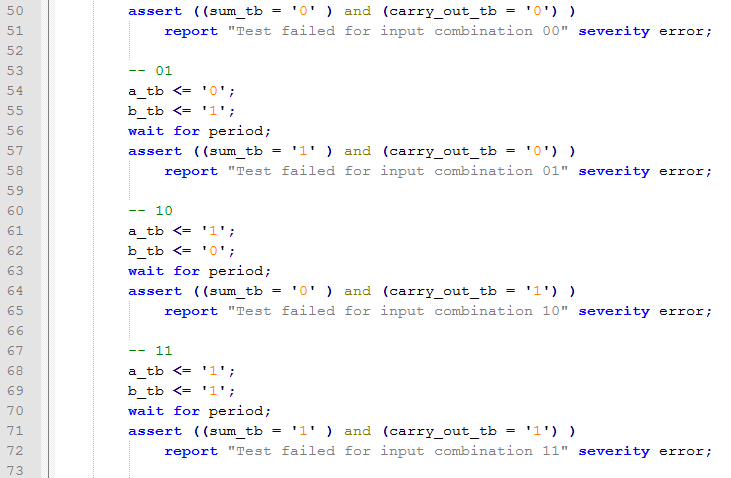

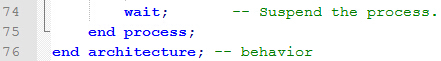

testbench.vhd

具体步骤

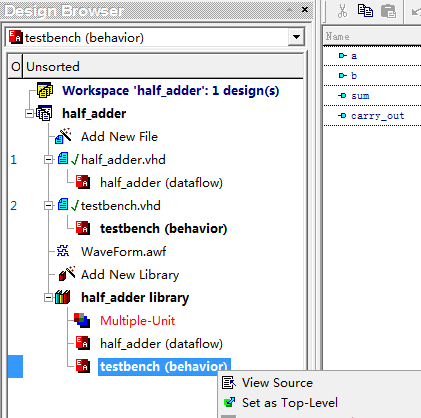

第一步,在Design Browser的Files选项卡内testbench.vhd下testbench(behavior)打开右键菜单,“Set as Top-Level”,这一步很重要,否则会出现如下提示

# KERNEL: Simulation has finished. There are no more test vectors to simulate.

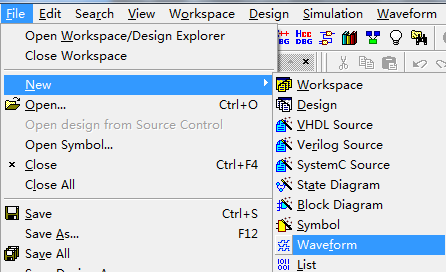

第二步,创建Waveform

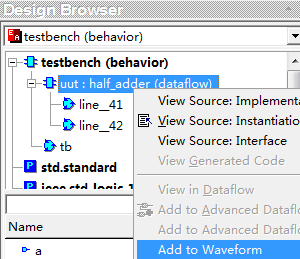

第三步,Add to Waveform

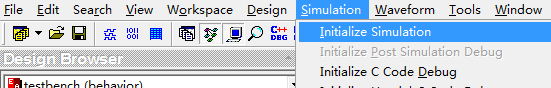

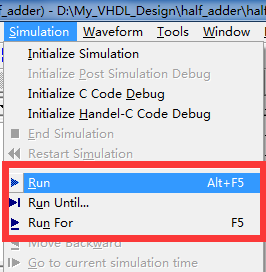

第五步,Run!!!

第六步,获得方波图形

后记

后言

本文档是我在接触Active-HDL这个上上机工具1天内写出来的,意在记录从VHDL源程序、测试平台代码到仿真输出方波的过程、注意事项,难免有些简单、肤浅。

请高手勿拍砖,直接忽视这篇小儿科文档;

也希望热心的前辈多多批评指教,让本篇文档,更加完善从而帮助更多人;

也希望众多像我这样痴迷于VHDL的朋友们能互相交流经验,共同进步!

Mighten Dai

May 2, 2015

附录:

(Active-HDL官方帮助文档节选)

VHDL Testbench Tutorial

Introduction

The purpose of this advanced testbench tutorial is to acquaint you with methods of automatic generation of WAVES-based testbenches. The basic testbench tutorial, which you are assumed to have already gone through, deals with the single process testbenches. A single process testbench can only drive input ports of the UUT entity while the WAVES-based testbench simultaneously drives the inputs and compares the output response with a previously saved pattern. Test vectors used to stimulate the UUT entity are furnished in an external file (*.VEC) based on a text format specified by the WAVES standard. Additional procedures compare output signals of the UUT entity with the pattern vectors. Discrepancies are reported in a log file. The Test Bench Wizard generates the test vector file (*.VEC) from a waveform file (*.AWF) created with Waveform Editor. It also verifies if port names of the UUT entity agree with the signal names saved in the waveform file.

Once the user has generated a testbench and prepared specification of test vectors, the testbench can be used many times to perform automatic verification of successive revisions of a VHDL design. Moreover, the same testbench can be used with different test vector files, provided that they define timings of the same signals. The wizard is not the only tool that generates test vector files in the WAVES format. Active-HDL provides the Export Waveform command that can be used to convert waveform files (*.AWF) to WAVES format test vector files(*.VEC).

Creating New Design

In the tutorial, you will create a simple design. To save time, you will reuse VHDL code from the Loadable_counter sample design, shipped with Active-HDL.

1. Start Active-HDL. If the Getting Started dialog opens, click Cancel.

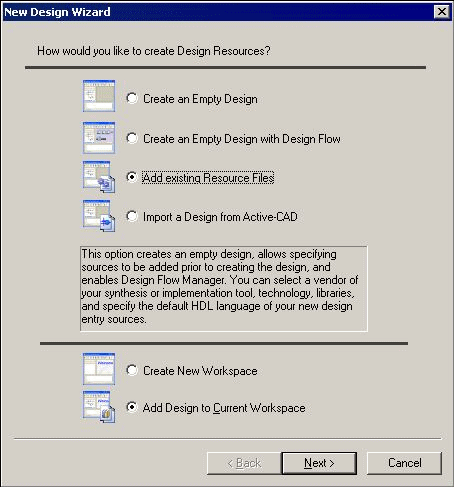

2. Choose New | Design from the File menu. The New Design Wizard will open.

3. In the first wizard dialog, select the Add existing resource files option, and then click Next. You will use an existing VHDL source file from the Loadable_counter sample design.

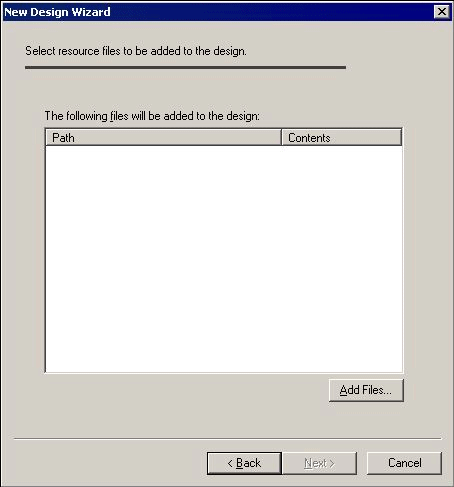

4. In the next wizard dialog, click the Add files button to open the Add Files to Design dialog box.

5. In the Add Files to De

本文档介绍了如何使用VHDL和Active-HDL进行半加器的设计与仿真,包括创建设计、生成测试平台、运行仿真等步骤,并详细讲解了在测试过程中遇到的问题及解决方案,旨在帮助初学者掌握VHDL上机操作。

本文档介绍了如何使用VHDL和Active-HDL进行半加器的设计与仿真,包括创建设计、生成测试平台、运行仿真等步骤,并详细讲解了在测试过程中遇到的问题及解决方案,旨在帮助初学者掌握VHDL上机操作。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

5333

5333

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?