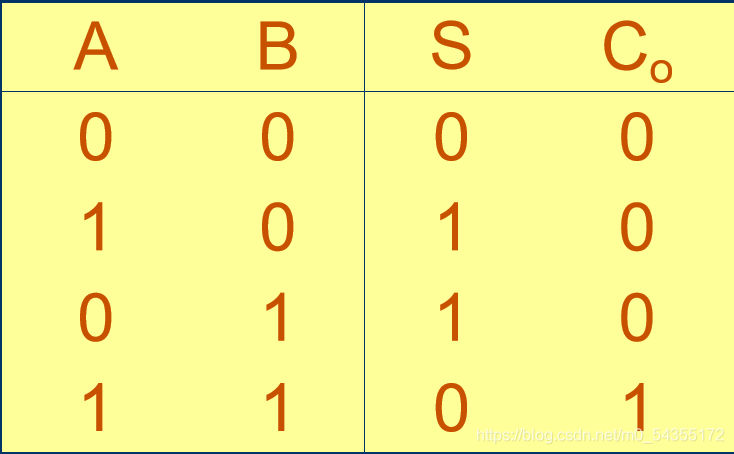

1.真值表

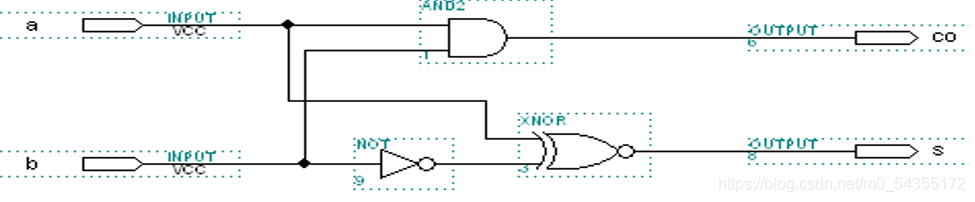

2.逻辑电路

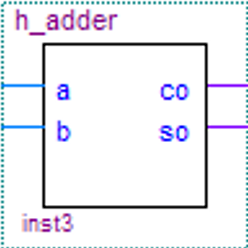

3.端口

4.VHDL语言

4.1.表达1:

library ieee;

use ieee.std_logic_1164.all;

entity h_adder is

port (a,b:in STD_LOGIC;

co,so:out STD_LOGIC);

end h_adder;

architecture fh of h_adder is

signal sel:STD_LOGIC_VECTOR(1 downto 0);

begin

sel <= a&b;

process(sel)

begin

case sel is

when "00"=>so<='0';co<='0';

when "01"=>so<='1';co<='0';

when "10"=>so<='1';co<='0';

when "11"=>so<='0';co<='1';

when others=>null;

end case;

end process;

end fh;

4.2表达2:

library ieee;

use ieee.std_logic_1164.all;

entity h_adder is

port (a,b:in STD_LOGIC;

co,so:out STD_LOGIC);

end h_adder;

architecture fh of h_adder is

begin

so <= not(a xor (not b));

co <= a and b;

end fh;

5224

5224

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?