硬件体系(3个部分):LCD液晶 屏、LCD驱动芯片、LCD控制器( 集成在ARM芯片内部)

控制器---通过驱动芯片---控制液晶屏

液晶屏种类:STN\GF\TFT;TFT 在嵌入式中较为常用

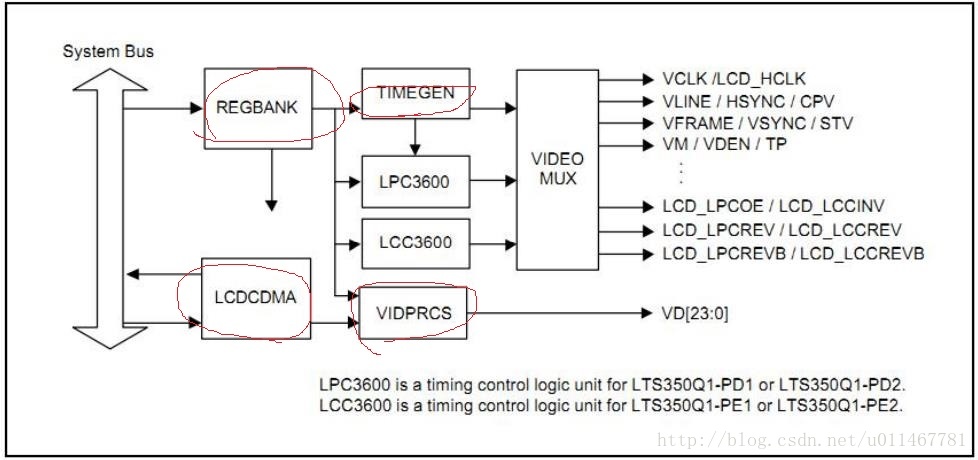

LCD控制器结构与模块:

1.

REGBANK: 由17个可编程的寄存器组和一块256*16的调色板内 存组成,通过这些寄存器,可以配置LCD控制器.

2. LCDCDMA: 一个专用的DMA,它能自 动地把在帧内 存中的视频数据传送到LCD驱动器,通过使用 这个DMA通道, 视频数据在不需要CPU的干预的情况下显示在LCD屏上.

2. LCDCDMA: 一个专用的DMA,它能自 动地把在帧内 存中的视频数据传送到LCD驱动器,通过使用 这个DMA通道, 视频数据在不需要CPU的干预的情况下显示在LCD屏上.

3. VIDPRCS: 接收来自 LCDCDMA的数据, 将数据转换为合适的数据格式, 比如说4/8位单扫, 4位双扫显示模式, 然后通过数据端口 VD[23:0]传送视频数据到LCD驱动器;

4.TIMEGEN: 由可编程的逻辑组成, 他生成LCD驱动器需要的控制信号, 比如VSYNC、 HSYNC、 VCLK和LEND等, 而这些控制信号又与 REGBANK寄存器组中的配置密切相关,通过不同 的配置, TIMEGEN就能产生这些信号的不同值, 从而支持不同 的LCD驱动器(即不同 的STN/TFT屏)。

显示过程

4.TIMEGEN: 由可编程的逻辑组成, 他生成LCD驱动器需要的控制信号, 比如VSYNC、 HSYNC、 VCLK和LEND等, 而这些控制信号又与 REGBANK寄存器组中的配置密切相关,通过不同 的配置, TIMEGEN就能产生这些信号的不同值, 从而支持不同 的LCD驱动器(即不同 的STN/TFT屏)。

显示过程

1. 显示从屏幕左上角第一行的第一个点开始, 一个点一个点地在LCD上显示, 当 显示到屏幕的最右边就结束这一行(Line)。

2. 接下来显示指针又回到屏幕的左边从第二行开始 显示,显示指针在从第一行的右边回到第二行的左边是需要一定的时间的, 我们称之为行切换。

3. 以此类推,显示指针就这样一行一行的显示至矩形的右下角 才把一幅图像(帧: frame)显示完成。

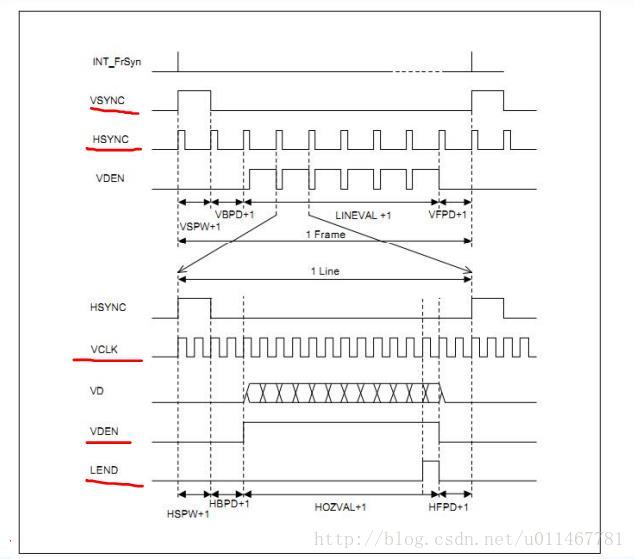

时序信号

•VSYNC:垂直同步信号 •HSYNC: 水平同步信号 •VCLK: 象素时钟信号

•VD[23:0]: LCD像素数据输出 端口 • VDEN: 数据使能信号 •LEND:行结束信号

![]()

2. 接下来显示指针又回到屏幕的左边从第二行开始 显示,显示指针在从第一行的右边回到第二行的左边是需要一定的时间的, 我们称之为行切换。

3. 以此类推,显示指针就这样一行一行的显示至矩形的右下角 才把一幅图像(帧: frame)显示完成。

时序信号

•VSYNC:垂直同步信号 •HSYNC: 水平同步信号 •VCLK: 象素时钟信号

•VD[23:0]: LCD像素数据输出 端口 • VDEN: 数据使能信号 •LEND:行结束信号

显示过程与时序

1. 显示从屏幕左上角第一行的第一个点开始,一个点一个点地在LCD上显示, 点与点之间 的时间间隔为 VCLK(

像素时钟信号) ;

当 显示到屏幕的最右边就结束这一行(Line), 这一行的显示对应时序图上的HSYNC( 水平同步信号)

2. 接下来显示指针又回到屏幕的左边从第二行开始显示, 显示指针在从第一行的右边回到第二行的左边是需要一定的时间的, 我们称之为行切换。

3. 以此类推,显示指针就这样一行一行的显示至矩形的右下角才把一幅图像(帧: frame)显示完成, 这一帧的显示时间 在时序图上表示为 VSYNC( 垂直同步信号) 。

当 显示到屏幕的最右边就结束这一行(Line), 这一行的显示对应时序图上的HSYNC( 水平同步信号)

2. 接下来显示指针又回到屏幕的左边从第二行开始显示, 显示指针在从第一行的右边回到第二行的左边是需要一定的时间的, 我们称之为行切换。

3. 以此类推,显示指针就这样一行一行的显示至矩形的右下角才把一幅图像(帧: frame)显示完成, 这一帧的显示时间 在时序图上表示为 VSYNC( 垂直同步信号) 。

5万+

5万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?