Vim 中如何去掉 ^M 字符?

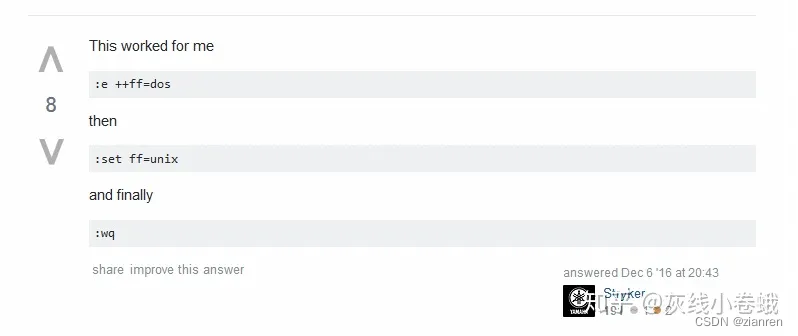

基于 DOS/Windows 的文本文件在每一行末尾有一个 CR(回车)和 LF(换行),而 UNIX 文本只有一个换行,即win每行结尾为\r\n,而linux只有一个\n如果win下的文档上传到linux,每行的结尾都会出现一个^M,(^M是ctrl+v,ctrl+m) 如果是单个文档的话,可以用vi打开,执行 :%s/^M//g 来去掉^M,但如里批量去除的话就不能用vi了,

方法1: 用dos2unix工具,把win文档转换成linux下文档命令:find ./ -type f -print0 | xargs -0 dos2unix如果想把linux下的文档转换成win下的:find ./ -type f -print0 | xargs -0 unix2dos

方法2: 用sed命令把win文档转换成linux下文档:find ./ -type f print0 | xargs -0 sed -i 's/^M$//'把linux下的文档转换成win下的fild ./ -type f print0 | xargs -0 sed -i 's/$/^M/'

链接:https://www.zhihu.com/question/22130727/answer/33814375

void‘($cast(env, p_sequencer.m_parent));

void'($cast(env, p_sequencer.m_parent)); 在UVM和SystemVerilog的上下文中看起来是一个尝试强制类型转换的操作。

这里简要解释一下你给出的代码:

-

$cast: 这是一个SystemVerilog的系统函数,用于尝试将一个类的对象强制转换为另一个类的类型。 -

env: 这应该是你想要转换到的目标类型的一个变量或者对象。 -

p_sequencer.m_parent: 这应该是你想要从中进行类型转换的源对象。在UVM中,p_sequencer可能是一个与sequence相关的sequencer,而m_parent则是它的父对象。 -

void'(...): 这个是一个特殊的语法,通常用于在SystemVerilog中消除未使用的返回值导致的警告。$cast函数返回一个boolean值,表示转换是否成功。如果你不关心这个返回值,并且想要避免任何关于未使用的返回值的警告,你可以使用void'来丢弃这个返回值。

所以,你的代码尝试将p_sequencer.m_parent转换为env的类型,并且丢弃了转换是否成功的结果。

为了确保代码的正确性,你应确保以下几点:

env已经被正确地声明并且是你期望的目标类型。p_sequencer.m_parent确实是一个可以被转换为env类型的对象。- 如果你关心转换是否成功,应该处理

$cast的返回值,而不是使用void'来丢弃它。

Virtual Sequence & Virtual Sequencer

https://zhuanlan.zhihu.com/p/369681031#%E4%BB%80%E4%B9%88%E6%97%B6%E5%80%99%E9%9C%80%E8%A6%81%E4%B8%80%E4%B8%AAvirtual%20Sequencer%EF%BC%9F

?

1

extern virtual function void configure_complex_agent(complex_agent_config cfg)

function void tesr_base::configure_complex_agent(complex_agent_config cfg);

agt_cfg.active = UVM_ACTIVE;

set 与 get 函数的参数

1.写信

1)第一个和第二个参数联合起来组成目标路径,与此路径符合的目标才能收信。

2)第一个参数必须为uvm_component 的实例的指针。

3)第二个参数是相对于此实例的路径。

2.收信

1)第一个参数必须为uvm_component 的实例的指针。

2)第二个参数是相对于此实例的路径。如果第一个设置为 this,第二个可以是空的字符串。

3)第三个参数必须和set中的严格一样。

3.在top_tb 中,set virtual interface 的第一个参数是null。UVM会自动把它替换成uvm_root::get(),即uvm_top。(uvm_root是全局的,get是静态的)

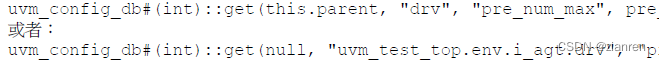

4.既然是第一个和第二个参数联合起来的,set 也可以是下面:

5 get也可以这样,比如driver的build_phase:

https://blog.csdn.net/tingtang13/article/details/46458869

uvm_info

uvm_info 是 UVM(Universal Verification Methodology)中的一个宏,用于在测试过程中输出信息级别的日志。这个宏的语法是:

systemverilog

`uvm_info(tag, message, verbosity)

其中:

tag:是一个字符串,用于标识日志的来源或分类。通常会传递当前执行代码的上下文信息,如方法名、模块名等。

message:是一个字符串,表示要输出的消息内容,用于描述操作或状态。

verbosity:是一个表示日志详细程度的枚举值,用于控制日志的显示级别。UVM 提供了不同的 verbosity 级别,如 UVM_NONE、UVM_LOW、UVM_MEDIUM、UVM_HIGH 等。

`uvm_info("TEST123", $sformatf("get configure random_total %d", cfg.total_random), UVM_LOW)

uvm_info:这是一个 UVM 宏,用于输出信息级别的日志。

“TEST123”:这是日志的标签(tag),表示日志的来源或分类。

$sformatf(“get configure random_total %d”, cfg.total_random):这是通过 $sformatf 函数将字符串和变量格式化为一个字符串。在这里,它会格式化成类似于 “get configure random_total 10” 的消息,其中 10 是 cfg.total_random 的值。

UVM_LOW:这是日志的详细程度(verbosity)。在这个示例中,使用了 UVM_LOW,表示这是一个低级别的信息日志。

总之,这段代码的作用是在 UVM 中输出一个信息级别的日志,标签为 “TEST123”,消息为 “get configure random_total” 以及 cfg.total_random 的值,日志的详细程度设置为低级别。这样的日志输出可以帮助测试工程师在调试和分析测试时了解特定配置信息的状态。

uvm_report_objection report = this;

在 UVM(Universal Verification Methodology)中,您提供的代码片段中涉及了一些 UVM 相关的概念和语法。我将逐个解释每个部分的含义:

-

bit manage_objection = 1;:

- 这行代码声明了一个名为

manage_objection的位变量,并将其初始化为 1。 - 这个变量可能会用来控制是否启用 UVM 的报告异议管理(objection management)功能。

- 这行代码声明了一个名为

-

uvm_report_objection report = this;:

- 这行代码声明了一个名为

report的 UVM 报告异议(objection)对象,并将其初始化为this。 - 在 UVM 中,报告异议是一种机制,用于收集和管理报告的信息,可以用于控制消息的显示和统计。

- 这行代码声明了一个名为

-

protected bit isrunning;:

- 这行代码声明了一个名为

isrunning的受保护(protected)位变量。 - 受保护成员只能在同一个类或类的派生类中访问。

- 这个变量可能用于跟踪某个过程或功能是否正在运行。

- 这行代码声明了一个名为

8486

8486

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?