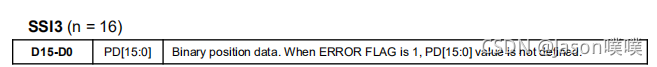

SSI(Synchronous Serial Interface,同步串行接口)是一个全双工的串行接口,允许芯片与多种串行设备通信。它是高精度绝对编码器种一种比较常见的接口方式,采用主机主动式读出方式,即在主控者发出的时钟脉冲的控制下,从最高有效位(MSB)开始同步传输数据。下面以SSI3为例,具体讲解它的接口实现方式。

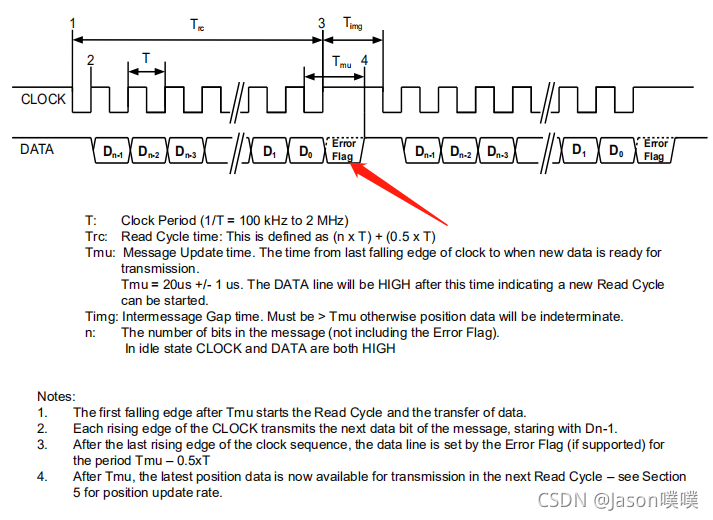

时序图

注意事项

1、时钟频率:100kHz至2MHz,这里取1MHz,就是1T=1us.

2、数据发送阶段:Trc=(16+0.5)us(SSI3数据位是16位)

3、Tmu(数据更新待阶段)=20us+/-1us;

4、Timg(数据等待阶段)必须要大于Tmu(数据更新阶段),为了保证满足时序要求,这里Timg只要大于21us即可;

5、一个完整工作周期=Trc(数据发送阶段)+Timg(数据等待阶段)=(16+0.5+21)us,也就是一个完整工作周期至少要>37.5us,这里为了保证满足时序需求,取到40us。

6、当检测到Error为0(可靠数据),将数据发送阶段的16bit数据保存输出即可。

例如:频率是56MHz,周期是1/56M是17.8ns,8个时钟,数据是32bit,总的时钟是32*8为256,接收32bit需要256个时钟,考虑到单稳态,再加24个时钟,也就是需要280个时钟接收32bit,速率是56M/280为0.2,即200KHz

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?