STM32中断配置示例:

/* NVIC config */

void NVIC_config(void)

{

NVIC_InitTypeDef NVIC_InitStructure;

NVIC_PriorityGroupConfig(NVIC_PriorityGroup_1);

NVIC_InitStructure.NVIC_IRQChannelPreemptionPriority = 1;

NVIC_InitStructure.NVIC_IRQChannel = USART2_IRQn;

NVIC_InitStructure.NVIC_IRQChannelSubPriority = 2;

NVIC_InitStructure.NVIC_IRQChannelCmd = ENABLE;

NVIC_Init(&NVIC_InitStructure);

}

这里涉及异常(中断)相关的:

1、异常与中断

2、优先级分组,NVIC_PriorityGroupConfig

3、抢占优先级,NVIC_IRQChannelPreemptionPriority

4、子(亚)优先级,NVIC_IRQChannelSubPriority

5、中断号定义,NVIC_IRQChannel

6、优先级配置的寄存器实现,NVIC_Init()的实现

此篇对上述内容进行整理,以下内容参考资料《Cortex-M3权威指南》

一、Cortex-M3异常简介

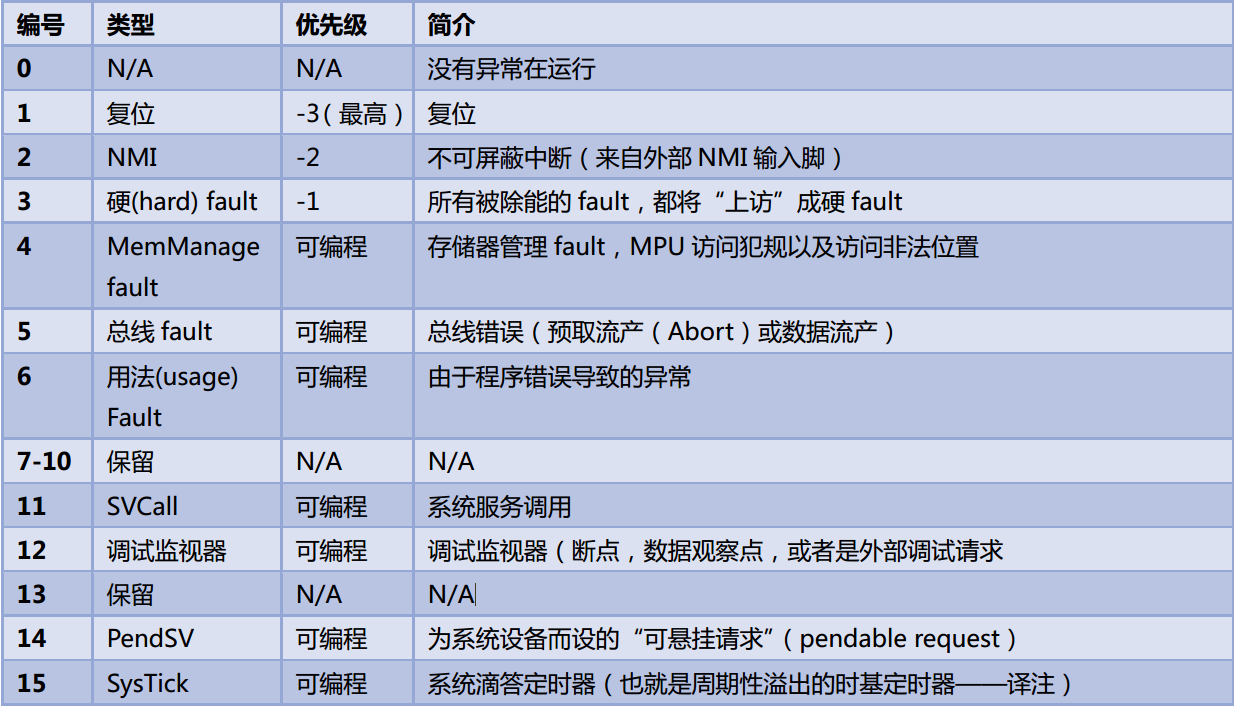

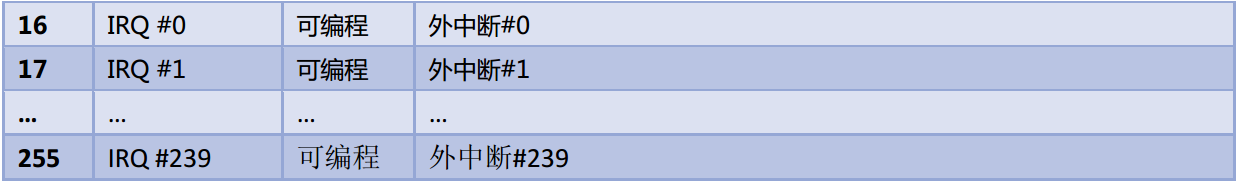

CM3 在内核水平上搭载了一个异常响应系统,所有中断机制都由NVIC实现。CM3有256个预定义的异常(所有能打断正常执行流的事件都称为异常)类型 , 其中编号为 1 - 15 的对应系统异常,大于等于 16 的则全是外部中断。如下图示:

虽然CM3 是支持240 个外中断的,但具体使用了多少个是由芯片生产商决定。比如:STM32 有84 个中断,包括16 个内核中断和68 个可屏蔽中断。不同系列支持的中断数也是不同的,需参考具体芯片datasheet。

这篇博客详细介绍了Cortex-M3处理器的异常概念,包括异常优先级、优先级分组,特别是抢占优先级和子优先级的设置。接着,文章深入探讨了STM32中断系统的中断寄存器组,并通过实例分析了STM32如何实现中断处理。

这篇博客详细介绍了Cortex-M3处理器的异常概念,包括异常优先级、优先级分组,特别是抢占优先级和子优先级的设置。接着,文章深入探讨了STM32中断系统的中断寄存器组,并通过实例分析了STM32如何实现中断处理。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?