ARMv8 TTBRx寄存器

1 TTBR0_ELx and TTBR1_ELx

Selection between TTBR0_ELx and TTBR1_ELx when two VA ranges are supported.

支持两个 VA 范围时,在 TTBR0_ELx 和 TTBR1_ELx 之间进行选择。

Every translation table walk starts by accessing the translation table addressed by the TTBR_ELx for the stage 1 translation for the required translation regime.

每个转换表遍历都从访问由 TTBR_ELx 寻址的转换表开始,以实现所需转换机制的第 1 阶段转换。

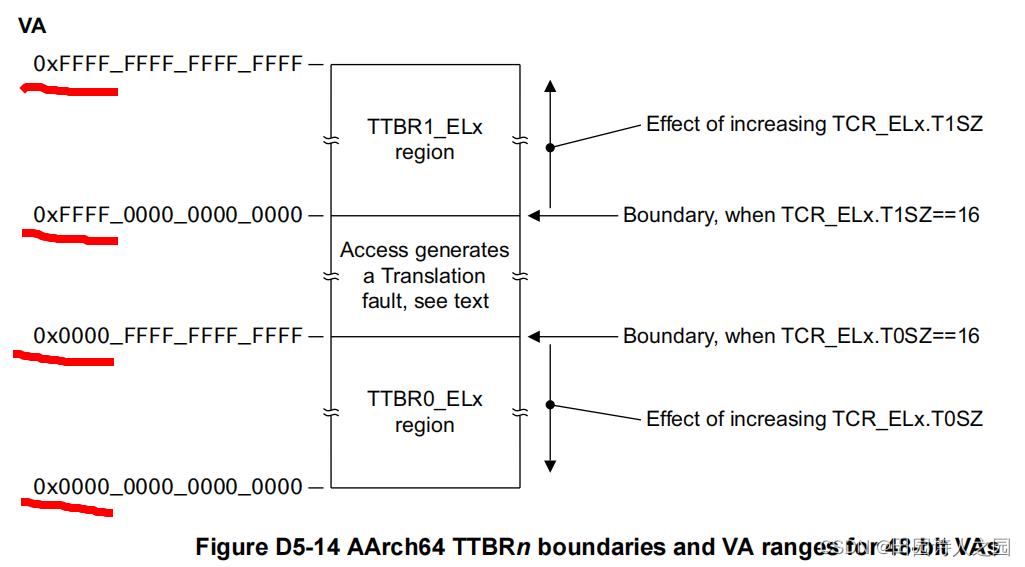

For a stage 1 translation that can support two VA ranges, Figure D5-14 shows this VA range split when using 48-bit

VAs, and:

对于可支持两个 VA 范围的第 1 阶段转换,图 D5-14 显示了在使用 48 位 VA 时的 VA 范围划分。

- TTBR0_ELx points to the initial translation table for the lower VA range, that starts at address 0x0000000000000000

- TTBR0_ELx 指向从地址 0x0000000000000000 开始的低 VA 范围的初始转换表

- TTBR1_ELx points to the initial translation table for the upper VA range, that runs up to address 0xFFFFFFFFFFFFFFFF.

- TTBR1_ELx 指向 VA 上限值范围的初始转换表,该表最高可达地址 0xFFFFFFFFFFFFFFFF。

As Figure D5-14 shows, for 48-bit VAs: - The address range translated using TTBR0_ELx is 0x0000000000000000 to 0x0000FFFFFFFFFFFF.

- 使用 TTBR0_ELx 转换的地址范围为 0x000000000000 至 0x0000FFFFFFFF。

- The address range translated using TTBR1_ELx is 0xFFFF000000000000 to 0xFFFFFFFFFFFFFFFF.

- 使用 TTBR1_ELx 转换的地址范围为 0xFFFF000000000000 至 0xFFFFFFFFFFFFFFFF。

Which TTBR_ELx is used depends only on the VA presented for translation. The most significant bits of the VA must all be the same value and:

使用哪个 TTBR_ELx 仅取决于所提供的 VA 是否需要转换。VA 的最高有效位必须全部为相同的值,并且: - If the most significant bits of the VA are zero, then TTBR0_ELx is used.

- 如果 VA 的最有效位为零,则使用 TTBR0_ELx。

- If the most significant bits of the VA are one, then TTBR1_ELx is used.

- 如果 VA 的最有效位为 1,则使用 TTBR1_ELx。

2 TTBR0_ELx

2.1 TTBR0_EL1

TTBR0_EL1, Translation Table Base Register 0 (EL1)

The TTBR0_EL1 characteristics are:

Purpose

Holds the base address of the translation table for the initial lookup for stage 1 of the translation of an address from the lower VA range in the EL1&0 translation regime, and other information for this translation regime.

保存转换表的基地址,用于在 EL1&0 转换机制中从较低 VA 范围转换地址的第 1 阶段初始查找,以及该转换机制的其他信息。

Configurations

AArch64 System register TTBR0_EL1[63:0] is architecturally mapped to AArch32 System register TTBR0[63:0].

AArch64 系统寄存器 TTBR0_EL1[63:0]在架构上映射到 AArch32 系统寄存器

Attributes

TTBR0_EL1 is a 64-bit register.

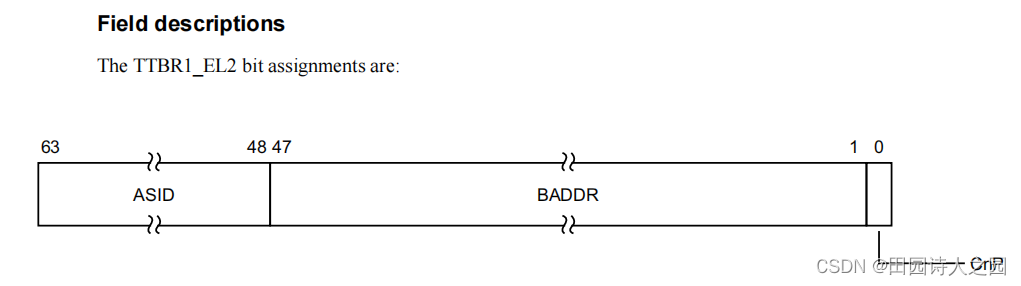

Field descriptions

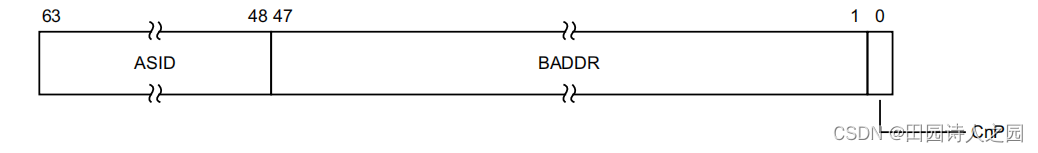

The TTBR0_EL1 bit assignments are:

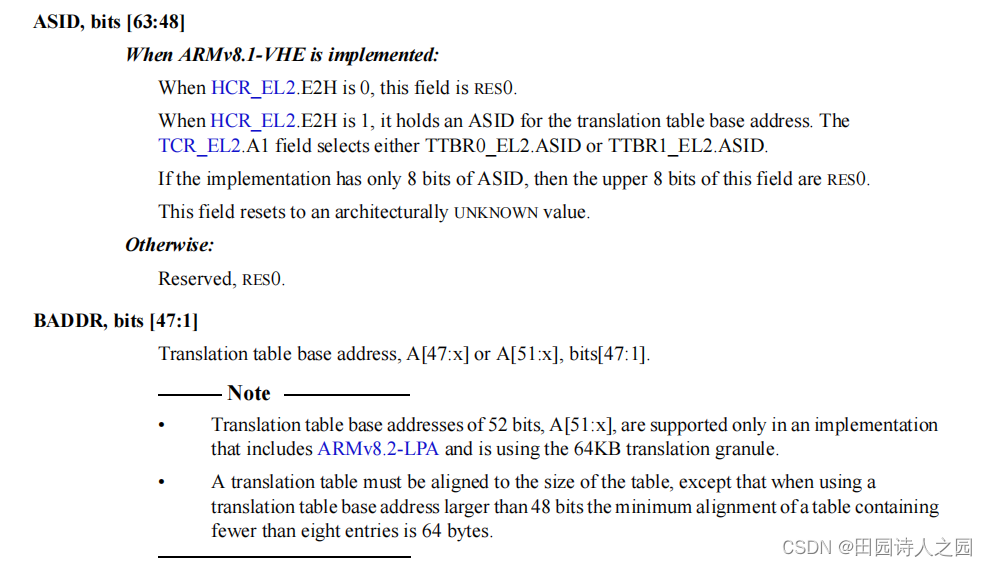

ASID, bits [63:48]

An ASID for the translation table base address. The TCR_EL1.A1 field selects either TTBR0_EL1.ASID or TTBR1_EL1.ASID.

翻译表基址的 ASID。TCR_EL1.A1 字段选择 TTBR0_EL1.ASID 或 TTBR1_EL1.ASID。

If the implementation has only 8 bits of ASID, then the upper 8 bits of this field are RES0.

如果实现只有 8 位 ASID,则该字段的高 8 位为 RES0。

This field resets to an architecturally UNKNOWN value.

该字段重置为一个架构上未知的值。

BADDR, bits [47:1]

Translation table base address, A[47:x] or A[51:x], bits[47:1].

转换表基址,A[47:x] 或 A[51:x],位 [47:1]。

Note:

- Translation table base addresses of 52 bits, A[51:x], are supported only in an implementation that includes ARMv8.2-LPA and is using the 64KB translation granule.

- 只有在包含 ARMv8.2-LPA 并使用 64KB 转换粒度的实施中,才支持 52 位的转换表基址 A[51:x]。

- A translation table must be aligned to the size of the table, except that when using a translation table base address larger than 48 bits the minimum alignment of a table containing fewer than eight entries is 64 bytes.

- 翻译表必须根据表的大小对齐,但当使用的翻译表基址大于 48 位时,包含少于 8 个条目的翻译表的最小对齐方式为 64 字节。

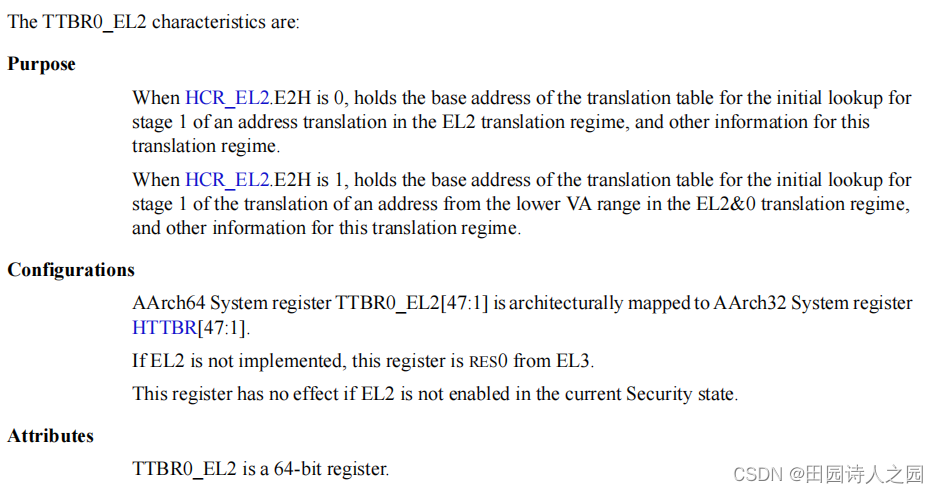

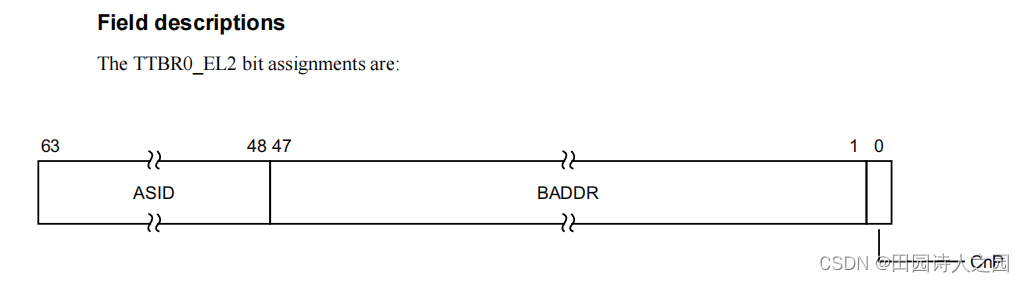

2.2 TTBR0_EL2

TTBR0_EL2, Translation Table Base Register 0 (EL2)

A translation table must be aligned to the size of the table, except that when using a translation table base address larger than 48 bits the minimum alignment of a table containing fewer than eight entries is 64 bytes.

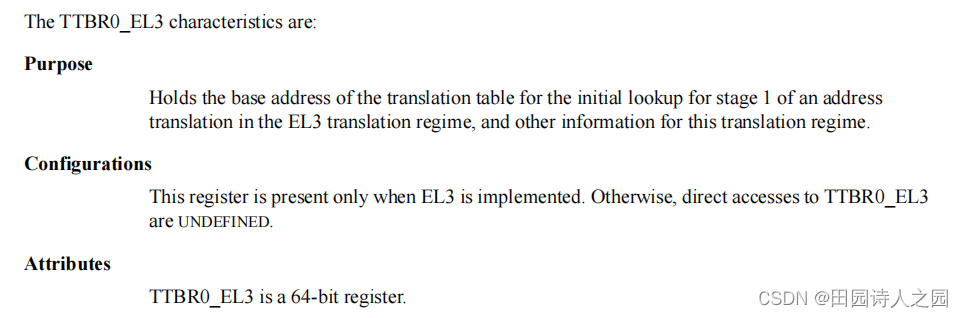

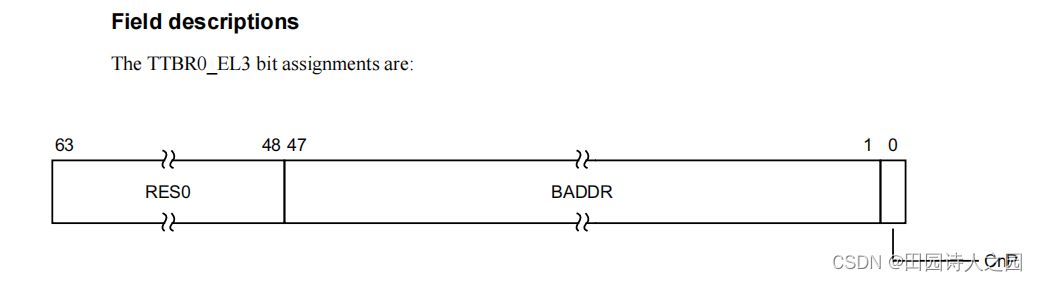

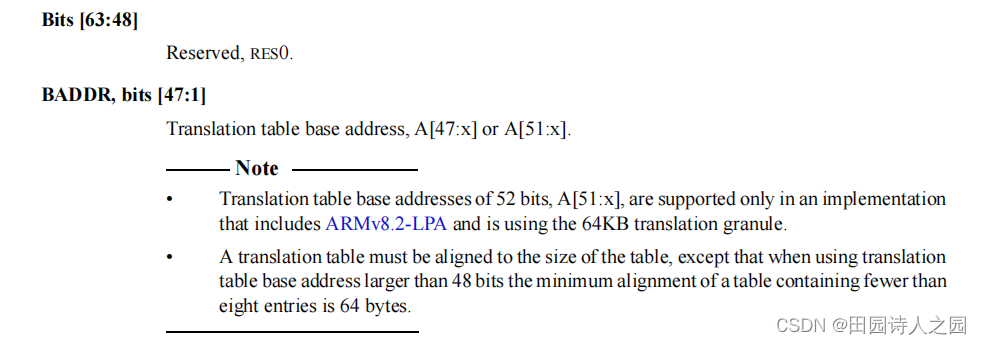

2.3 TTBR0_EL3

TTBR0_EL3, Translation Table Base Register 0 (EL3)

3 TTBR1

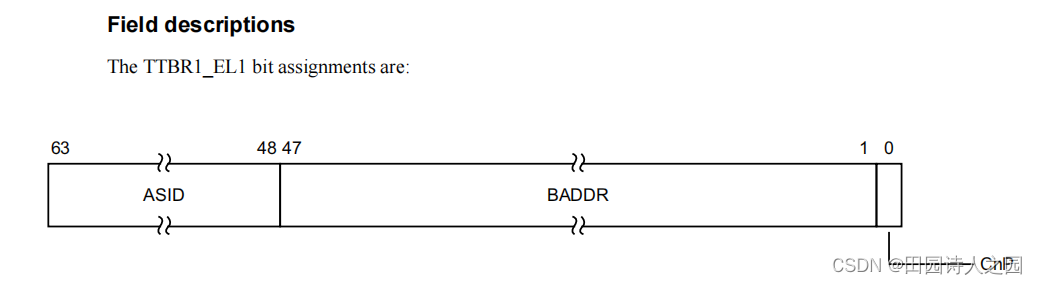

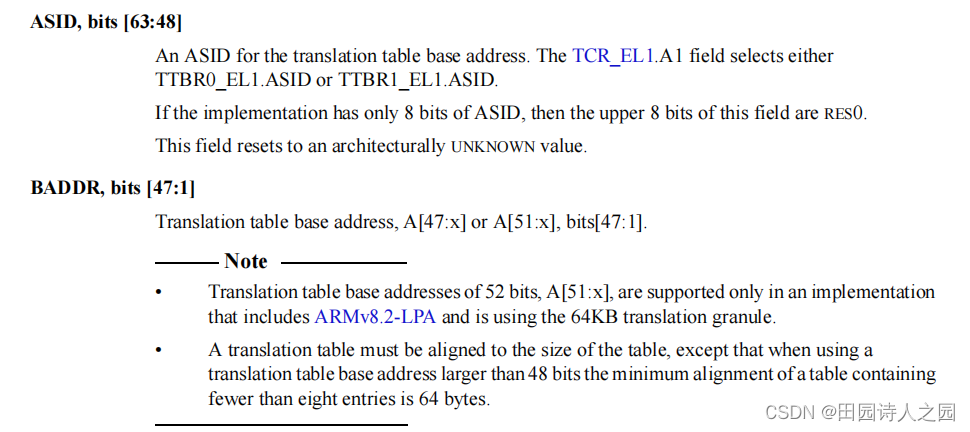

3.1 TTBR1_EL1

TTBR1_EL1, Translation Table Base Register 1 (EL1)

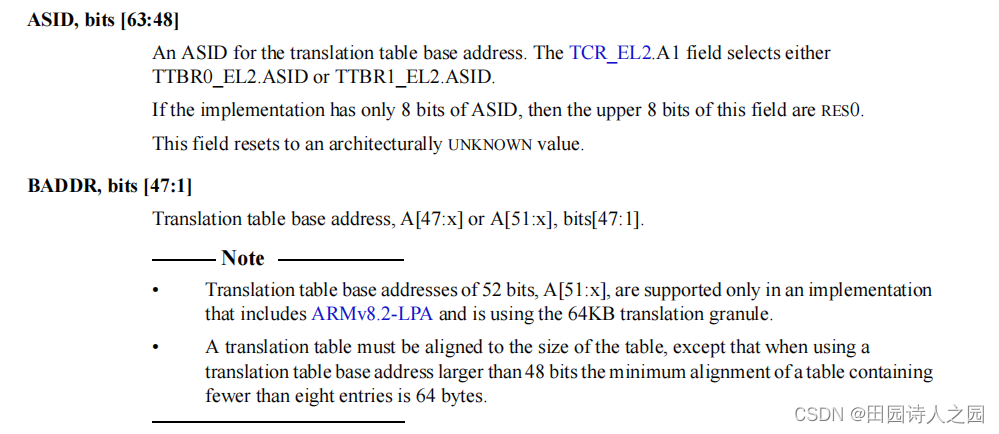

3.2 TTBR1_EL2

TTBR1_EL2, Translation Table Base Register 1 (EL2)

4 访问TTBRx寄存器

4.1 TTBR0_ELx

读TTBR0_ELx寄存器的值到普通寄存器中

mrs <Xt>, TTBR0_ELx

将普通寄存器Xt的值写入TTBR0_ELx寄存器中

msr TTBR0_ELx, <Xt>

4.2 TTBR1_ELx

读TTBR1_ELx寄存器的值到普通寄存器中

mrs <Xt>, TTBR1_ELx

将普通寄存器Xt的值写入TTBR1_ELx寄存器中

msr TTBR1_ELx, <Xt>

5 TTBRx保留的是物理地址还是虚拟地址

5.1 保存的是物理地址还是虚拟地址

在ARMv8架构中,TTBR(Translation Table Base Register)寄存器保存的是一级页表的物理地址。

ARMv8架构使用了分页内存管理方式。页表包含了虚拟地址到物理地址的映射,当CPU需要访问内存时,硬件会根据虚拟地址查找页表,以获得对应的物理地址。

页表本身也在内存中,因此需要有一个方式让硬件知道它在哪里。这就是TTBR寄存器的用途。当页表需要被查找时,硬件会从TTBR寄存器中读出页表的物理地址,然后再根据虚拟地址在页表中查找对应的物理地址。因此,TTBR寄存器中保存的是一级页表的物理地址。

5.2 为什么是物理地址而不是虚拟地址

使用物理地址而非虚拟地址的主要原因是为了避免递归和降低复杂性。

如果TTBR保存的是虚拟地址,那在转换虚拟地址为物理地址时,就需要先找到页表的物理地址,而页表的虚拟地址又需要做同样的转换,这就形成了无限递归,无法完成寻址。

其次,从虚拟地址转化到物理地址是一个非常频繁的操作,如果在这个过程中还要再次进行地址转化,效率将极其低下。从物理地址直接索引可以减少时间和复杂性。

保存物理地址还降低了处理器在地址转换时的硬件实现复杂性,处理器每次进行地址转换时,可以直接从TTBR加载页表的物理基地址,不需要再经过一次虚拟到物理的转换。

因此,为了解决这种递归问题,同时提高处理器的效率和简化硬件设计,页表的地址需要是物理地址。

911

911

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?