Lattice CPLD,是板载GPIO控制芯片,我使用的这款LCMX0256C,上电后支持两种模式,默认高电平输出、或者默认全低电平输出,如果需要切换模式,需要刷FW,本文介绍了一种刷FW的方法

1、需要的工具的软件

烧录文件,可以联系厂家技术支持获取

2、烧录方法和注意事项

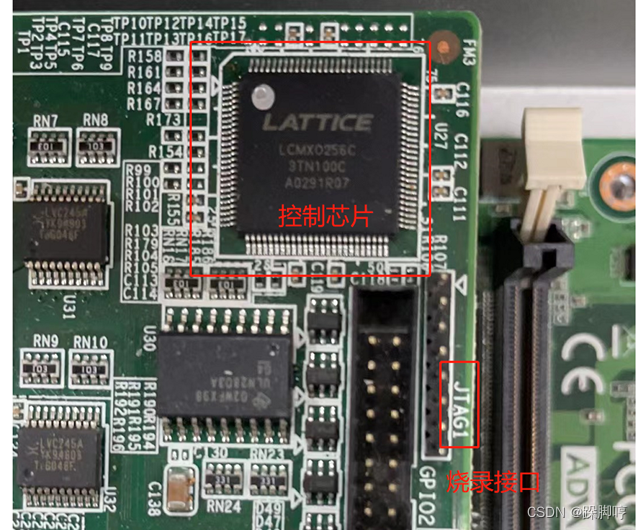

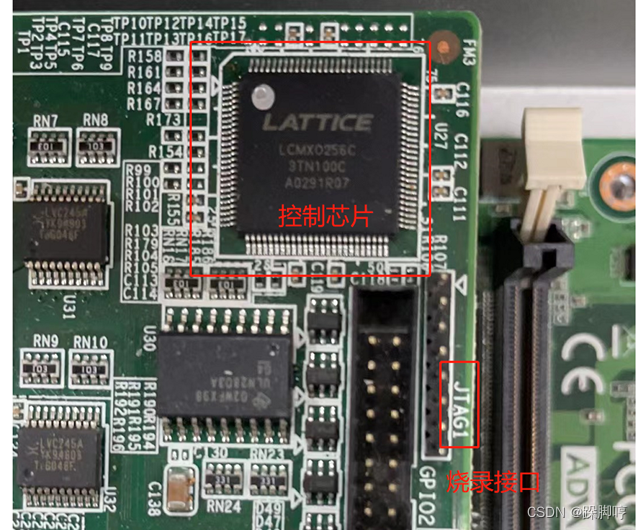

在信号载板上找到控制芯片和JTAG1烧录接口

机器需要保持有电的状态,打开烧录软件,点击Scan查找设备

Lattice CPLD,是板载GPIO控制芯片,我使用的这款LCMX0256C,上电后支持两种模式,默认高电平输出、或者默认全低电平输出,如果需要切换模式,需要刷FW,本文介绍了一种刷FW的方法

1、需要的工具的软件

烧录文件,可以联系厂家技术支持获取

2、烧录方法和注意事项

在信号载板上找到控制芯片和JTAG1烧录接口

机器需要保持有电的状态,打开烧录软件,点击Scan查找设备

638

638

2222

2222

3298

3298

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?