一.单周期CPU设计

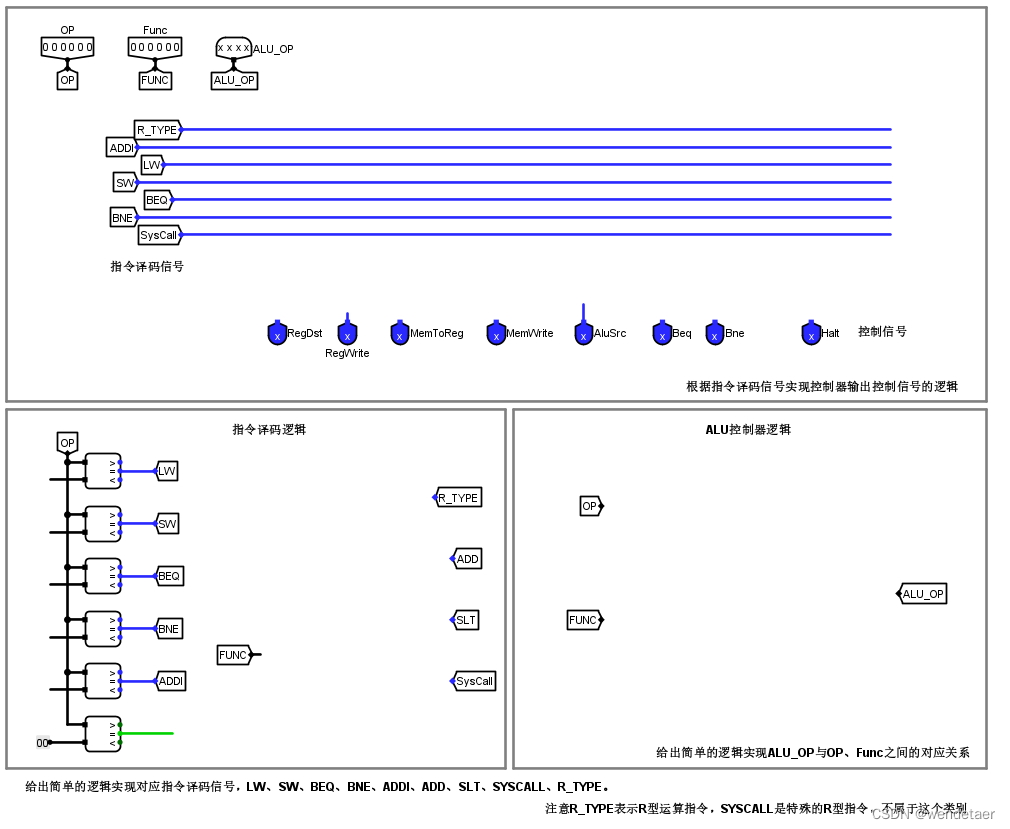

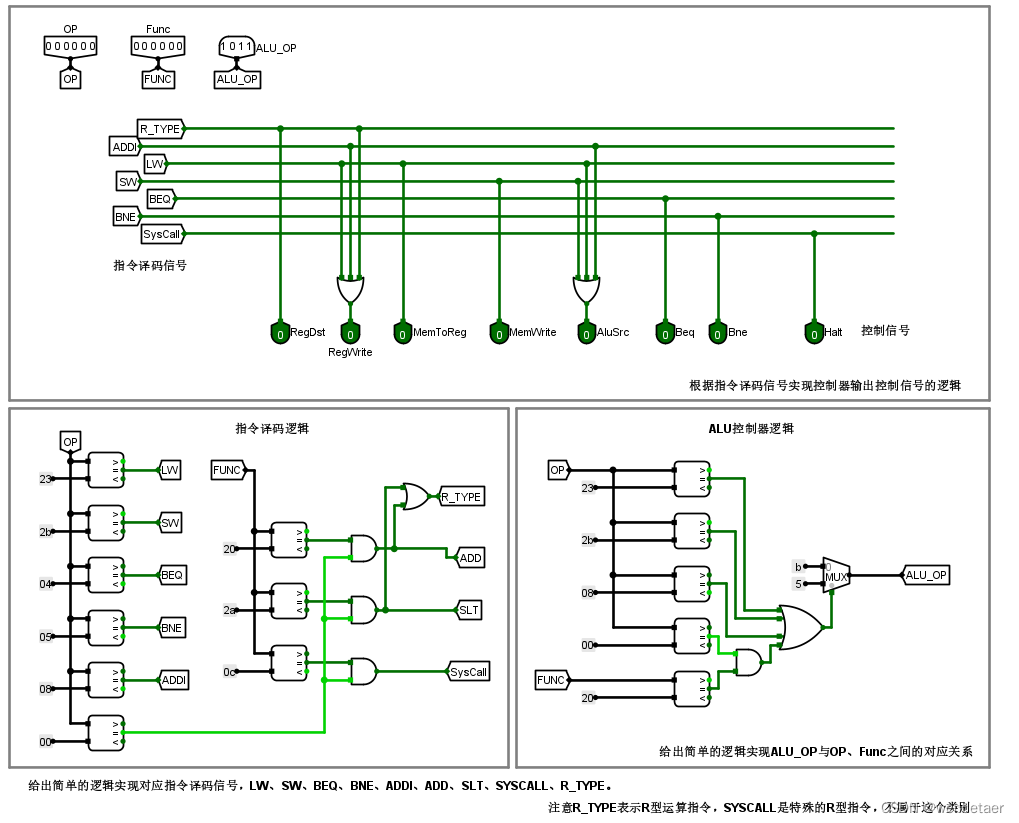

1.单周期硬布线控制器

2.单周期MIPS(硬布线)

二.多周期CPU设计

1.微程序地址转移逻辑

打开微程序地址转移逻辑自动生成文件

修改第一个表后,第二个表的数据会自动修改

将修改后的表达式填入组合电路分析

生成后的微程序地址转移逻辑如图所示

2.多周期微程序控制器

打开微指令自动生成文件

按照图示填写,微指令十六进制编码会自动生成,将生成的十六进制编码填入指令存储器

3.多周期MIPS(微程序)

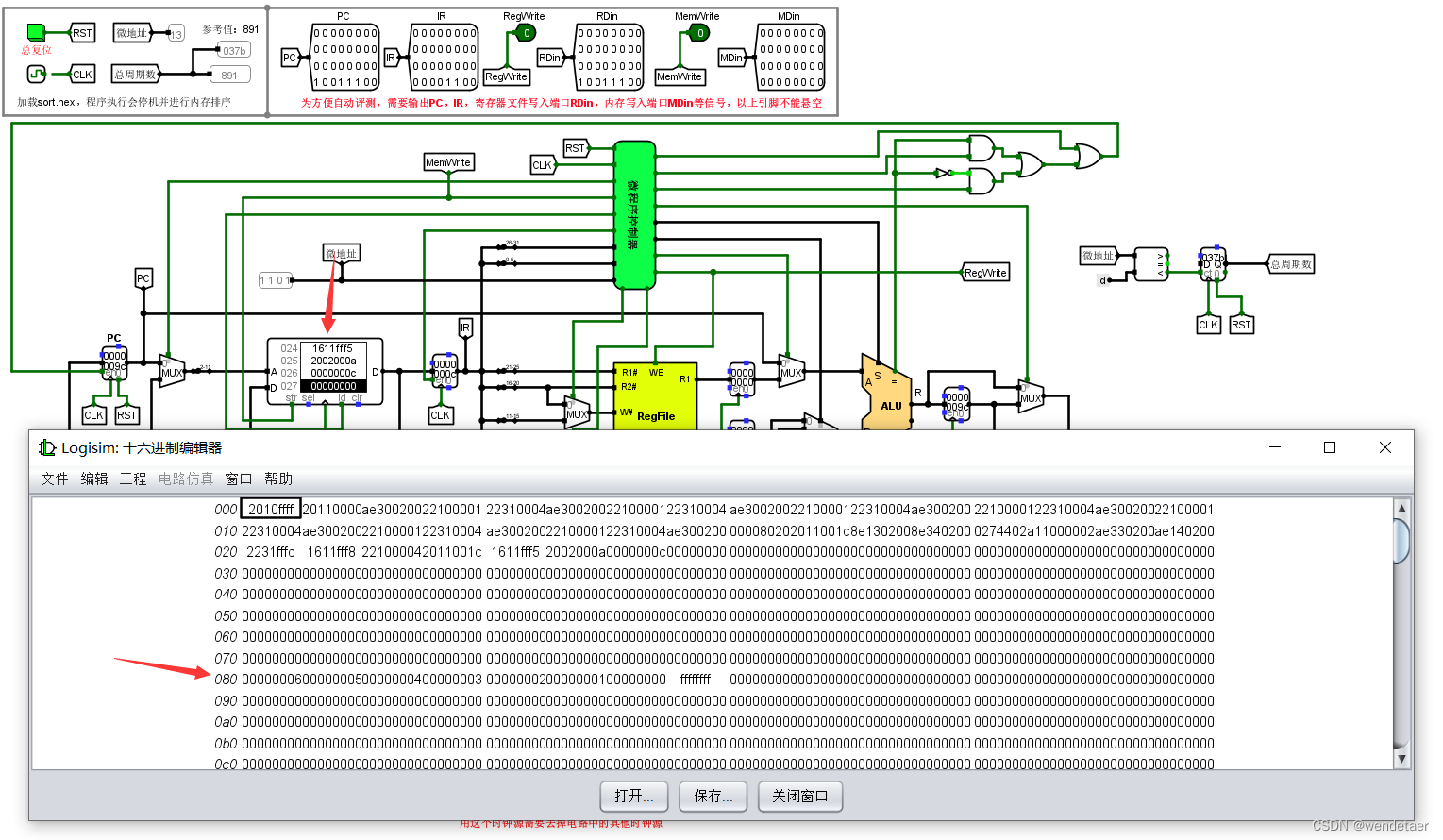

三.CPU测试

1.单周期CPU测试

加载sort.hex文件,然后运行程序

查看数据存储器,第80行呈降序排列,正常运行

2.多周期CPU测试

同样加载sort.hex文件,查看运行结果

查看数据存储器,第80行呈降序排列,正常运行

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?