PCI与PCI_E的学习参照于Intel给出的EDS,以及博客上大神的博文,再次对学习进行总结,由于水平有限,存在不足,望指正,同时也感谢CSDN提供的平台。(学习互助,共同进步)。

一:PCI的物理结构

定义:PCI即Peripheral Component Interconnect,中文意思是“外围器件互联”,是由PCISIG (PCI Special Interest Group)推出的一种局部并行总线标准.他是一种同步的独立于处理器的32位或64位局部总线。从结构上看,PCI是在CPU的供应商和原来的系统总线之间插入的一级总线,具体由一个桥接电路实现对这一层的管理,并实现上下之间的接口以协调数据的传送。从1992年创立规范到如今,PCI总线已成为了计算机的一种标准总线。已成为局部总线的新标准,广泛用于当前高档微机、工作站,以及便携式微机。主要用于连接显示卡、网卡、声卡。

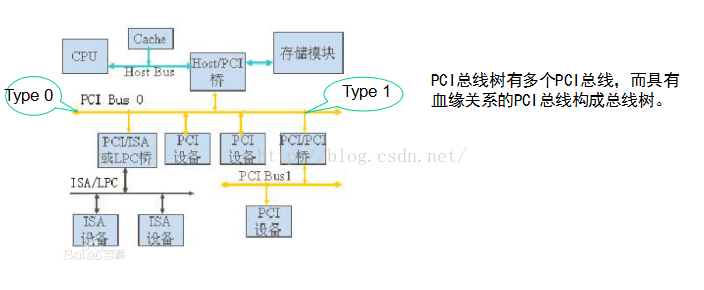

PCI总线是一种树型结构,并且独立于CPU总线,可以和CPU总线并行操作。PCI总线上可以挂接PCI设备和PCI桥片,PCI总线上只允许有一个PCI主设备,其他的均为PCI 从设备,而且读写操作只能在主从设备之间进行,从设备之间的数据交换需要通过主设备中转。

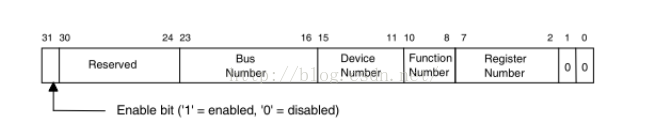

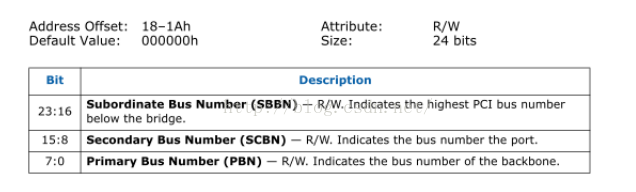

前面的结构图提到bus,那么计算机是如何匹配bus呢?在EDS中,提到了bus number register,通过匹配与读取这个寄存器的数据来匹配bus,该寄存器如下所示:

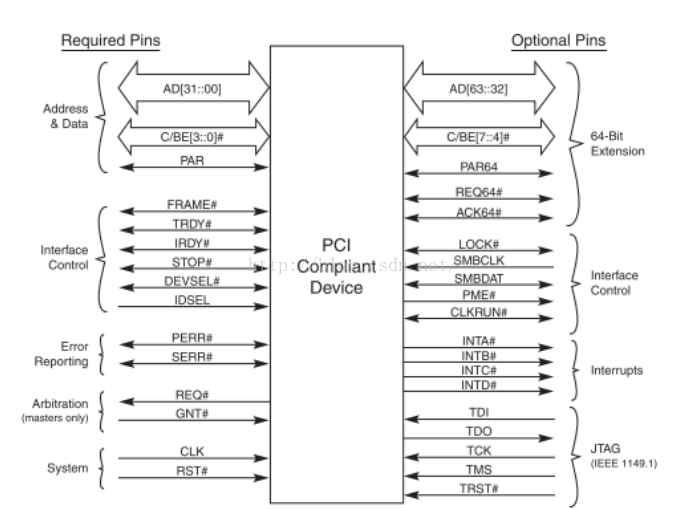

PCI总线的引脚结构:

PCI主设备最少需要49pin脚,而从设备则最少需要47个pin脚,如下图所示:

对部分重要的引脚进行简单的介绍,摘自Datasheet里的内容,如下:(H/W设计需要对这些进行详细的了解,软件上要求不高,会使用即可)

CLK:PCI时钟,上升沿有效

RST:Reset信号

FRAME#:标志传输开始与结束

IRDY#:Master可以传输数据的标志

DEVSEL#:当Slave发现自己被寻址时置低应答

TRDY#:Slave可以转输数据的标志

STOP#:Slave主动结束传输数据的信号

IDSEL:在即插即用系统启动时用于选中板卡的信号

AD[31::0]:地址/数据分时复用总线

C/BE#[3::0]:命今/字节使能信号

PAR:奇偶校验信号

REQ#:Master用来请求总线使用权的信号

GNT#:Arbiter允许Master得到总线使用权的信号

PERR#,数据奇偶校验错

SERR#,系统奇偶校验错

二:PCI的总线特点参数

(1)传输速率高最大数据传输率为132MB/s,当数据宽度升级到64位,数据传输率可达264MB/s。

(2)多总线共存采用PCI总线可在一个系统中让多种总线共存,容纳不同速度的设备一起工作。

(3)独立于CPU PCI总线不依附于某一具体处理器,即PCI总线支持多种处理器及将来发展的新处理器,在更改处理器品种时,更换相应的桥接组件即可。

(4)自动识别与配置外设 用户使用方便。

(5)并行操作能力。

(6)总线时钟频率33.3MHz/66.6MHz。

(7)总线宽度32位/64位。

(8)最大数据传输率132MB/s(264MB/s)。

(9)支持64位寻址。

(10)适应5V和3.3V电源环境。

总而言之,PCI总线具有高速性,即插即用性,可靠性,复杂性,自动配置,共享中断,扩展性好,多路复用等特点。

三:PCI的访问方式(对于软件开发来说,这一块最重要)

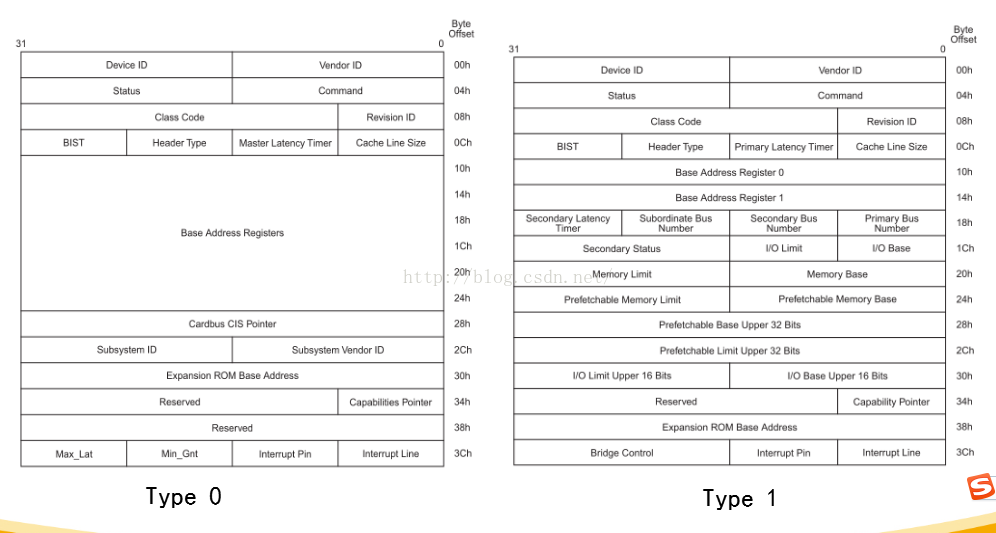

两个重要的type:0/1

Type 0模式是访问bus 0,而Type 1是访问pci_pci_bridge

Type 1的工作方式

一:扫描当前pci总线上所有的pci桥

二:若bus number等于某一个pci桥上的secondary bus number,说明配置请求的device在该secondary bus上,转type 0模式;

三:若secondary bus number<bus number<Subordinate Bus number,则说明type 1请求的设备由该pci总线下从属的某一个桥管理,pci桥认领type1,然后进行一操作,直到找到相应的设备,找到后转type 0,进行处理;若找不到该设备,返回值全为1,即FF。

type 0和type 1 的header 决定其结构的不同,EDS给出的header如下:

不管是type 0还是type 1模式,configration space header的前16个字节都是相同的

其中Vendor ID,Device ID,Revision ID,Header type,Class code对于所有的pci设备都是必须实现的。

Vendor ID:由pci sig分配,0FFFH为无效值

Device ID:由vendor来分配

Revision ID:Device ID的扩展,值由vendor选定

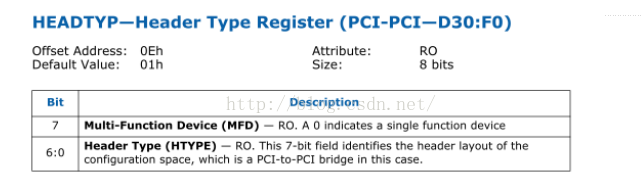

Header type:可用来表示10H到3FH的布局类型,也可指出设备是否包含多功能。第7位来指出其是否为多功能设备,[6::0]表示是布局类型。

Class Code:标识设备的总体功能和特定的寄存器级编程接口。

接下来说一下,相关寄存器的设置,计算机是如何选择type的呢?

由该寄存器决定采用哪一种表头格式,分别为:

type 1,pci to pci的桥接器(01h)

Type 2,pci to cardbus的桥接器(02h)

Type 0,除以上装置外的装置(00h)

Bit 7 用来表示是否为多功能设备,0表示单一功能设备

使用pci访问涉及到两个重要的寄存器,分别是0xcf8,0xcfc,在EDS中给出的说明如下:

0xcf8:config_address

由该寄存器决定采用哪一种表头格式,分别为:

type 1,pci to pci的桥接器(01h)

Type 2,pci to cardbus的桥接器(02h)

Type 0,除以上装置外的装置(00h)

Bit 7 用来表示是否为多功能设备,0表示单一功能设备

0xcfc config_data

数据寄存器,确定了地址之后在该寄存器内进行数据读取。

由该寄存器决定采用哪一种表头格式,分别为:

type 1,pci to pci的桥接器(01h)

Type 2,pci to cardbus的桥接器(02h)

Type 0,除以上装置外的装置(00h)

Bit 7 用来表示是否为多功能设备,0表示单一功能设备

前面提到地址寄存器0XCF8,那么地址是如何计算的呢?

0xcf8为32位的寄存器,所以往该寄存器写入数据的时候需要进行移位或者乘法运算

首先确定好需要读写的bus,device,function,register,最高位是enable,使能位,需要置1,固地址的计算为:

Address=(0x80000000|(bus<<16)|(device<<11)|(function<<8)|register

或

Address=(0x80000000+bus*(pow(2,16))+device*(pow(2,11))+function*(pow(2,8))+register)

接下来会有一段程序示例,本段程序采用的编译器是watcom C,(不同的编译器所包含或者定义的函数名字存在差异,因根据实际情况区分,比如VC是没有定义IO访问函数的,需要采用内联汇编的方式访问)

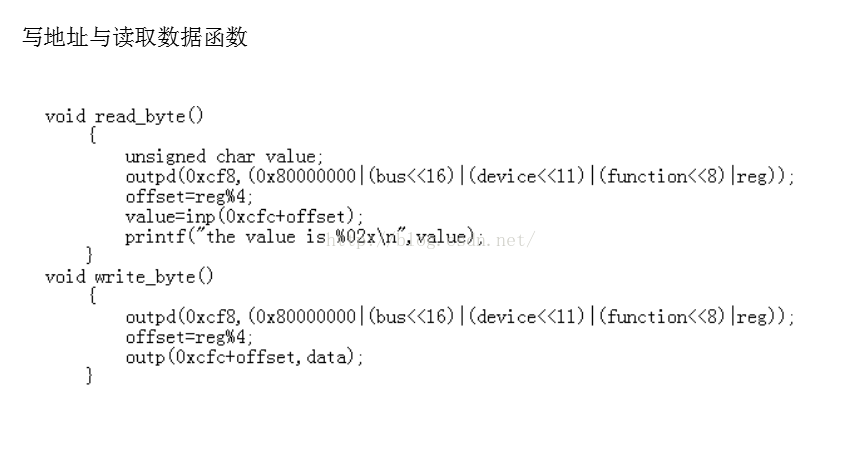

读写byte的函数如下;

由该寄存器决定采用哪一种表头格式,分别为:

type 1,pci to pci的桥接器(01h)

Type 2,pci to cardbus的桥接器(02h)

Type 0,除以上装置外的装置(00h)

Bit 7 用来表示是否为多功能设备,0表示单一功能设备

PCI_E的介绍:

定义:PCI Express是新一代的总线接口。早在2001年的春季,英特尔公司就提出了要用新一代的技术取代PCI总线和多种芯片的内部连接,并称之为第三代I/O总线技术。随后在2001年底,包括Intel、AMD、DELL、IBM在内的20多家业界主导公司开始起草新技术的规范,并在2002年完成,对其正式命名为PCI Express。

特点:

PCI Express的接口根据总线位宽不同而有所差异,包括X1、X4、X8以及X16(X2模式将用于内部接口而非插槽模式)。较短的PCI Express卡可以插入较长的PCI Express插槽中使用。PCI Express接口能够支持热拔插,这也是个不小的飞跃。PCI Express卡支持的三种电压分别为+3.3V、3.3Vaux以及+12V。用于取代AGP接口的PCI Express接口位宽为X16,将能够提供5GB/s的宽带,即便有编码上的损耗但仍能够提供4GB/s左右的实际带宽,远远超过AGP 8X的2.1GB/s的带宽。

尽管PCI Express技术规格允许实现X1(250MB/秒),X2,X4,X8,X12,X16和X32通道规格,但是依形式来看,PCI Express X1和PCI Express X16将成为PCI Express主流规格,同时chipset厂商将在南桥芯片当中添加对PCI Express X1的支持,在北桥芯片当中添加对PCI Express X16的支持。除去提供极高数据传输带带宽之外,PCI Express因为采用串行数据包方式传递数据,所以PCI Express接口每个针针脚可以获得比传统I/O标准更多的带宽,这样就可以降低PCI Express设备生产成本和体积。

兼容性方面,PCI Express在软件层面上兼容的PCI技术和设备,支持PCI设备和内存模组的初始化,也就是说驱动程序、操作系统无需推倒重来,就可以支持PCI Express设备。PCI Express是新一代能够提供大量带带宽和丰富功能以实现令人激动的新式图形应用的全新架构。PCI Express可以为带宽渴求型应用分配相应的带宽,大幅提高中央处理器(CPU)和图形处理器(GPU)之间的带宽。对最终用户而言,他们可以感受影院级图象效果,并获得无缝多媒体体验。

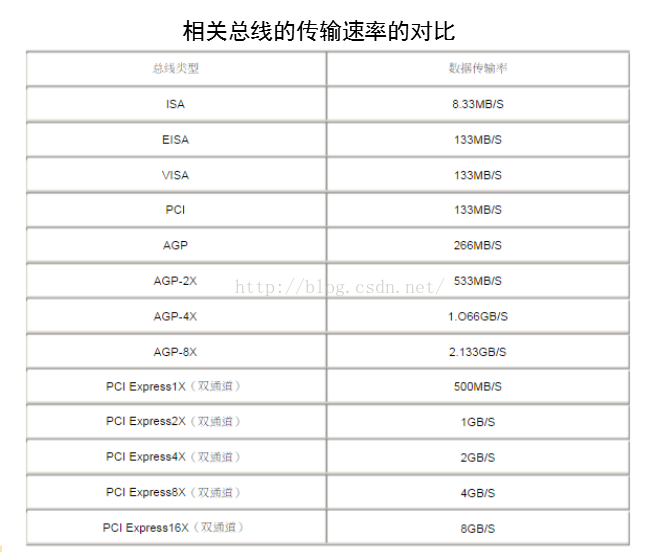

PCI_E最大的优势在于他的传输速率:

16X 2.0版本的可达到10GB/S

PCI_E3.0的带宽为8GT/S

PCI_E采用的是内存访问的方式,这里暂不做说明,会在后面的博文当中给出介绍。

简单说一下PCI与PCI_E的区别:

传输速率的对比:

由该寄存器决定采用哪一种表头格式,分别为:

type 1,pci to pci的桥接器(01h)

Type 2,pci to cardbus的桥接器(02h)

Type 0,除以上装置外的装置(00h)

Bit 7 用来表示是否为多功能设备,0表示单一功能设备

1 传输速率不同:从最高传输速率对比,PCI_E远高于PCI

2 传输方式不同:PCI采用的是并行传输方式,即用多条信号线同时并行传输多位数据,而PCI_E采用的是串行传输方式,最大传输速度为8Gbit/S.

3 访问方式不同:PCI采用I/O访问,而PCI_E采用的为MMIO内存映射IO的方式

4 空间大小不同:PCI为256个字节,即00h—ffh;而PCI_E为00h—ffffh。

总之,双方各有优势:

PCI由于采用的是并行传输,就无法连接太多的设备,总线的扩展性相对于PCI_E也较差,同时在传输时的线间干扰也比较严重。同时多个设备工作时,总线有效带宽也会被拉低,传输速率也会因此变慢。

PCI_E采用串行传输方式,支持双向传输模式和数据分通道传输。因为PCI_E采用点对点的传输方式,每一个设备都有自己的传输通道,避免了干扰的问题,同样也可以保证传输速率不被拉低。

但PCI的优势也很明确,就是结构简单,设计上难度小,成本低,利于推广。

Thanks for your reading.

type 1,pci to pci的桥接器(01h)

Type 2,pci to cardbus的桥接器(02h)

Type 0,除以上装置外的装置(00h)

Bit 7 用来表示是否为多功能设备,0表示单一功能设备

11万+

11万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?