1.LVDS基础、原理、图文讲解

LVDS是一种低摆幅的差分信号技术,它使得信号能在差分PCB 线对或平衡电缆上以几百Mbps的速率传输,其低压幅和低电流驱动输出实现了低噪声和低功耗。IEEE 在两个标准中对LVDS 信号进行了定义。ANSI/TIA/E IA -644 中,推荐最大速率为655Mbps ,理论极限速率为1.923Gbps。

一、LVDS组成

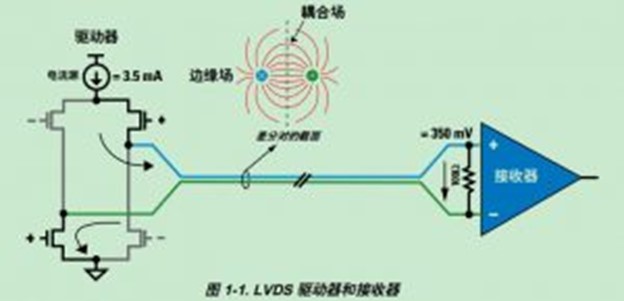

LVDS 信号传输一般由三部分组成:差分信号发送器,差分信号互联器,差分信号接收器。

差分信号发送器:将非平衡传输的TTL 信号转换成平衡传输的LVDS 信号。

差分信号接收器:将平衡传输的LVDS 信号转换成非平衡传输的TTL 信号。

差分信号互联器:包括联接线(电缆或者PCB 走线),终端匹配电阻。按照IEEE 规定 ,电阻为100 欧。我们通常选择为100 ,120 欧。

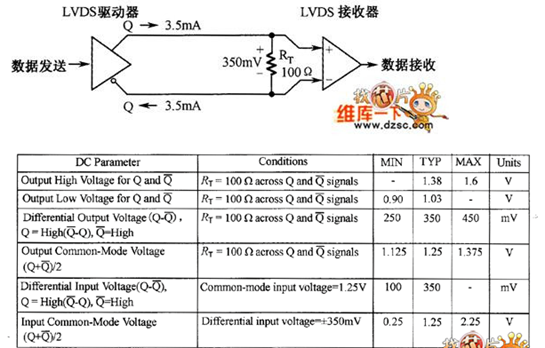

二、 LVDS信号电平特性 (电流驱动--电压接收--共模电压由0-2.4v直流偏置,典型为1.2v--差模电压:350mv由驱动电流提供-)

LVDS 物理接口使用1.2V 偏置电压作为基准(共模直流电压),提供大约350mV 摆幅(差模电压)。LVDS 驱动器由一个驱动差分线对的电流源组成(通常电流为3.5mA),

LVDS 接收器具有很高的输入阻抗,因此驱动器输出的电流大部分都流过100Ω的匹配电阻,并在接收器的输入端产生大约350mV 的电压。电流源为恒流特性,终端电阻在100 ――120 欧姆之间,则电压摆动幅度为:3.5mA * 100 = 350mV ;3.5mA * 120 = 420m V 。

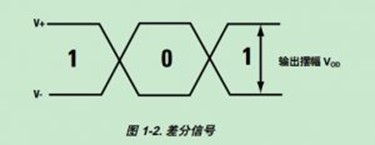

由逻辑"0 "电平变化到逻辑"1 "电平是需要时间的。由于LVDS 信号物理电平变化在0 .85――1 .55V 之间,其由逻辑"0"电平到逻辑"1 "电平变化的时间比TTL 电平要快得多,所以LVDS 更适合用来传输高速变化信号。其低压特点,功耗也低.

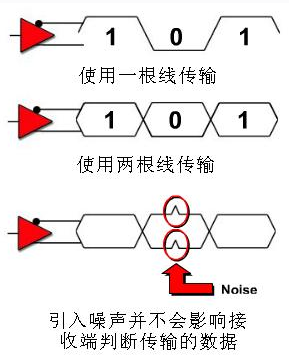

三、抗干扰性

0--1电平表示:当输出V+=350MA电流,V-=0ma电流,那么输出的为高电平(在接收端的匹配电阻转换为电压值350mv),反之为低电平

摆幅VOD=共模差值350MV

在实际线路传输中,

V+总电流=A(交流350MA)+D(直流1.2V/100=12MA)-----当然了,最主要的还是差模电压的交流信号

V-总电流=A(交流 0MA)+D(直流1.2V/100=12MA)-----当然了,最主要的还是差模电压的交流信号

差值--(在100欧姆上的电压)=[(350+12)-(0+12)]*100=0.35*100=0.35v=350mv

线路存在干扰,并且同时出现在差分线对上,

V+总电流=A(交流350MA)+D(直流1.2V/100=12MA) +G(干扰8ma)-----当然了,最主要的还是差模电压的交流信号

V-总电流=A(交流 0MA)+D(直流1.2V/100=12MA)+G(干扰8ma)-----当然了,最主要的还是差模电压的交流信号

差值--(在100欧姆上的电压)=[(350+12+8)-(0+12+8)]*100=0.35*100=0.35v=350mv(由于干扰是加在差分线上的所以相等抵消了). 噪声被抑止掉。

上述可以形象理解差分方式抑止噪声的能力。在实际芯片中,是在噪声容限内,采用"比较"及"量化"来处理的。

LVDS 接收器可以承受至少±1V 的驱动器与接收器之间的地的电压变化。由于LVDS驱动器典型的偏置电压为+1.2V,地的电压变化、驱动器偏置电压以及轻度耦合到的噪声之和,在接收器的输入端相对于接收器的地是共模电压。这个共模范围是:+0.2V~+2.2 V 。建议接收器的输入电压范围为:0V~+2.4V.

四、总结

LVDS(Low Voltage Differential Signaling)是一种低摆幅的差分信号技术,它使得信号能在差分PCB线对或平衡电缆上以几百Mbps的速率传输,其低压幅和低电流驱动输出实现了低噪声和低功耗。

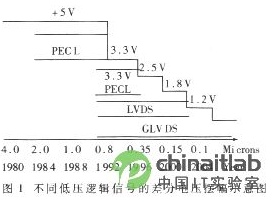

几十年来,5V供电的使用简化了不同技术和厂商逻辑电路之间的接口。然而,随着集成电路的发展和对更高数据速率的要求,低压供电成为急需。降低供电电压不仅减少了高密度集成电路的功率消耗,而且减少了芯片内部的散热,有助于提高成度。

减少供电电压和逻辑电压摆幅的一个极好例子是低压差分信号(LVDS)。LVDS物理接口使用1.2V偏置提供400mV摆幅的信号(使用差分信号的原因是噪声以共模的方式在一对差分线上耦合出现,并在接收器中相减从而可消除噪声)。LVDS驱动和接收器不依赖于特定的供电电压,因此它很容易迁移到低压供电的系统中去,而性能不变。作为比较,ECL和PECL技术依赖于供电电压,ECL要求负的供电电压,PECL参考正的供电电压总线上电压值(Vcc)而定。而GLVDS是一种发展中的标准尚未确定的新技术,使用500mV的供电电压可提供250mV 的信号摆幅。不同低压逻辑信号的差分电压摆幅示于图1。

LVDS在两个标准中定义。IEEE P1596.3(1996年3月通过),主要面向SCI(Scalable Coherent Interface),定义了LVDS的电特性,还定义了SCI协议中包交换时的编码;ANSI/EIA/EIA-644(1995年11月通过),主要定义了LVDS的电特性,并建议了655Mbps的最大速率和1.823Gbps的无失真媒质上的理论极限速率。在两个标准中都指定了与物理媒质无关的特性,这意味着只要媒质在指定的噪声边缘和歪斜容忍范围内发送信号到接收器,接口都能正常工作。 LVDS具有许多优点:①终端适配容易;②功耗低;③具有fail-safe特性确保可靠性;④低成本;⑤高速传送。这些特性使得LVDS在计算机、通信设备、消费电子等方面得到了广泛应用。

2.TMDS信号

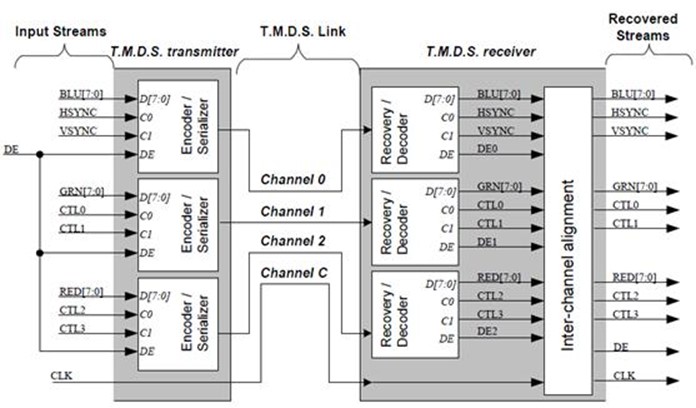

HDMI传输原理和DVI相同,由Silicon Image公司发明的TMDS(Time Minimized Differential Signal)最小化传输差分信号传输技术。TMDS是一种微分信号机制,采用的是差分传动方式。这不仅是DVI技术的基础,也是HDMI技术的基础原理。

一、TMDS原理

TMDS差分传动技术是一种利用2个引脚间电压差来传送信号的技术。传输数据的数值("0"或者"1")由两脚间电压正负极性和大小决定。即,采用2根线来传输信号,一根线上传输原来的信号,另一根线上传输与原来信号相反的信号。这样接收端就可以通过让一根线上的信号减去另一根线上的信号的方式来屏蔽电磁干扰,从而得到正确的信号。

每一个标准的HDMI连接,都包含了3个用于传输数据的TMDS传输通道,还有1个独立的TMDS时钟通道,以保证传输时所需的统一时序。在一个时钟周期内,每个TMDS通道都能传送10bit的数据流。而这10bit数据,可以由若干种不同的编码格式构成。

另外,还有一个显示数据通道(DDC),是用于读取表示接收端显示器的清晰度等显示能力的扩展显示标识数据(EDID)的信号线。搭载HDCP(High-bandwidth Digital Content Protection,高带宽数字内容保护技术)的发送、接收设备之间也利用DDC线进行密码键的认证。

一个HDMI包括3个TMDS数据通道和1个TMDS时钟通道。

每个数据通道都通过编码算法(异或、异或非等),将8位数据转换成10位数据,前8为数据由原始信号经运算后获得,第9位指示运算的方式,第10位用来对应直流平衡。通过这种算法,会使得数据的传输和恢复更加可靠。

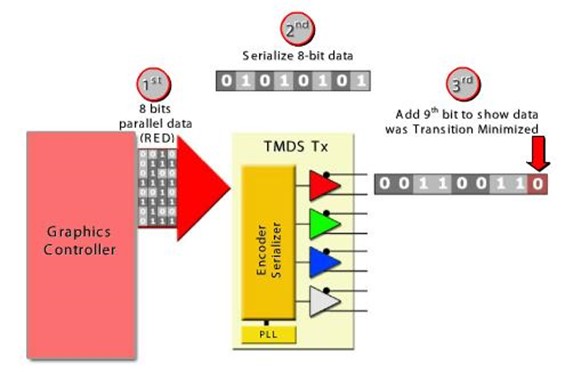

1.传输最小化

第一步:将8位并行RED数据发送到TMDS Tx。

第二步:并/串转换.

第三步:进行最小化传输处理,加上第9位,即编码过程。第9位数据称为编码位。

2.直流平衡(DC-balanced)

直流平衡:在编码过程中,保证信道的直流偏移为零。方法是在原来的第9位数据后面加上1位,使得TMDS发送的"0"、"1"数量保持基本一致。这样,传输的数据趋于直流平衡,使信号对传输线的电磁干扰减少,提高信号传输的可靠性。

3.差分信号

利用两引脚间电压差来传送信号。

二、HDMI与分辨率

PCLK:像素时钟

以1920x1080p/60hz为例:1920*1080*60=124.4MHz

以1280x720p/60hz为例:1280*720*60=55.3MHz

带宽:1s内传输的数据量(bit)

4K频率需要的带宽:选最常用的3840x2160分辨率,色深的话常用的是8位,RGB三色就是24bit,我们的目标是60Hz刷新率(60fps)→→→ 3840*2160*24bit*60fps=11.94Gbps

HDMI1.4像素时钟高达340MHz,即最大带宽是:

→→→ 340MHz*10bit(10bit编码)*3(3个数据通道)=10.2Gbps

但是由于HDMI采用的是8bit/10bit编码方式,实际效率是理论值的80%,所以10.2Gbps能传输的最大视频带宽是10.2*0.8=8.1Gbps

HDMI带宽和TMDS的关系

而在HDMI标准中所规定的带宽,在1.0版本就设定为最高4.96Gbps。那么这一数值是怎么的来的呢?和TMDS又有什么关系呢?我们看下面的公式:

这是一个适用于所有串口传输接口带宽计算的公式。在所有的数字电路中,都有一个负责提供基本频率的元器件——晶振,它就像是一个精确的闹钟一样,电路中所有的元器件都按照它的节奏统一行动。比方说,某一运算电路的晶振频率是100Hz,就是说这一电路在一秒钟内可以进行100次运算过程。由此可见,晶振的工作频率越高,每秒所能处理的运算次数就会越多,数据的处理能力也就会越强大。而HDMI标准中,这个原理同样适用。

HDMI电路中的时钟频率,在最初制定时范围从25MHz-165MHz之间,也就是说一个TMDS通道每秒最多能传输165MHz×10bit=1.65Gbit的数据,3个TMDS通道一秒就可以传输1.65×3=4.95Gbit的数据,再加上控制数据,用标准方法表示就是4.96Gbps的带宽。而如果用像素点来表示,那就是一秒可以传输显示1.65G个像素点(一个完整的像素点信息由R/G/B三原色信息构成)所需要的数据量。

在数字音频方面,HDMI灵活的支持符合IEC60985 L-PCM标准的32kHz、44.1kHz和48kHz、16bit量化的立体声数字音频信号和IEC 61937标准的采样率为192KHz,24bit量化的单路无压缩PCM数字音频信号,或者8路96kHz的声音数据流。此外,在家庭影院中常用的DolbyDigital5.1和DTS数字音频格式也能通过HDMI直接传输。

9656

9656

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?