20240603在飞凌的OK3588-C开发板上跑原厂IPC方案调通OV5645和OV13850

2024/6/3 15:07

【整理完成之后,突然发现没有针对ov13850.c做任何改动,不过它确实可以通过以太网推流了。】

【但是由于没有进行ISP配置,电脑上的VLC通过rtsp最后拿到的是绿油油的鬼影!^_】

rootroot@rootroot-ThinkBook-16-G5-IRH:~/RK3588_IPC_SDK$ ./build.sh lunch

Which would you like? [0]: 3

rootroot@rootroot-ThinkBook-16-G5-IRH:~/RK3588_IPC_SDK$ ./build.sh

Z:\RK3588_IPC_SDK\project\app\rkipc\rkipc\src\rk3588_ipc\main.c

Z:\RK3588_IPC_SDK\project\app\rkipc\rkipc\src\rk3588_multi_ipc\main.c

1、

Z:\RK3588_IPC_SDK\sysdrv\source\kernel\arch\arm64\boot\dts\rockchip\rk3588-nvr-demo.dtsi

&i2c2 {

status = "okay";

extio: tca6424@23 {

compatible = "ti,tca6424";

reg = <0x23>;

interrupt-parent = <&gpio1>;

interrupts = <RK_PA4 IRQ_TYPE_EDGE_FALLING>;

gpio-controller;

pinctrl-0 = <&extio_int_gpio>;

pinctrl-names = "default";

#gpio-cells = <2>;

status = "okay";

};

vdd_npu_s0: vdd_npu_mem_s0: rk8602@42 {

compatible = "rockchip,rk8602";

reg = <0x42>;

vin-supply = <&vcc5v0_sys>;

regulator-compatible = "rk860x-reg";

regulator-name = "vdd_npu_s0";

regulator-min-microvolt = <550000>;

regulator-max-microvolt = <950000>;

regulator-ramp-delay = <2300>;

rockchip,suspend-voltage-selector = <1>;

regulator-boot-on;

regulator-always-on;

regulator-state-mem {

regulator-off-in-suspend;

};

};

};

&pinctrl {

dp {

dp1_hdmi_ctl: dp-hdmi-ctl {

rockchip,pins = <0 RK_PD5 RK_FUNC_GPIO &pcfg_pull_up>,

<3 RK_PB2 RK_FUNC_GPIO &pcfg_pull_up>;

};

};

extio {

extio_int_gpio: extio-int-gpio {

rockchip,pins = <1 RK_PA4 RK_FUNC_GPIO &pcfg_pull_up>;

};

};

rtc {

rtc_int: rtc-int {

rockchip,pins = <0 RK_PB2 RK_FUNC_GPIO &pcfg_pull_up>;

};

};

usb {

vcc5v0_host_en: vcc5v0-host-en {

rockchip,pins = <4 RK_PB0 RK_FUNC_GPIO &pcfg_pull_none>;

};

vcc5v0_otg_en: vcc5v0-otg-en {

rockchip,pins = <4 RK_PA7 RK_FUNC_GPIO &pcfg_pull_none>;

};

};

sata {

sata0_pm_reset: sata0-pm-reset {

rockchip,pins = <4 RK_PA0 RK_FUNC_GPIO &pcfg_output_high>;

};

sata1_pm_reset: sata1-pm-reset {

rockchip,pins = <4 RK_PA1 RK_FUNC_GPIO &pcfg_output_high>;

};

};

};

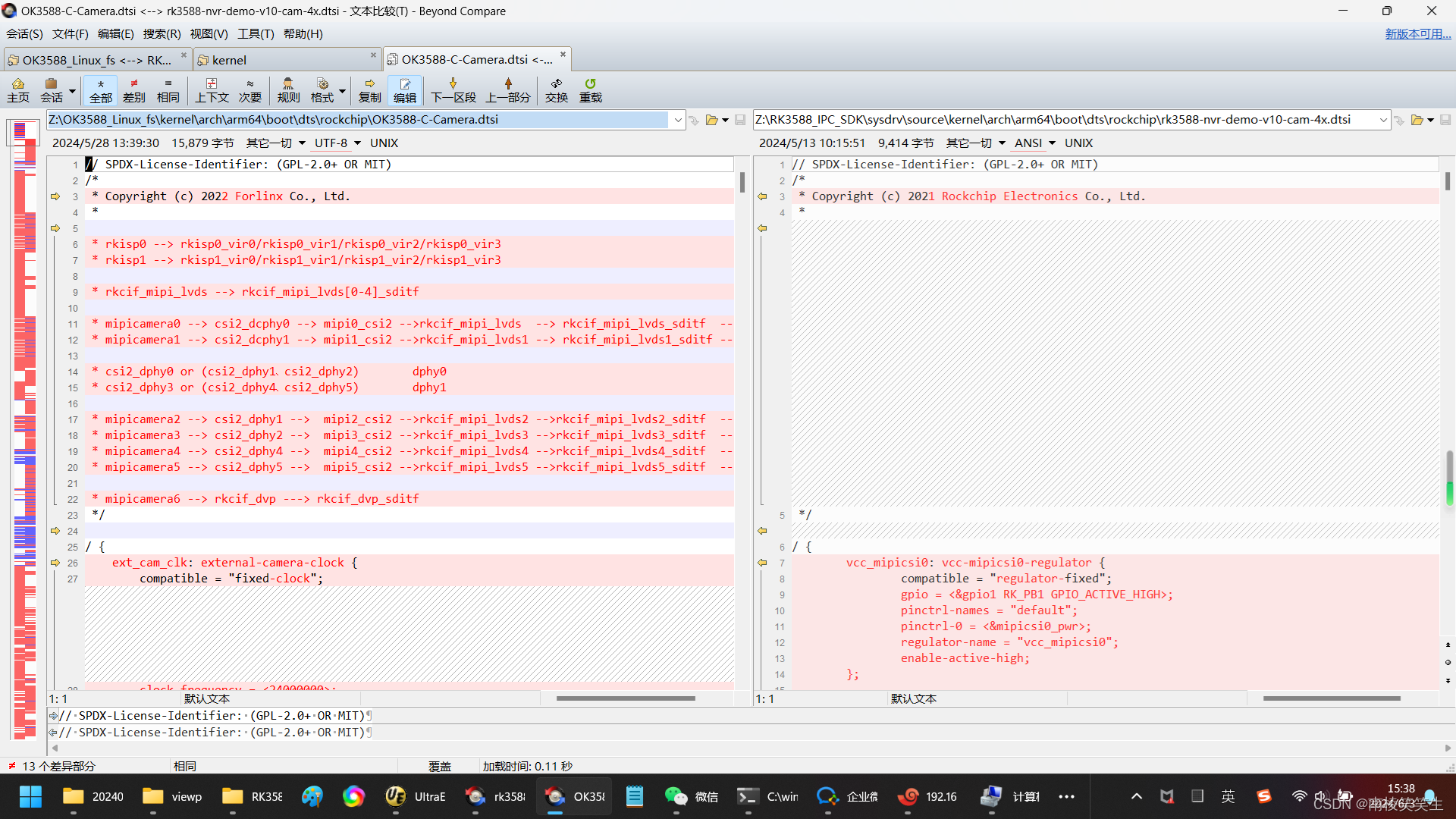

【当时时间追的紧,直接使用飞凌的camera摄像头相关的DTS直接替换,通了!^_】

Z:\OK3588_Linux_fs\kernel\arch\arm64\boot\dts\rockchip\OK3588-C-Camera.dtsi

Z:\RK3588_IPC_SDK\sysdrv\source\kernel\arch\arm64\boot\dts\rockchip\rk3588-nvr-demo-v10-cam-4x.dtsi

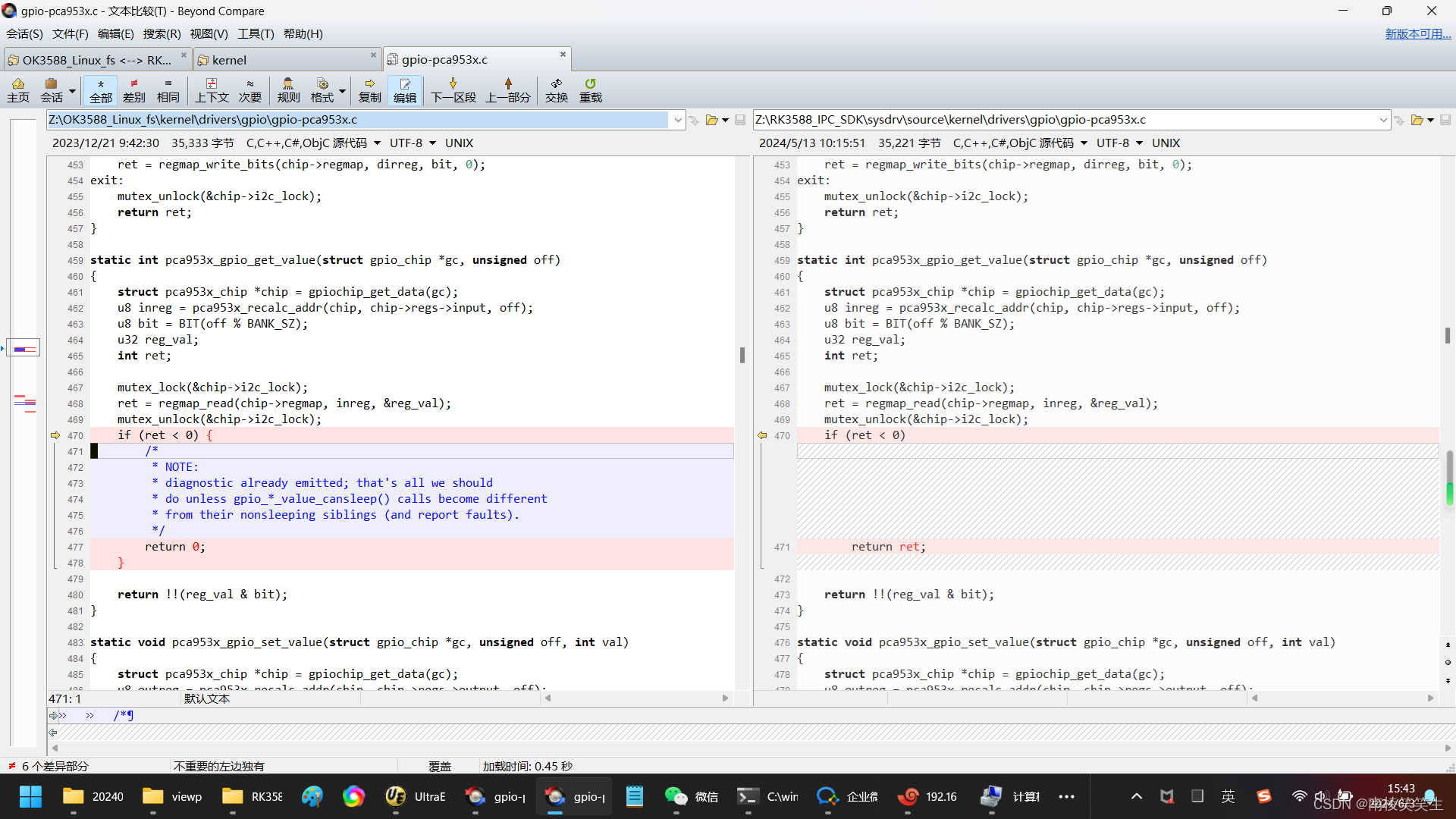

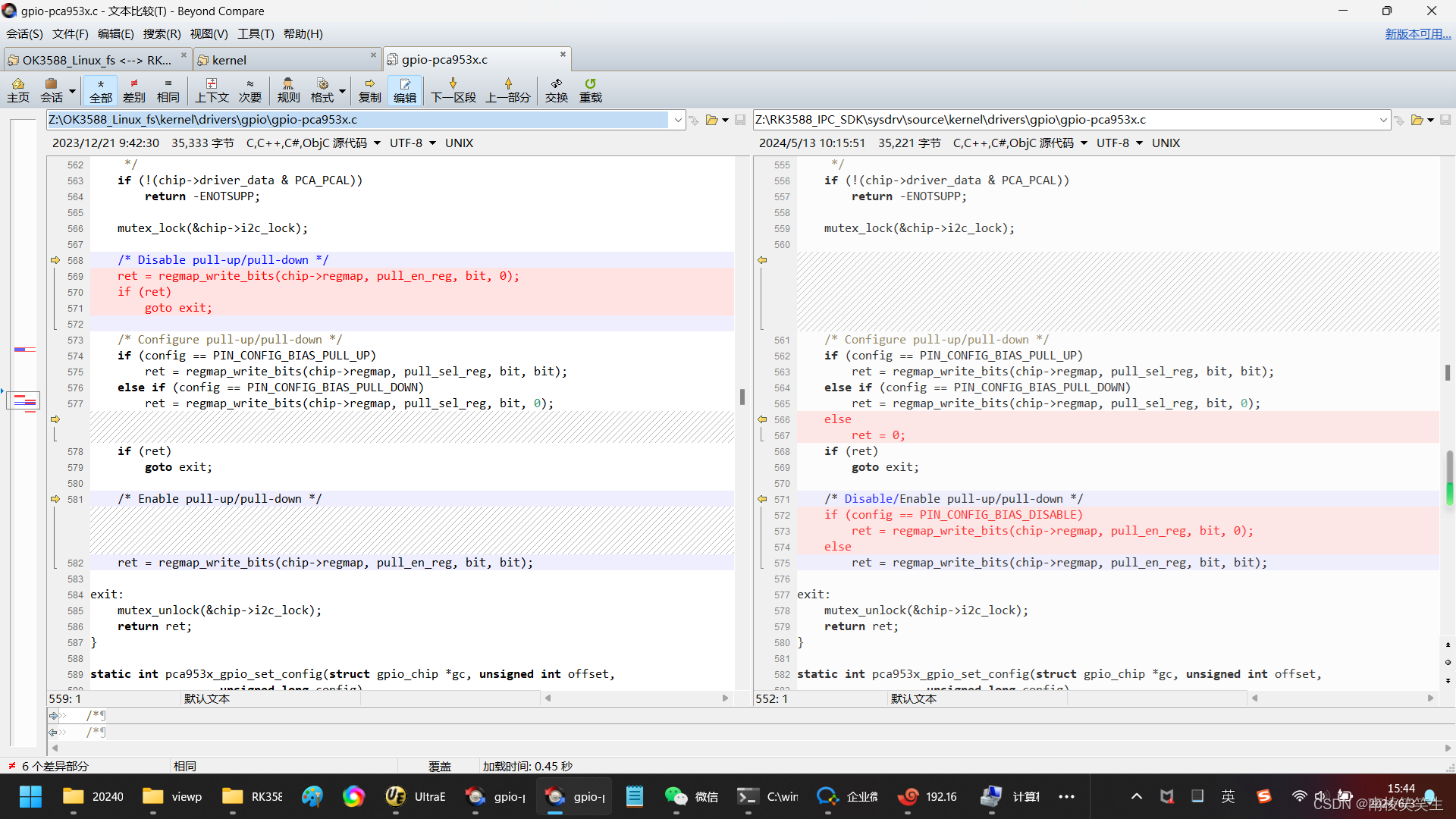

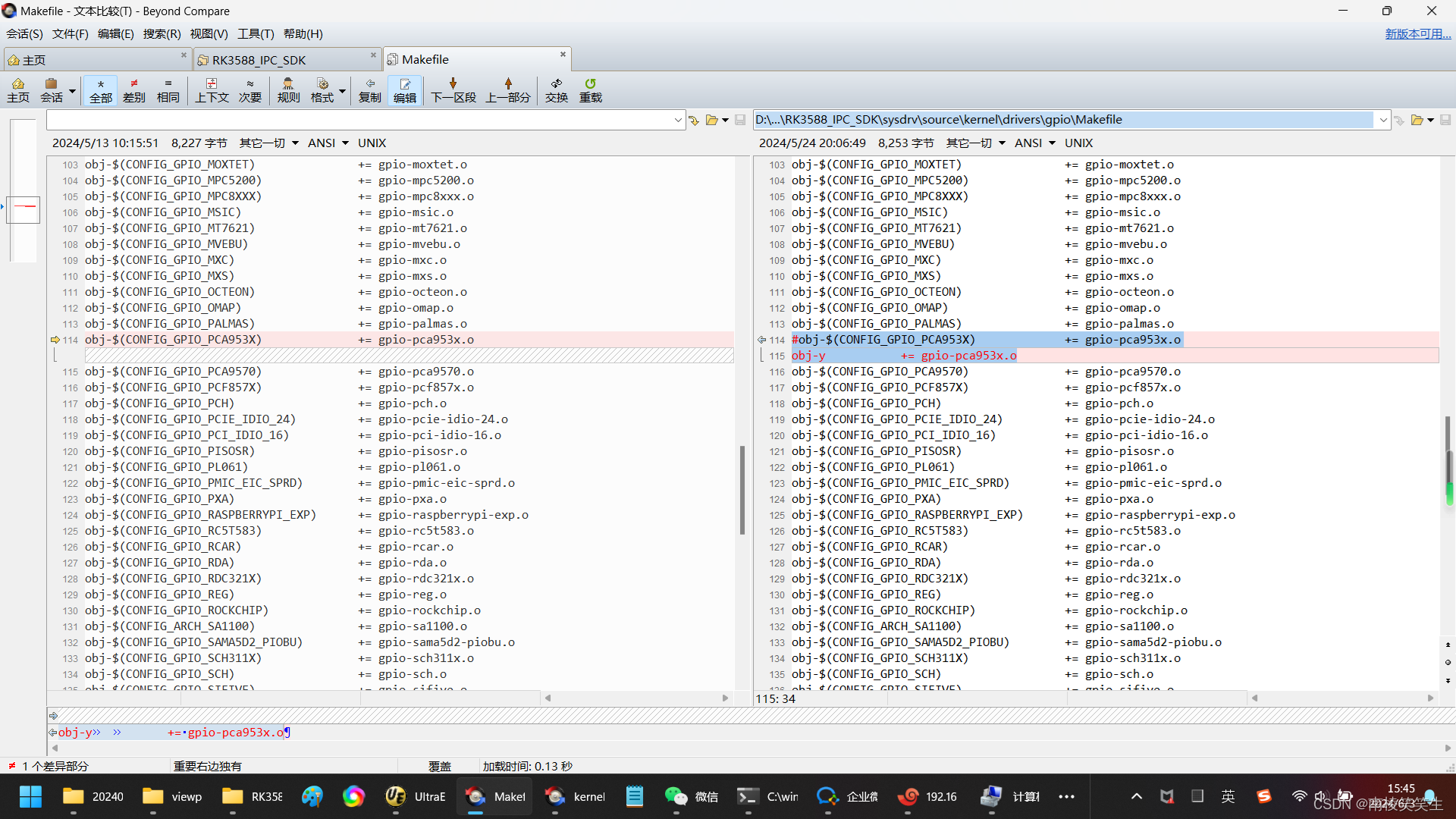

2、有不同点,为了省事,直接使用飞凌的覆盖。同时在Makefile中强制打开pca953x!

Z:\RK3588_IPC_SDK\sysdrv\source\kernel\drivers\gpio\gpio-pca953x.c

Z:\RK3588_IPC_SDK\sysdrv\source\kernel\drivers\gpio\gpio-pca953x.c

Z:\RK3588_IPC_SDK\sysdrv\source\kernel\drivers\gpio\Makefile

obj-$(CONFIG_GPIO_OCTEON) += gpio-octeon.o

obj-$(CONFIG_GPIO_OMAP) += gpio-omap.o

obj-$(CONFIG_GPIO_PALMAS) += gpio-palmas.o

#obj-$(CONFIG_GPIO_PCA953X) += gpio-pca953x.o

obj-y += gpio-pca953x.o

obj-$(CONFIG_GPIO_PCA9570) += gpio-pca9570.o

obj-$(CONFIG_GPIO_PCF857X) += gpio-pcf857x.o

obj-$(CONFIG_GPIO_PCH) += gpio-pch.o

【不改之类,编译不过,DTS里面会有变量未定义的!好不容易百度找到了!】

Z:\OK3588_Linux_fs\kernel\include\dt-bindings\pinctrl\rockchip.h

Z:\RK3588_IPC_SDK\sysdrv\source\kernel\include\dt-bindings\pinctrl\rockchip.h

/* SPDX-License-Identifier: GPL-2.0-or-later */

/*

* Header providing constants for Rockchip pinctrl bindings.

*

* Copyright (c) 2013 MundoReader S.L.

* Author: Heiko Stuebner <heiko@sntech.de>

*/

#ifndef __DT_BINDINGS_ROCKCHIP_PINCTRL_H__

#define __DT_BINDINGS_ROCKCHIP_PINCTRL_H__

#define RK_PA0 0

#define RK_PA1 1

#define RK_PA2 2

#define RK_PA3 3

#define RK_PA4 4

#define RK_PA5 5

#define RK_PA6 6

#define RK_PA7 7

#define RK_PB0 8

#define RK_PB1 9

#define RK_PB2 10

#define RK_PB3 11

#define RK_PB4 12

#define RK_PB5 13

#define RK_PB6 14

#define RK_PB7 15

#define RK_PC0 16

#define RK_PC1 17

#define RK_PC2 18

#define RK_PC3 19

#define RK_PC4 20

#define RK_PC5 21

#define RK_PC6 22

#define RK_PC7 23

#define RK_PD0 24

#define RK_PD1 25

#define RK_PD2 26

#define RK_PD3 27

#define RK_PD4 28

#define RK_PD5 29

#define RK_PD6 30

#define RK_PD7 31

#define RK_FUNC_GPIO 0

#define EXTIO_GPIO_P00 0

#define EXTIO_GPIO_P01 1

#define EXTIO_GPIO_P02 2

#define EXTIO_GPIO_P03 3

#define EXTIO_GPIO_P04 4

#define EXTIO_GPIO_P05 5

#define EXTIO_GPIO_P06 6

#define EXTIO_GPIO_P07 7

#define EXTIO_GPIO_P10 8

#define EXTIO_GPIO_P11 9

#define EXTIO_GPIO_P12 10

#define EXTIO_GPIO_P13 11

#define EXTIO_GPIO_P14 12

#define EXTIO_GPIO_P15 13

#define EXTIO_GPIO_P16 14

#define EXTIO_GPIO_P17 15

#define EXTIO_GPIO_P20 16

#define EXTIO_GPIO_P21 17

#define EXTIO_GPIO_P22 18

#define EXTIO_GPIO_P23 19

#define EXTIO_GPIO_P24 20

#define EXTIO_GPIO_P25 21

#define EXTIO_GPIO_P26 22

#define EXTIO_GPIO_P27 23

#endif

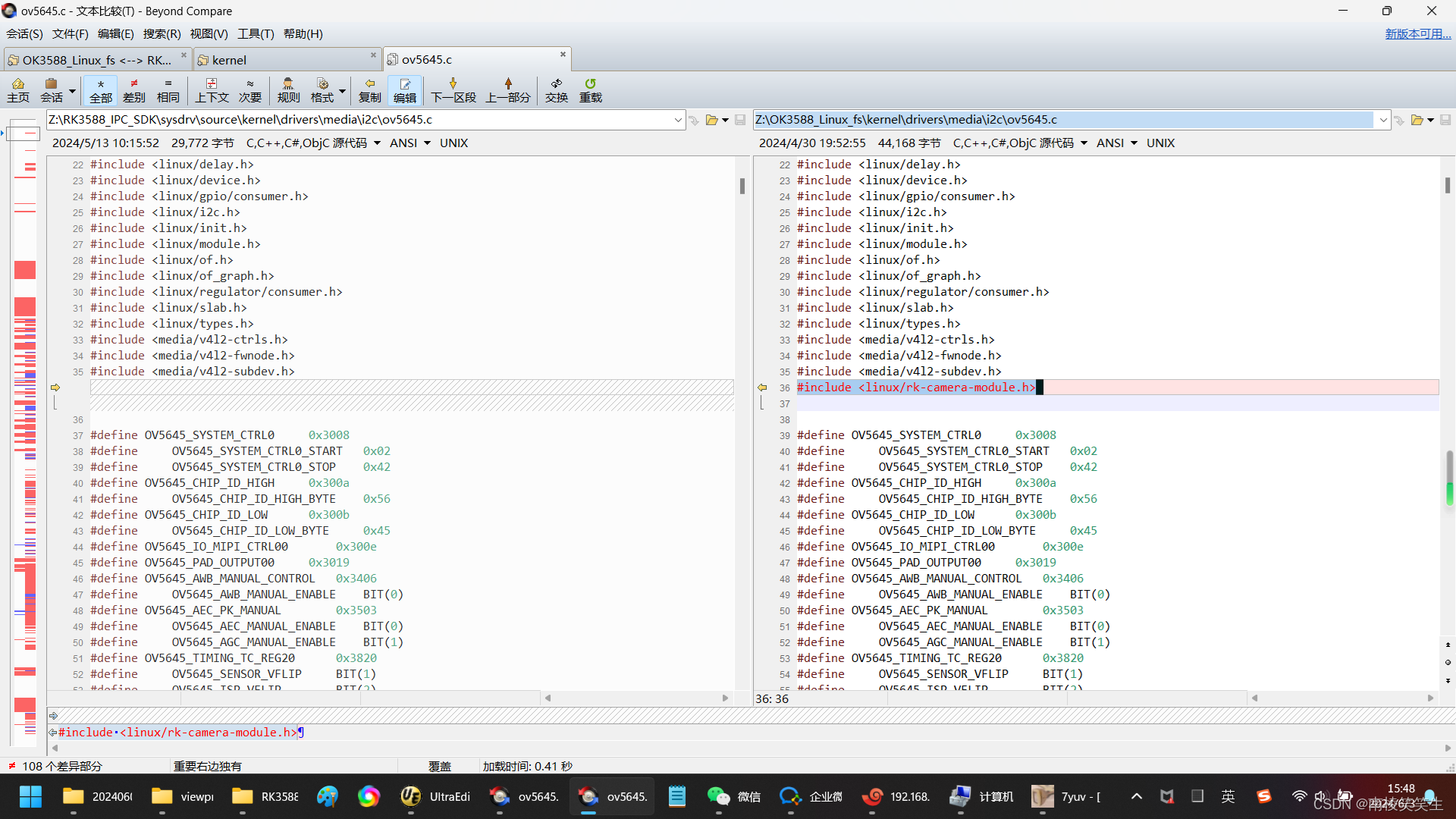

3、不用看了,ov5645.c差异太大了。根据经验,直接使用飞凌的ov5645的驱动替换掉了!

Z:\OK3588_Linux_fs\kernel\drivers\media\i2c\ov5645.c

Z:\RK3588_IPC_SDK\sysdrv\source\kernel\drivers\media\i2c\ov5645.c

【由于ov5645.c默认不编译,为了省事,我直接让它强制打开了!】

Z:\RK3588_IPC_SDK\sysdrv\source\kernel\drivers\media\i2c\Makefile

obj-$(CONFIG_VIDEO_OS02G10) += os02g10.o

obj-$(CONFIG_VIDEO_OS03B10) += os03b10.o

obj-$(CONFIG_VIDEO_OS04A10) += os04a10.o

obj-$(CONFIG_VIDEO_OS05A20) += os05a20.o

obj-$(CONFIG_VIDEO_OS08A20) += os08a20.o

obj-$(CONFIG_VIDEO_OV02B10) += ov02b10.o

obj-$(CONFIG_VIDEO_OV02K10) += ov02k10.o

obj-$(CONFIG_VIDEO_OV2640) += ov2640.o

obj-$(CONFIG_VIDEO_OV2680) += ov2680.o

obj-$(CONFIG_VIDEO_OV2685) += ov2685.o

obj-$(CONFIG_VIDEO_OV2718) += ov2718.o

obj-$(CONFIG_VIDEO_OV2740) += ov2740.o

obj-$(CONFIG_VIDEO_OV4686) += ov4686.o

obj-$(CONFIG_VIDEO_OV4688) += ov4688.o

obj-$(CONFIG_VIDEO_OV4689) += ov4689.o

obj-$(CONFIG_VIDEO_OV50C40) += ov50c40.o

obj-$(CONFIG_VIDEO_OV5640) += ov5640.o

#obj-$(CONFIG_VIDEO_OV5645) += ov5645.o

obj-y += ov5645.o

obj-$(CONFIG_VIDEO_OV5647) += ov5647.o

obj-$(CONFIG_VIDEO_OV5670) += ov5670.o

obj-$(CONFIG_VIDEO_OV5675) += ov5675.o

obj-$(CONFIG_VIDEO_OV5695) += ov5695.o

obj-$(CONFIG_VIDEO_OV6650) += ov6650.o

obj-$(CONFIG_VIDEO_OV7251) += ov7251.o

obj-$(CONFIG_VIDEO_OV7640) += ov7640.o

obj-$(CONFIG_VIDEO_OV7670) += ov7670.o

obj-$(CONFIG_VIDEO_OV772X) += ov772x.o

obj-$(CONFIG_VIDEO_OV7740) += ov7740.o

obj-$(CONFIG_VIDEO_OV8856) += ov8856.o

obj-$(CONFIG_VIDEO_OV8858) += ov8858.o

obj-$(CONFIG_VIDEO_OV9281) += ov9281.o

obj-$(CONFIG_VIDEO_OV9640) += ov9640.o

obj-$(CONFIG_VIDEO_OV9650) += ov9650.o

obj-$(CONFIG_VIDEO_OV12D2Q) += ov12d2q.o

obj-$(CONFIG_VIDEO_OV13850) += ov13850.o

obj-$(CONFIG_VIDEO_OV13855) += ov13855.o

obj-$(CONFIG_VIDEO_OV13858) += ov13858.o

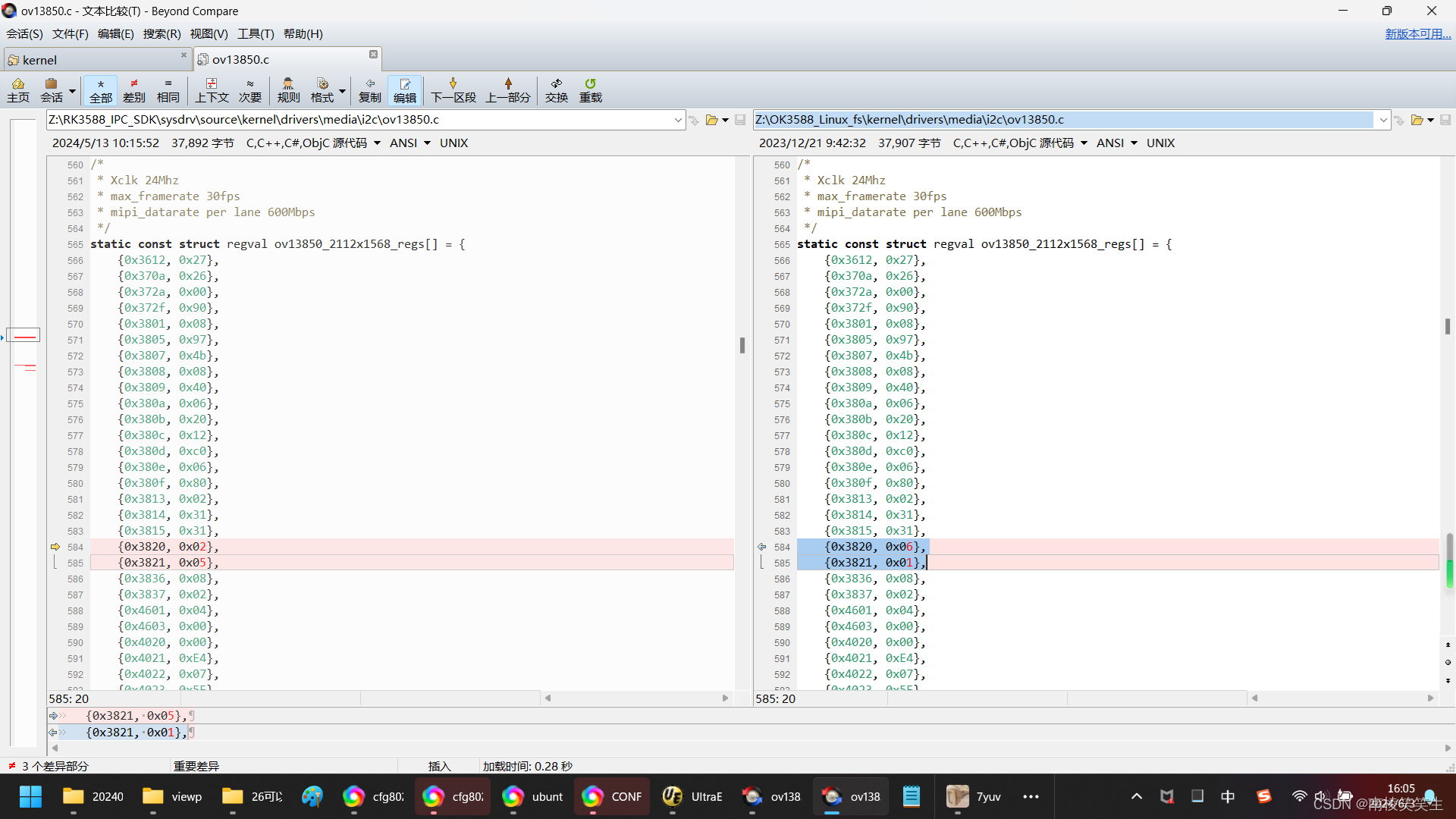

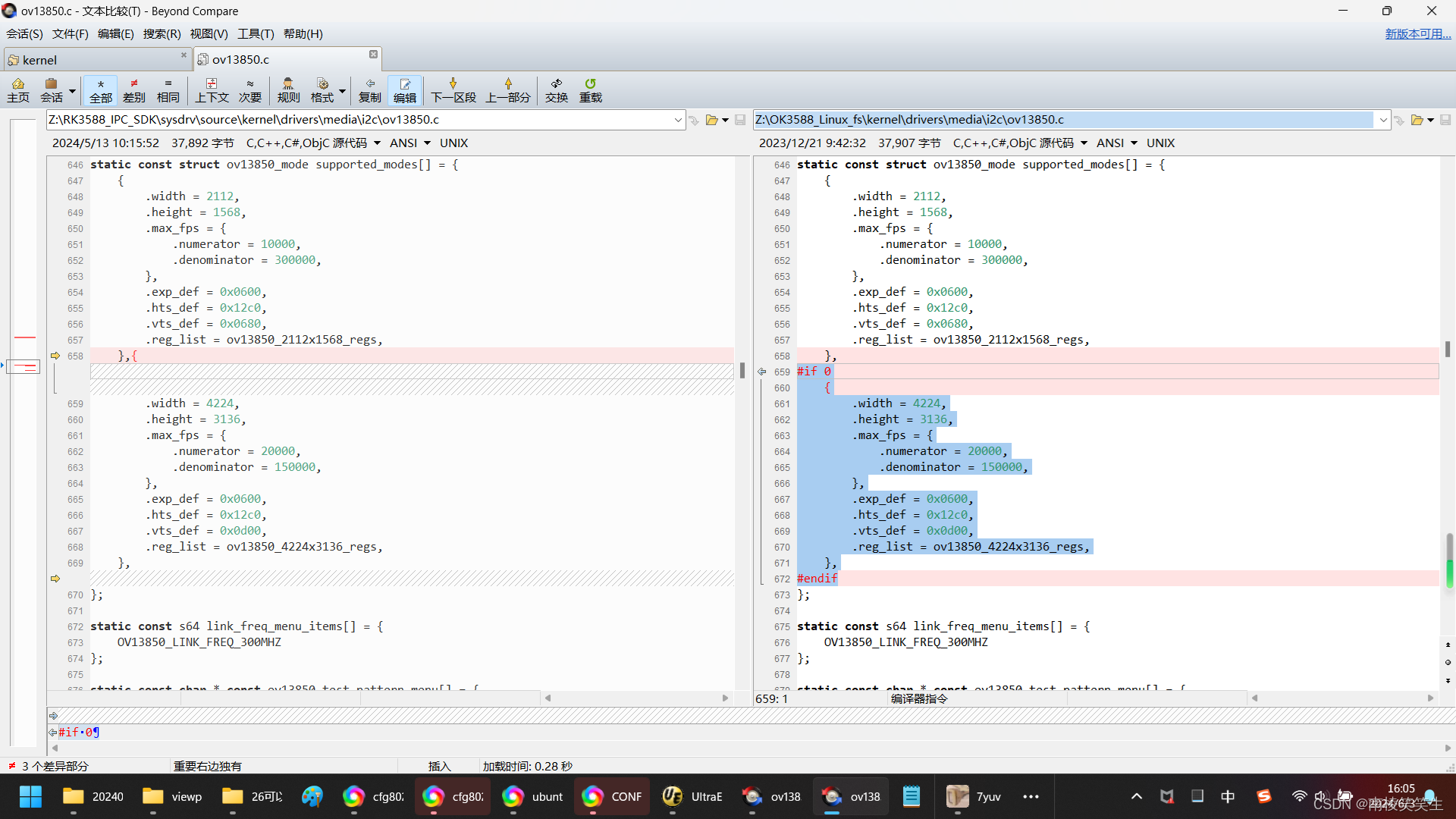

4、可能ov13850只使用了2lane,或者实际量产的时候达不到设计要求,不能完美的输出4K分辨率。

针对DATASHEET进行了减配!要想比较理想地进行4K录像,可以上同门OV13855了。

Z:\OK3588_Linux_fs\kernel\drivers\media\i2c\ov13850.c

Z:\RK3588_IPC_SDK\sysdrv\source\kernel\drivers\media\i2c\ov13850.c

/*

* Xclk 24Mhz

* max_framerate 30fps

* mipi_datarate per lane 600Mbps

*/

static const struct regval ov13850_2112x1568_regs[] = {

{0x3612, 0x27},

{0x370a, 0x26},

{0x372a, 0x00},

{0x372f, 0x90},

{0x3801, 0x08},

{0x3805, 0x97},

{0x3807, 0x4b},

{0x3808, 0x08},

{0x3809, 0x40},

{0x380a, 0x06},

{0x380b, 0x20},

{0x380c, 0x12},

{0x380d, 0xc0},

{0x380e, 0x06},

{0x380f, 0x80},

{0x3813, 0x02},

{0x3814, 0x31},

{0x3815, 0x31},

{0x3820, 0x06},

{0x3821, 0x01},

{0x3836, 0x08},

{0x3837, 0x02},

{0x4601, 0x04},

{0x4603, 0x00},

{0x4020, 0x00},

{0x4021, 0xE4},

{0x4022, 0x07},

{0x4023, 0x5F},

{0x4024, 0x08},

{0x4025, 0x44},

{0x4026, 0x08},

{0x4027, 0x47},

{0x4603, 0x01},

{0x5401, 0x61},

{0x5405, 0x40},

{REG_NULL, 0x00},

};

static const struct ov13850_mode supported_modes[] = {

{

.width = 2112,

.height = 1568,

.max_fps = {

.numerator = 10000,

.denominator = 300000,

},

.exp_def = 0x0600,

.hts_def = 0x12c0,

.vts_def = 0x0680,

.reg_list = ov13850_2112x1568_regs,

},

#if 0

{

.width = 4224,

.height = 3136,

.max_fps = {

.numerator = 20000,

.denominator = 150000,

},

.exp_def = 0x0600,

.hts_def = 0x12c0,

.vts_def = 0x0d00,

.reg_list = ov13850_4224x3136_regs,

},

#endif

};

参考资料:

OV5645的抓图指令:

v4l2-ctl -d /dev/video64 \

--set-fmt-video=width=640,height=480,pixelformat=NV12 \

--stream-mmap=3 \

--stream-skip=3 \

--stream-to=/tmp/nv12_2.bmp \

--stream-count=1 \

--stream-poll

百度:RK3588 EXTIO_GPIO_P01 dtsi:79.30-31 syntax error

pca953x 2-0023: interrupt support not compiled in

TCA6524 EXTIO_GPIO_P01

L6524 芯片

obj-y += ov5645.o

https://blog.csdn.net/qq_41544116/article/details/131863063

rk3588 编译 linux uboot(使用github公版源码、debian rootfs)和烧录(sd、emmc)

配置文件和设备树

使用板卡厂商提供的设备树,这里用的是飞凌的 ok3588c

FET3588-C.dtsi、OK3588-C-Camera.dtsi、OK3588-C-common.dtsi、OK3588-C-Linux.dts 放到 arch/arm64/boot/dts/rockchip 里

电源管理芯片的设备树有单双之分,不能通用。单:rk3588-rk806-single.dtsi;双:rk3588-rk806-dual.dtsi

修改

OK3588-C-Camera.dtsi

EXTIO_GPIO_P06 改为 RK_PA6

EXTIO_GPIO_P07 改为 RK_PA7

EXTIO_GPIO_P10 改为 RK_PB0

EXTIO_GPIO_P11 改为 RK_PB1

EXTIO_GPIO_P05 改为 RK_PA5

EXTIO_GPIO_P04 改为 RK_PA4

EXTIO_GPIO_P01 改为 RK_PA1

EXTIO_GPIO_P00 改为 RK_PA0

EXTIO_GPIO_P03 改为 RK_PA3

EXTIO_GPIO_P02 改为 RK_PA2

从板卡厂商整合包里的 kernel/include/dt-bindings/pinctrl/rockchip.h 得出。这是 TCA6424ARGJR 芯片,用于 i2c 扩展 io,比如 EXTIO_GPIO_P06 是扩展出的 io 的序号,用这个需要修改 rockchip.h 文件,这里用已有 RK_PA6 代替序号,RK_PA6 也是序号

OK3588-C-common.dtsi

dsi0_in_vp2 和紧贴该节点上面的 dsi0

两个节点里的 status 都赋值为 okay // 这样 dsi0 的 mipi 屏就能显示了

i2c2 里的 ft5x06_dsi0

取消注释 interrupt-parent、interrupts,注释 irq-gpio // 驱动代码不同导致的修改

i2c2 里的 gt9xx_dsi0

status 赋值为 disabled // ft5x06_dsi0 和 gt9xx_dsi0 使用同一中断脚,所以节点不能都开启,这里开启的是 ft5x06_dsi0,所以 gt9xx_dsi0 就要关闭

i2c2 里的触摸芯片对应的是 dsi0 接口,如果屏幕接 dsi1 上就用同样的方法修改 i2c5

OK3588-C-Linux.dts

如果要烧录到 sd 卡里,需要更改 bootargs,修改 / 里的 chosen 节点

bootargs 值的 root 赋值为 /dev/mmcblk0p4 // mmcblk0 是设备号,从 0 开始,p4 是分区 4,从 1 开始

/ 里的 fiq_debugger 节点

rockchip,baudrate 赋值为 1500000 // 串口波特率

arch/arm64/boot/dts/rockchip/Makefile

删除所有内容并添加 dtb-$(CONFIG_ARCH_ROCKCHIP) += OK3588-C-Linux.dtb

boot.its

fdt 节点

data = /incbin/("arch/arm64/boot/dts/rockchip/OK3588-C-Linux.dtb"); // 文件的在电脑的路径,工具会去这里找

arch = "arm64";

kernel 节点

data = /incbin/("arch/arm64/boot/Image.gz");

arch = "arm64";

compression = "gzip";

如需手动制作 .gz 镜像:cat Image | gzip -n -f -9 > Image.gz

删除 resource 节点

configurations 节点

删除 conf 里的 multi 部分

删除 conf/sign-images 里的 multi 部分

编译

export ARCH=arm64 CROSS_COMPILE=aarch64-linux-gnu- // 新的终端都要先执行一次

make rockchip_linux_defconfig rk3588_linux.config

make menuconfig // rockchip 提供的公有配置也能启动,额外的驱动比如 ft5x06 的驱动就要在这自行开启。ft5x06 的位置在 Device Drivers/Input device support/Touchscreens/EDT FocalTech FT5x06 I2C Touchscreen support

make -j16

如果编译报 ...error, forbidden warning,就在 scripts/gcc-wrapper.py 中注释掉 run_gcc() 里的 interpret_warning()

boot.itb

../u-boot/tools/mkimage -f boot.its -E -p 0x800 boot.itb

Z:\OK3588_Linux_fs\kernel\arch\arm64\boot\dts\rockchip\OK3588-C-Camera.dtsi

// SPDX-License-Identifier: (GPL-2.0+ OR MIT)

/*

* Copyright (c) 2022 Forlinx Co., Ltd.

*

* rkisp0 --> rkisp0_vir0/rkisp0_vir1/rkisp0_vir2/rkisp0_vir3

* rkisp1 --> rkisp1_vir0/rkisp1_vir1/rkisp1_vir2/rkisp1_vir3

* rkcif_mipi_lvds --> rkcif_mipi_lvds[0-4]_sditf

* mipicamera0 --> csi2_dcphy0 --> mipi0_csi2 -->rkcif_mipi_lvds --> rkcif_mipi_lvds_sditf --> rkisp0_vir0

* mipicamera1 --> csi2_dcphy1 --> mipi1_csi2 -->rkcif_mipi_lvds1 --> rkcif_mipi_lvds1_sditf --> rkisp0_vir1

* csi2_dphy0 or (csi2_dphy1?¢csi2_dphy2) dphy0

* csi2_dphy3 or (csi2_dphy4?¢csi2_dphy5) dphy1

* mipicamera2 --> csi2_dphy1 --> mipi2_csi2 -->rkcif_mipi_lvds2 -->rkcif_mipi_lvds2_sditf --> rkisp0_vir2

* mipicamera3 --> csi2_dphy2 --> mipi3_csi2 -->rkcif_mipi_lvds3 -->rkcif_mipi_lvds3_sditf --> rkisp1_vir0

* mipicamera4 --> csi2_dphy4 --> mipi4_csi2 -->rkcif_mipi_lvds4 -->rkcif_mipi_lvds4_sditf --> rkisp1_vir1

* mipicamera5 --> csi2_dphy5 --> mipi5_csi2 -->rkcif_mipi_lvds5 -->rkcif_mipi_lvds5_sditf --> rkisp1_vir2

* mipicamera6 --> rkcif_dvp ---> rkcif_dvp_sditf

*/

/ {

ext_cam_clk: external-camera-clock {

compatible = "fixed-clock";

clock-frequency = <24000000>;

clock-output-names = "CLK_CAMERA_24MHZ";

#clock-cells = <0>;

};

};

&rkcif {

status = "okay";

};

&rkcif_mmu {

status = "okay";

};

//************************************************

//*** CAM1 OV13850 Configuration description ***

//************************************************

&mipi_dcphy0 {

status = "okay";

};

&rkisp0 {

status = "okay";

};

&isp0_mmu {

status = "okay";

};

&i2c3 {

status = "okay";

clock-frequency = <400000>;

vm149c_0: vm149c@0c {

compatible = "silicon touch,vm149c";

status = "okay";

reg = <0x0c>;

rockchip,camera-module-index = <0>;

rockchip,camera-module-facing = "back";

};

cam1_ov13850: cam1_ov13850@10 {

compatible = "ovti,ov13850";

status = "okay";

reg = <0x10>;

clocks = <&ext_cam_clk>;

clock-names = "xvclk";

//pwdn-gpios = <&extio EXTIO_GPIO_P01 GPIO_ACTIVE_HIGH>;

//reset-gpios = <&extio EXTIO_GPIO_P00 GPIO_ACTIVE_HIGH>;

rockchip,camera-module-index = <0>;

rockchip,camera-module-facing = "back";

rockchip,camera-module-name = "forlinx";

rockchip,camera-module-lens-name = "default";

lens-focus = <&vm149c_0>;

port {

cam1_ov13850_out: endpoint {

remote-endpoint = <&mipi_in_0_ucam1>;

data-lanes = <1 2>;

};

};

};

};

&csi2_dcphy0 {

status = "okay";

ports {

#address-cells = <1>;

#size-cells = <0>;

port@0 {

reg = <0>;

#address-cells = <1>;

#size-cells = <0>;

mipi_in_0_ucam1: endpoint@1 {

reg = <1>;

remote-endpoint = <&cam1_ov13850_out>;

data-lanes = <1 2>;

};

};

port@1 {

reg = <1>;

#address-cells = <1>;

#size-cells = <0>;

csidcphy0_out: endpoint@0 {

reg = <0>;

remote-endpoint = <&mipi0_csi2_input>;

};

};

};

};

&mipi0_csi2 {

status = "okay";

ports {

#address-cells = <1>;

#size-cells = <0>;

port@0 {

reg = <0>;

#address-cells = <1>;

#size-cells = <0>;

mipi0_csi2_input: endpoint@1 {

reg = <1>;

remote-endpoint = <&csidcphy0_out>;

};

};

port@1 {

reg = <1>;

#address-cells = <1>;

#size-cells = <0>;

mipi0_csi2_output: endpoint@0 {

reg = <0>;

remote-endpoint = <&cif_mipi_lvds0>;

};

};

};

};

&rkcif_mipi_lvds {

status = "okay";

port {

cif_mipi_lvds0: endpoint {

remote-endpoint = <&mipi0_csi2_output>;

};

};

};

&rkcif_mipi_lvds_sditf {

status = "okay";

port {

mipi_lvds_sditf: endpoint {

remote-endpoint = <&isp0_vir0>;

};

};

};

&rkisp0_vir0 {

status = "okay";

port {

#address-cells = <1>;

#size-cells = <0>;

isp0_vir0: endpoint@0 {

reg = <0>;

remote-endpoint = <&mipi_lvds_sditf>;

};

};

};

//************************************************

//*** CAM2 OV13850 Configuration description ***

//************************************************

&mipi_dcphy1 {

status = "okay";

};

&i2c4 {

status = "okay";

clock-frequency = <400000>;

vm149c_1: vm149c@0c {

compatible = "silicon touch,vm149c";

status = "okay";

reg = <0x0c>;

rockchip,camera-module-index = <1>;

rockchip,camera-module-facing = "back";

};

cam2_ov13850: cam2_ov13850@10 {

compatible = "ovti,ov13850";

status = "okay";

reg = <0x10>;

clocks = <&ext_cam_clk>;

clock-names = "xvclk";

//pwdn-gpios = <&extio EXTIO_GPIO_P03 GPIO_ACTIVE_HIGH>;

//reset-gpios = <&extio EXTIO_GPIO_P02 GPIO_ACTIVE_HIGH>;

rockchip,camera-module-index = <1>;

rockchip,camera-module-facing = "front";

rockchip,camera-module-name = "forlinx";

rockchip,camera-module-lens-name = "default";

lens-focus = <&vm149c_1>;

port {

cam2_ov13850_out: endpoint {

remote-endpoint = <&mipi_in_1_ucam2>;

data-lanes = <1 2>;

};

};

};

};

&csi2_dcphy1 {

status = "okay";

ports {

#address-cells = <1>;

#size-cells = <0>;

port@0 {

reg = <0>;

#address-cells = <1>;

#size-cells = <0>;

mipi_in_1_ucam2: endpoint@1 {

reg = <1>;

remote-endpoint = <&cam2_ov13850_out>;

data-lanes = <1 2>;

};

};

port@1 {

reg = <1>;

#address-cells = <1>;

#size-cells = <0>;

csidcphy1_out: endpoint@0 {

reg = <0>;

remote-endpoint = <&mipi1_csi2_input>;

};

};

};

};

&mipi1_csi2 {

status = "okay";

ports {

#address-cells = <1>;

#size-cells = <0>;

port@0 {

reg = <0>;

#address-cells = <1>;

#size-cells = <0>;

mipi1_csi2_input: endpoint@1 {

reg = <1>;

remote-endpoint = <&csidcphy1_out>;

};

};

port@1 {

reg = <1>;

#address-cells = <1>;

#size-cells = <0>;

mipi1_csi2_output: endpoint@0 {

reg = <0>;

remote-endpoint = <&cif_mipi_lvds1>;

};

};

};

};

&rkcif_mipi_lvds1 {

status = "okay";

port {

cif_mipi_lvds1: endpoint {

remote-endpoint = <&mipi1_csi2_output>;

};

};

};

&rkcif_mipi_lvds1_sditf {

status = "okay";

port {

mipi_lvds1_sditf: endpoint {

remote-endpoint = <&isp0_vir1>;

};

};

};

&rkisp0_vir1 {

status = "okay";

port {

#address-cells = <1>;

#size-cells = <0>;

isp0_vir1: endpoint@0 {

reg = <0>;

remote-endpoint = <&mipi_lvds1_sditf>;

};

};

};

//************************************************

//*** CAM3 OV5645 Configuration Description ****

//************************************************

&csi2_dphy0_hw {

status = "okay";

};

&i2c7 {

status = "okay";

clock-frequency = <400000>;

cam3_ov5645: cam3_ov5645@3c {

compatible = "ovti,ov5645";

status = "okay";

reg = <0x3c>;

clocks = <&ext_cam_clk>;

clock-names = "xclk";

clock-frequency = <24000000>;

//enable-gpios = <&extio EXTIO_GPIO_P05 GPIO_ACTIVE_HIGH>;

//reset-gpios = <&extio EXTIO_GPIO_P04 GPIO_ACTIVE_LOW>;

rockchip,camera-module-index = <0>;

rockchip,camera-module-facing = "back";

rockchip,camera-module-name = "NC";

rockchip,camera-module-lens-name = "NC";

port {

cam3_ov5645_out: endpoint {

remote-endpoint = <&mipi_in_ucam3>;

data-lanes = <1 2>;

};

};

};

};

&csi2_dphy0 {

status = "okay";

ports {

#address-cells = <1>;

#size-cells = <0>;

port@0 {

reg = <0>;

#address-cells = <1>;

#size-cells = <0>;

mipi_in_ucam3: endpoint@1 {

reg = <1>;

remote-endpoint = <&cam3_ov5645_out>;

data-lanes = <1 2>;

};

};

port@1 {

reg = <1>;

#address-cells = <1>;

#size-cells = <0>;

mipi2_csi2_mipicsi0_out0: endpoint@0 {

reg = <0>;

remote-endpoint = <&mipi2_csi2_input>;

};

};

};

};

&mipi2_csi2 {

status = "okay";

ports {

#address-cells = <1>;

#size-cells = <0>;

port@0 {

reg = <0>;

#address-cells = <1>;

#size-cells = <0>;

mipi2_csi2_input: endpoint@1 {

reg = <1>;

remote-endpoint = <&mipi2_csi2_mipicsi0_out0>;

};

};

port@1 {

reg = <1>;

#address-cells = <1>;

#size-cells = <0>;

mipi2_csi2_output: endpoint@0 {

reg = <0>;

remote-endpoint = <&cif_mipi_lvds2>;

};

};

};

};

&rkcif_mipi_lvds2 {

status = "okay";

port {

cif_mipi_lvds2: endpoint {

remote-endpoint = <&mipi2_csi2_output>;

};

};

};

&rkcif_mipi_lvds2_sditf {

status = "disabled";

};

//************************************************

//*** CAM4 OV5645 Configuration Description ****

//************************************************

&csi2_dphy1_hw {

status = "okay";

};

&i2c3 {

status = "okay";

cam4_ov5645: cam4_ov5645@3c {

status = "okay";

compatible = "ovti,ov5645";

reg = <0x3c>;

clocks = <&ext_cam_clk>;

clock-names = "xclk";

clock-frequency = <24000000>;

//reset-gpios = <&extio EXTIO_GPIO_P06 GPIO_ACTIVE_LOW>;

//enable-gpios = <&extio EXTIO_GPIO_P07 GPIO_ACTIVE_HIGH>;

rockchip,camera-module-index = <1>;

rockchip,camera-module-facing = "front";

rockchip,camera-module-name = "NC";

rockchip,camera-module-lens-name = "NC";

port {

cam4_ov5645_out: endpoint {

remote-endpoint = <&mipi_in_ucam4>;

data-lanes = <1 2>;

};

};

};

};

&csi2_dphy4 {

status = "okay";

ports {

#address-cells = <1>;

#size-cells = <0>;

port@0 {

reg = <0>;

#address-cells = <1>;

#size-cells = <0>;

mipi_in_ucam4: endpoint@1 {

reg = <1>;

remote-endpoint = <&cam4_ov5645_out>;

data-lanes = <1 2>;

};

};

port@1 {

reg = <1>;

#address-cells = <1>;

#size-cells = <0>;

mipi4_csi2_csidphy1_out0: endpoint@0 {

reg = <0>;

remote-endpoint = <&mipi4_csi2_input>;

};

};

};

};

&mipi4_csi2 {

status = "okay";

ports {

#address-cells = <1>;

#size-cells = <0>;

port@0 {

reg = <0>;

#address-cells = <1>;

#size-cells = <0>;

mipi4_csi2_input: endpoint@1 {

reg = <1>;

remote-endpoint = <&mipi4_csi2_csidphy1_out0>;

};

};

port@1 {

reg = <1>;

#address-cells = <1>;

#size-cells = <0>;

mipi4_csi2_output: endpoint@0 {

reg = <0>;

remote-endpoint = <&cif_mipi_in4>;

};

};

};

};

&rkcif_mipi_lvds4 {

status = "okay";

port {

cif_mipi_in4: endpoint {

remote-endpoint = <&mipi4_csi2_output>;

};

};

};

&rkcif_mipi_lvds4_sditf {

status = "disabled";

};

//************************************************

//*** CAM5 OV5645 Configuration Description ****

//************************************************

&i2c4 {

status = "okay";

cam5_ov5645: cam5_ov5645@3c {

status = "okay";

compatible = "ovti,ov5645";

reg = <0x3c>;

clocks = <&ext_cam_clk>;

clock-names = "xclk";

clock-frequency = <24000000>;

//reset-gpios = <&extio EXTIO_GPIO_P10 GPIO_ACTIVE_LOW>;

//enable-gpios = <&extio EXTIO_GPIO_P11 GPIO_ACTIVE_HIGH>;

rockchip,camera-module-index = <2>;

rockchip,camera-module-facing = "front";

rockchip,camera-module-name = "NC";

rockchip,camera-module-lens-name = "NC";

port {

cam5_ov5645_out: endpoint {

remote-endpoint = <&mipi_in_ucam5>;

data-lanes = <1 2>;

};

};

};

};

&csi2_dphy5 {

status = "okay";

ports {

#address-cells = <1>;

#size-cells = <0>;

port@0 {

reg = <0>;

#address-cells = <1>;

#size-cells = <0>;

mipi_in_ucam5: endpoint@1 {

reg = <1>;

remote-endpoint = <&cam5_ov5645_out>;

data-lanes = <1 2>;

};

};

port@1 {

reg = <1>;

#address-cells = <1>;

#size-cells = <0>;

mipi5_csi2_csidphy1_out1: endpoint@0 {

reg = <0>;

remote-endpoint = <&mipi5_csi2_input>;

};

};

};

};

&mipi5_csi2 {

status = "okay";

ports {

#address-cells = <1>;

#size-cells = <0>;

port@0 {

reg = <0>;

#address-cells = <1>;

#size-cells = <0>;

mipi5_csi2_input: endpoint@1 {

reg = <1>;

remote-endpoint = <&mipi5_csi2_csidphy1_out1>;

};

};

port@1 {

reg = <1>;

#address-cells = <1>;

#size-cells = <0>;

mipi5_csi2_output: endpoint@0 {

reg = <0>;

remote-endpoint = <&cif_mipi_in5>;

};

};

};

};

&rkcif_mipi_lvds5 {

status = "okay";

port {

cif_mipi_in5: endpoint {

remote-endpoint = <&mipi5_csi2_output>;

};

};

};

&rkcif_mipi_lvds5_sditf {

status = "disabled";

};

Z:\RK3588_IPC_SDK\sysdrv\source\kernel\arch\arm64\boot\dts\rockchip\rk3588-nvr-demo-v10-cam-4x.dtsi

// SPDX-License-Identifier: (GPL-2.0+ OR MIT)

/*

* Copyright (c) 2021 Rockchip Electronics Co., Ltd.

*

*/

/ {

vcc_mipicsi0: vcc-mipicsi0-regulator {

compatible = "regulator-fixed";

gpio = <&gpio1 RK_PB1 GPIO_ACTIVE_HIGH>;

pinctrl-names = "default";

pinctrl-0 = <&mipicsi0_pwr>;

regulator-name = "vcc_mipicsi0";

enable-active-high;

};

vcc_mipicsi1: vcc-mipicsi1-regulator {

compatible = "regulator-fixed";

gpio = <&gpio1 RK_PB2 GPIO_ACTIVE_HIGH>;

pinctrl-names = "default";

pinctrl-0 = <&mipicsi1_pwr>;

regulator-name = "vcc_mipicsi1";

enable-active-high;

};

};

&pinctrl {

cam {

mipicsi0_pwr: mipicsi0-pwr {

rockchip,pins =

<1 RK_PB1 RK_FUNC_GPIO &pcfg_pull_none>;

};

mipicsi1_pwr: mipicsi1-pwr {

rockchip,pins =

<1 RK_PB2 RK_FUNC_GPIO &pcfg_pull_none>;

};

};

};

&csi2_dphy0_hw {

status = "okay";

};

&csi2_dphy1_hw {

status = "okay";

};

&csi2_dphy1 {

status = "okay";

ports {

#address-cells = <1>;

#size-cells = <0>;

port@0 {

reg = <0>;

#address-cells = <1>;

#size-cells = <0>;

mipi_in_ucam2: endpoint@1 {

reg = <1>;

remote-endpoint = <&imx464_out2>;

data-lanes = <1 2>;

};

};

port@1 {

reg = <1>;

#address-cells = <1>;

#size-cells = <0>;

csidphy1_out: endpoint@0 {

reg = <0>;

remote-endpoint = <&mipi2_csi2_input>;

};

};

};

};

&csi2_dphy2 {

status = "okay";

ports {

#address-cells = <1>;

#size-cells = <0>;

port@0 {

reg = <0>;

#address-cells = <1>;

#size-cells = <0>;

mipi_in_ucam3: endpoint@1 {

reg = <1>;

remote-endpoint = <&imx464_out3>;

data-lanes = <1 2>;

};

};

port@1 {

reg = <1>;

#address-cells = <1>;

#size-cells = <0>;

csidphy2_out: endpoint@0 {

reg = <0>;

remote-endpoint = <&mipi3_csi2_input>;

};

};

};

};

&csi2_dphy4 {

status = "okay";

ports {

#address-cells = <1>;

#size-cells = <0>;

port@0 {

reg = <0>;

#address-cells = <1>;

#size-cells = <0>;

mipi_in_ucam4: endpoint@1 {

reg = <1>;

remote-endpoint = <&imx464_out4>;

data-lanes = <1 2>;

};

};

port@1 {

reg = <1>;

#address-cells = <1>;

#size-cells = <0>;

csidphy4_out: endpoint@0 {

reg = <0>;

remote-endpoint = <&mipi4_csi2_input>;

};

};

};

};

&csi2_dphy5 {

status = "okay";

ports {

#address-cells = <1>;

#size-cells = <0>;

port@0 {

reg = <0>;

#address-cells = <1>;

#size-cells = <0>;

mipi_in_ucam5: endpoint@1 {

reg = <1>;

remote-endpoint = <&imx464_out5>;

data-lanes = <1 2>;

};

};

port@1 {

reg = <1>;

#address-cells = <1>;

#size-cells = <0>;

csidphy5_out: endpoint@0 {

reg = <0>;

remote-endpoint = <&mipi5_csi2_input>;

};

};

};

};

&i2c5 {

status = "okay";

pinctrl-0 = <&i2c5m3_xfer>;

/* module 77/79 0x1a 78/80 0x36 */

imx464_2: imx464-2@1a {

compatible = "sony,imx464";

status = "okay";

reg = <0x1a>;

clocks = <&cru CLK_MIPI_CAMARAOUT_M3>;

clock-names = "xvclk";

power-domains = <&power RK3588_PD_VI>;

pinctrl-names = "default";

pinctrl-0 = <&mipim0_camera3_clk>;

avdd-supply = <&vcc_mipicsi0>;

reset-gpios = <&gpio1 RK_PA4 GPIO_ACTIVE_HIGH>;

pwdn-gpios = <&gpio1 RK_PB3 GPIO_ACTIVE_HIGH>;

rockchip,camera-module-sync-mode = "internal_master";

rockchip,camera-module-index = <2>;

rockchip,camera-module-facing = "back";

rockchip,camera-module-name = "CMK-OT1980-PX1";

rockchip,camera-module-lens-name = "SHG102";

port {

imx464_out2: endpoint {

remote-endpoint = <&mipi_in_ucam2>;

data-lanes = <1 2>;

};

};

};

imx464_3: imx464-3@36 {

compatible = "sony,imx464";

status = "okay";

reg = <0x36>;

clocks = <&cru CLK_MIPI_CAMARAOUT_M3>;

clock-names = "xvclk";

power-domains = <&power RK3588_PD_VI>;

avdd-supply = <&vcc_mipicsi0>;

pwdn-gpios = <&gpio1 RK_PA7 GPIO_ACTIVE_HIGH>;

rockchip,camera-module-sync-mode = "external_master";

rockchip,camera-module-index = <3>;

rockchip,camera-module-facing = "back";

rockchip,camera-module-name = "CMK-OT1980-PX1";

rockchip,camera-module-lens-name = "SHG102";

port {

imx464_out3: endpoint {

remote-endpoint = <&mipi_in_ucam3>;

data-lanes = <1 2>;

};

};

};

};

&i2c4 {

status = "okay";

pinctrl-0 = <&i2c4m3_xfer>;

/* 77/79 0x1a 78/80 0x36 */

imx464_4: imx464-4@1a {

compatible = "sony,imx464";

status = "okay";

reg = <0x1a>;

clocks = <&cru CLK_MIPI_CAMARAOUT_M4>;

clock-names = "xvclk";

power-domains = <&power RK3588_PD_VI>;

pinctrl-names = "default";

pinctrl-0 = <&mipim0_camera4_clk>;

avdd-supply = <&vcc_mipicsi1>;

reset-gpios = <&gpio1 RK_PB5 GPIO_ACTIVE_HIGH>;

pwdn-gpios = <&gpio1 RK_PB4 GPIO_ACTIVE_HIGH>;

rockchip,camera-module-sync-mode = "external_master";

rockchip,camera-module-index = <0>;

rockchip,camera-module-facing = "back";

rockchip,camera-module-name = "CMK-OT1980-PX1";

rockchip,camera-module-lens-name = "SHG102";

port {

imx464_out4: endpoint {

remote-endpoint = <&mipi_in_ucam4>;

data-lanes = <1 2>;

};

};

};

imx464_5: imx464-5@36 {

compatible = "sony,imx464";

status = "okay";

reg = <0x36>;

clocks = <&cru CLK_MIPI_CAMARAOUT_M4>;

clock-names = "xvclk";

power-domains = <&power RK3588_PD_VI>;

avdd-supply = <&vcc_mipicsi1>;

pwdn-gpios = <&gpio1 RK_PB0 GPIO_ACTIVE_HIGH>;

rockchip,camera-module-sync-mode = "external_master";

rockchip,camera-module-index = <1>;

rockchip,camera-module-facing = "back";

rockchip,camera-module-name = "CMK-OT1980-PX1";

rockchip,camera-module-lens-name = "SHG102";

port {

imx464_out5: endpoint {

remote-endpoint = <&mipi_in_ucam5>;

data-lanes = <1 2>;

};

};

};

};

&mipi2_csi2 {

status = "okay";

ports {

#address-cells = <1>;

#size-cells = <0>;

port@0 {

reg = <0>;

#address-cells = <1>;

#size-cells = <0>;

mipi2_csi2_input: endpoint@1 {

reg = <1>;

remote-endpoint = <&csidphy1_out>;

};

};

port@1 {

reg = <1>;

#address-cells = <1>;

#size-cells = <0>;

mipi2_csi2_output: endpoint@0 {

reg = <0>;

remote-endpoint = <&cif_mipi_in2>;

};

};

};

};

&mipi3_csi2 {

status = "okay";

ports {

#address-cells = <1>;

#size-cells = <0>;

port@0 {

reg = <0>;

#address-cells = <1>;

#size-cells = <0>;

mipi3_csi2_input: endpoint@1 {

reg = <1>;

remote-endpoint = <&csidphy2_out>;

};

};

port@1 {

reg = <1>;

#address-cells = <1>;

#size-cells = <0>;

mipi3_csi2_output: endpoint@0 {

reg = <0>;

remote-endpoint = <&cif_mipi_in3>;

};

};

};

};

&mipi4_csi2 {

status = "okay";

ports {

#address-cells = <1>;

#size-cells = <0>;

port@0 {

reg = <0>;

#address-cells = <1>;

#size-cells = <0>;

mipi4_csi2_input: endpoint@1 {

reg = <1>;

remote-endpoint = <&csidphy4_out>;

};

};

port@1 {

reg = <1>;

#address-cells = <1>;

#size-cells = <0>;

mipi4_csi2_output: endpoint@0 {

reg = <0>;

remote-endpoint = <&cif_mipi_in4>;

};

};

};

};

&mipi5_csi2 {

status = "okay";

ports {

#address-cells = <1>;

#size-cells = <0>;

port@0 {

reg = <0>;

#address-cells = <1>;

#size-cells = <0>;

mipi5_csi2_input: endpoint@1 {

reg = <1>;

remote-endpoint = <&csidphy5_out>;

};

};

port@1 {

reg = <1>;

#address-cells = <1>;

#size-cells = <0>;

mipi5_csi2_output: endpoint@0 {

reg = <0>;

remote-endpoint = <&cif_mipi_in5>;

};

};

};

};

&rkcif {

status = "okay";

};

&rkcif_mipi_lvds2 {

status = "okay";

port {

cif_mipi_in2: endpoint {

remote-endpoint = <&mipi2_csi2_output>;

};

};

};

&rkcif_mipi_lvds2_sditf {

status = "okay";

port {

mipi2_lvds_sditf: endpoint {

remote-endpoint = <&isp0_vir0>;

};

};

};

&rkcif_mipi_lvds3 {

status = "okay";

port {

cif_mipi_in3: endpoint {

remote-endpoint = <&mipi3_csi2_output>;

};

};

};

&rkcif_mipi_lvds3_sditf {

status = "okay";

port {

mipi3_lvds_sditf: endpoint {

remote-endpoint = <&isp1_vir0>;

};

};

};

&rkcif_mipi_lvds4 {

status = "okay";

port {

cif_mipi_in4: endpoint {

remote-endpoint = <&mipi4_csi2_output>;

};

};

};

&rkcif_mipi_lvds4_sditf {

status = "okay";

port {

mipi4_lvds_sditf: endpoint {

remote-endpoint = <&isp0_vir1>;

};

};

};

&rkcif_mipi_lvds5 {

status = "okay";

port {

cif_mipi_in5: endpoint {

remote-endpoint = <&mipi5_csi2_output>;

};

};

};

&rkcif_mipi_lvds5_sditf {

status = "okay";

port {

mipi5_lvds_sditf: endpoint {

remote-endpoint = <&isp1_vir1>;

};

};

};

&rkcif_mmu {

status = "okay";

};

&rkisp0 {

status = "okay";

};

&isp0_mmu {

status = "okay";

};

&rkisp0_vir0 {

status = "okay";

port {

#address-cells = <1>;

#size-cells = <0>;

isp0_vir0: endpoint@0 {

reg = <0>;

remote-endpoint = <&mipi2_lvds_sditf>;

};

};

};

&rkisp0_vir1 {

status = "okay";

port {

#address-cells = <1>;

#size-cells = <0>;

isp0_vir1: endpoint@0 {

reg = <0>;

remote-endpoint = <&mipi4_lvds_sditf>;

};

};

};

&rkisp1 {

status = "okay";

};

&isp1_mmu {

status = "okay";

};

&rkisp1_vir0 {

status = "okay";

port {

#address-cells = <1>;

#size-cells = <0>;

isp1_vir0: endpoint@0 {

reg = <0>;

remote-endpoint = <&mipi3_lvds_sditf>;

};

};

};

&rkisp1_vir1 {

status = "okay";

port {

#address-cells = <1>;

#size-cells = <0>;

isp1_vir1: endpoint@0 {

reg = <0>;

remote-endpoint = <&mipi5_lvds_sditf>;

};

};

};

1185

1185

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?