最近在牛客网刷数字IC真题,看到乐鑫科技2020秋招真题,做完发现有的人首先用c语言模拟输入输出参考模型用作verilog输入输出真值表参数,然后根据真值表算出输入输出各位之间的关系,这显然在现实笔试时是不可取的,时间浪费太多不说,就怕面试官不允许。那么如果不用这种办法,应该如何解决,答案是用generate并行例化多次模块。

题目:请将下面这段 C 语言描述的串行处理过程,转换为单拍完成的并行处理,并用可综合的 Verilog 来描述。

unsigned char cal_table_high_first(unsigned char value)

{

unsigned char i ;

unsigned char checksum = value ;

for (i=8;i>0;--i)

{

if (check_sum & 0x80)

{

check_sum = (check_sum<<1) ^ 0x31;

}

else

{

check_sum = (check_sum << 1);

}

}

return check_sum;

}

题目的难点在于如何处理好上一次的check_sum输入与其输出之间的关系,所以我们首先可以定义8个8位宽二维的数组,8个即for循环要处理8次,为什么位宽为8,因为unsigned char型为1个字节即8bit,定义wire [7:0] r_check [7:0];用于存储上一个输入与下一个输出。然后设计循环内部模块,其实就是个简单的判断赋值语句,如下:

module check(

input [7:0] value,

output [7:0] checksum

);

assign checksum = (value & 8'h80)?(value<<1)^8'h31:value<<1;

endmodule

整体代码如下所示:

不过要确保第一次例化输入为value[7:0],然后再将最后一次r_check[7][7:0]作为模块的输出。

module check_sum(

input [7:0] value,

output [7:0] checksum

);

wire [7:0] r_check [7:0];

assign checksum = r_check[7];

check u0_check(value,r_check[0]);

genvar i;

generate begin:inst_loop

for(i=0;i<7;i=i+1)begin

check u_check(r_check[i],r_check[i+1]);

end

end

endgenerate

endmodule

module check(

input [7:0] value,

output [7:0] checksum

);

assign checksum = (value & 8'h80)?(value<<1)^8'h31:value<<1;

endmodule

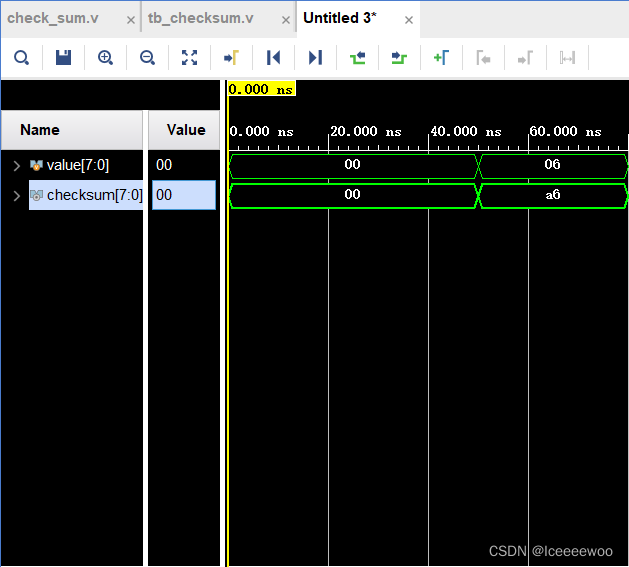

最后仿真输入输出:

1536

1536

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?