GPIO的结构体系

zynq的GPIO,分为两种,MIO(multiuse I/O)和EMIO(extendable multiuse I/O)。

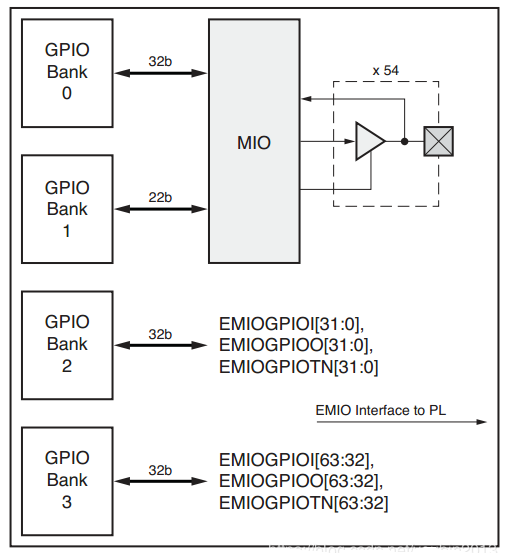

ZYNQ的GPIO由4个BANK组成,其体系结构如图1所示。其中Bank0有32个GPIO引脚,Bank1有22个引脚,共54个GPIO引脚直接通过MIO连接到PS上,每个引脚可以通过寄存器的设置来确定该引脚为输入、输出或者中断,因为54个MIO引脚直接连接在PS上,像其他普通ARM一样,不需要通过XPS进行硬件配置,直接通过SDK编程即可。

Bank2和Bank3通过EMIO接口将CPU的GPIO连接到PL部分的引脚上,其中每个Bank各有32个引脚,通过EMIO扩展的GPIO连接到PL上,可以在PL部分进行逻辑设计,进行特定功能的IP核制定。然后在PS部分,像控制普通MIO一样进行编程。因此,使用EMIO引脚必须通过XPS进行硬件配置,然后在PS部分使用SDK进行编程控制。

图1 GPIO的组成

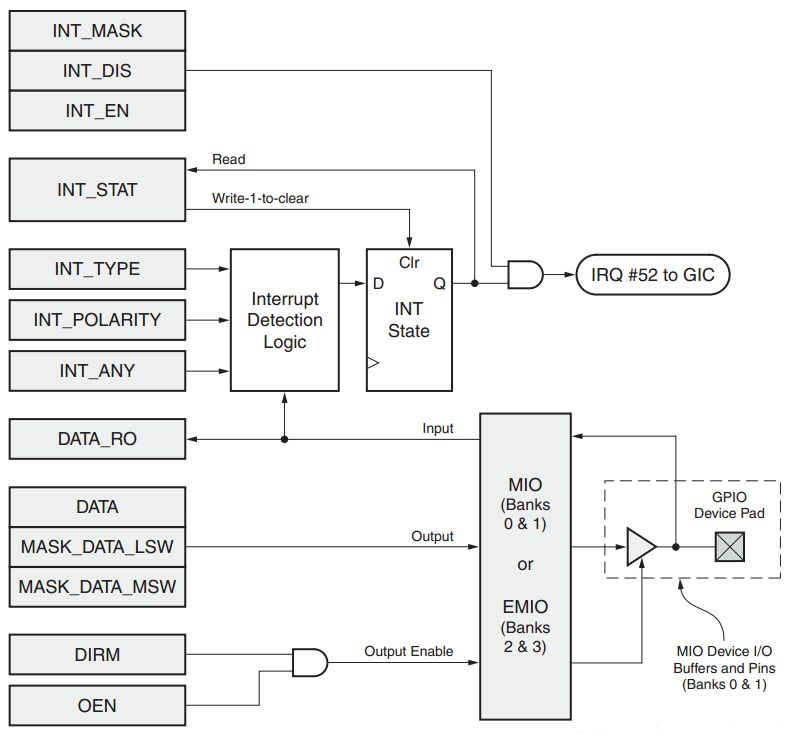

GPIO的内部结构和内部数据流及寄存器结构如图2所示。上半部分为GPIO中断相关的寄存器,下半部分为GPIO查询方式读写的寄存器。

图2 GPIO寄存器数据流组成

DATA_RO寄存器是读取GPIO引脚值寄存器,不论该GPIO引脚配置为输入还是输出,都能正确读取该GPIO引脚值。如果该引脚的功能没有配置成GPIO功能,读取的值为随机值,因为该寄存器只能读取GPIO引脚值。

DATA寄存器的值是要输出到GPIO引脚上的数值,当读取该寄存器的数值时,

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

2431

2431

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?