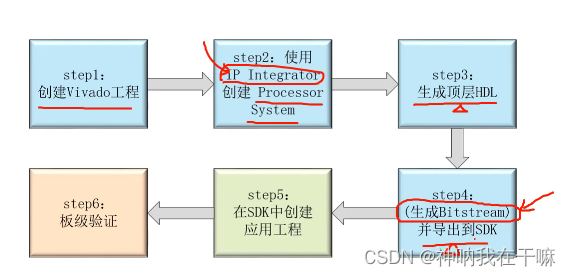

使用FPGA(PL)则要生成比特流。否则不需要。浅蓝色方框属于硬件设计部分,导出到SDK中后开启软件开发的过程。

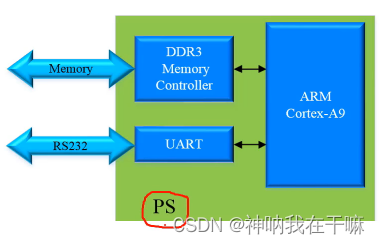

最小系统

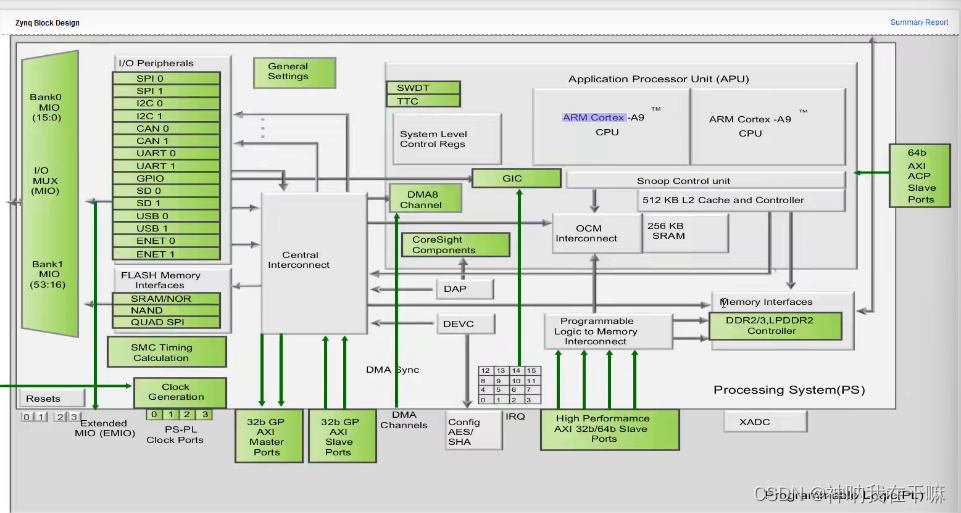

最小系统只涉及PS部分。PS包含处理器和外设。PL对PS来说是外设。

PS的核心就是ARM Cortex-A9处理器。外设1:

DDR3存储器,是程序运行空间,与外部存储器连接用来运行软件程序。

UART让最小系统让ARM与外部通信。

硬件设计

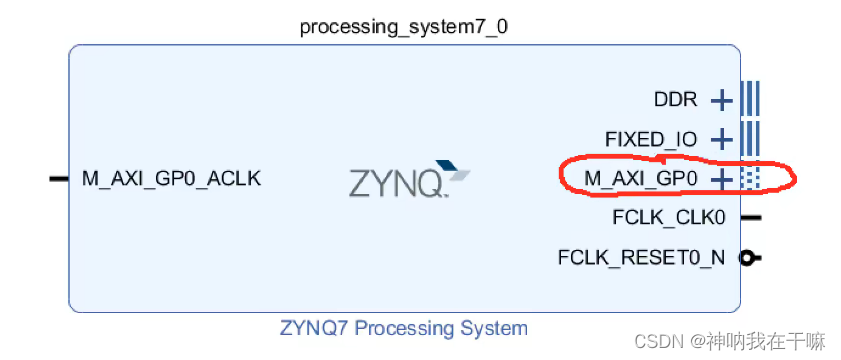

M_AXI_GP0对应

- DDR Configuration

7020核心板DDR3选用MT41J256M16 RE-125

DDR3:8192Mbit = 8Gbit

7010核心板DDR3选用MT41J128M16

DDR3:4096Mbit = 4Gbit - 配置UART

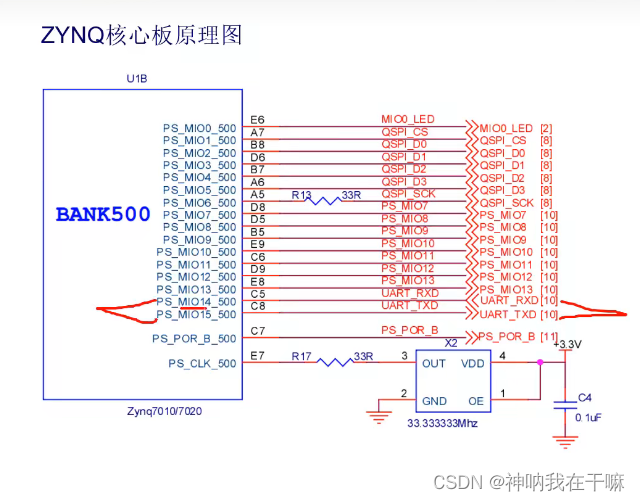

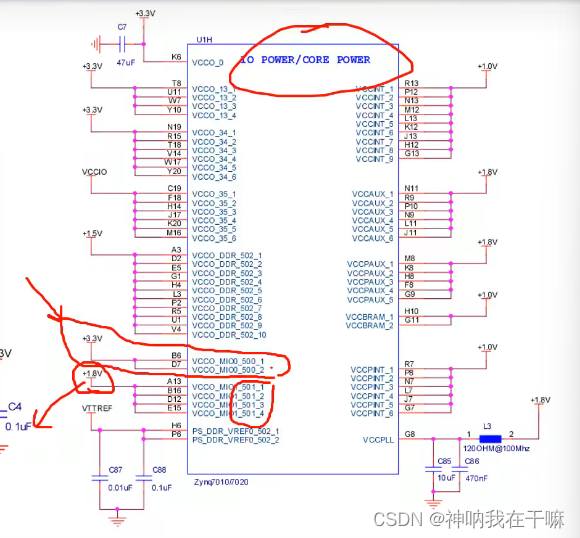

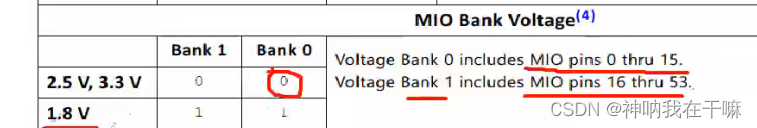

MIO有两个Bank,Bank0有16个引脚,Bank1有38个引脚。所使用电压不同。

Bank0:3.3V

Bank1:1.8v

- 删除PS中的多余接口

删掉M_AXI_GP0和M_AXI_GP0_ACL。

删掉PS提供给PL的时钟信号FCLK_CLK0

tips:查看系统时钟:

Clock Configuration —> Input frequency显示的是晶振提供的源时钟(33.333MHz),CPU和DDR的时钟分别是ARM锁相环和DDR锁相环配频提供的。

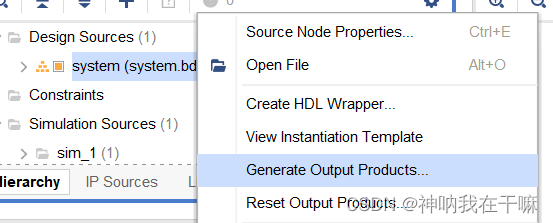

FCLK_RESET0_N是PS提供给PL的复位接口。 - 生成IP

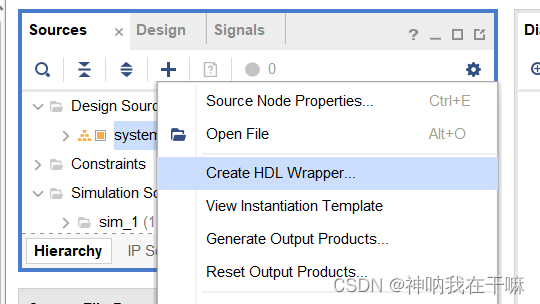

- 生成硬件描述顶层文件

用硬件描述语言把刚才的设计封装起来。

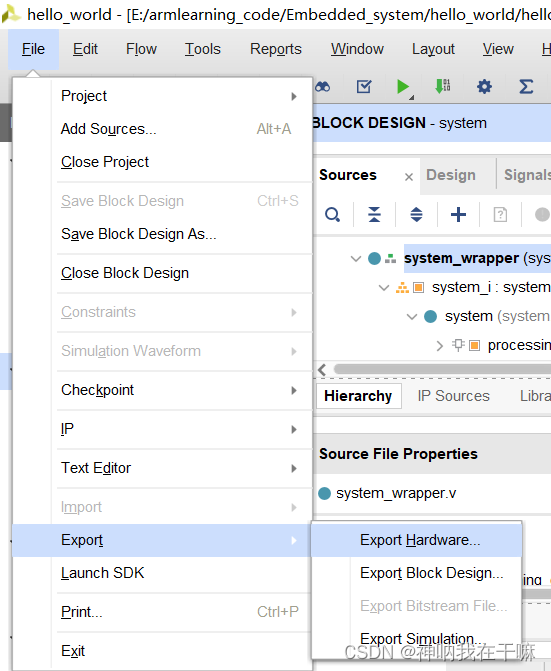

至此,硬件设计过程只剩下导出到SDK一步(本次不用PL,不需要生成比特流)。

- 导出到SDK

软件设计

板级支持包(.bsp):在上层应用和底层硬件之间的桥梁

GPIO

-

GPIO是一个外设,用来对器件的引脚作观测(观测器件引脚高低电平,GPIO作为input,如把GPIO通过引脚接到按键上,按键按下后,GPIO可以观测到器件引脚电平)以及简单的控制(GPIO作为output,如把GPIO通过引脚接到LED/蜂鸣器上, 通过GPIO控制引脚高低电平,从而控制LED/蜂鸣器的状态)。(通过MIO模块 )

APU:PS的核心,其中最关键的是两个ARM Cortex-A9 CPU -

MIO:把来自PS外设和静态存储器接口的访问多路复用到PS 的引脚上。

PS端502引脚只能连接到DDR存储器,剩余可用引脚仅有54个,但是由于外设众多,引脚不够用,因此要借助MIO模块实现引脚的多路复用。外设都通过MIO与外部引脚进行连接,MIO通过编程选择具体哪个外设连接引脚。 -

EMIO

I/O外设可以通过EMIO连接到PL的引脚,来实现PS的引脚扩展 -

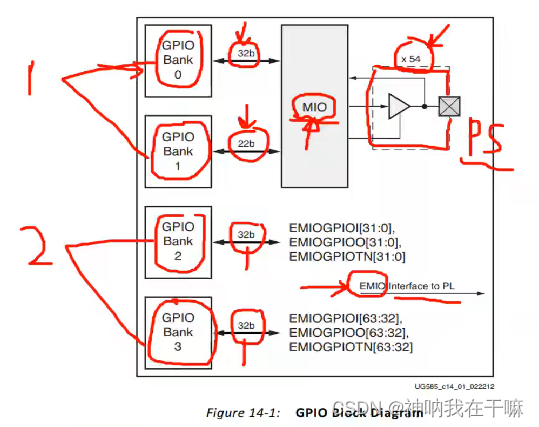

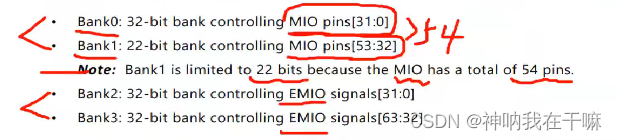

GPIO的寄存器分为四组,每组称为一个bank,bank0和bank1通过MIO连接到PS的引脚,bank2和bank3通过EMIO连接到PL。

-

每个GPIO都是独立且动态可编程的,可编程为input/output/中断模式

-

软件通过一组存储映射的寄存器来控制GPIO

每个外设的寄存器对应一个地址空间,处理器对外设的寄存器的存储空间进行读写从而控制寄存器。

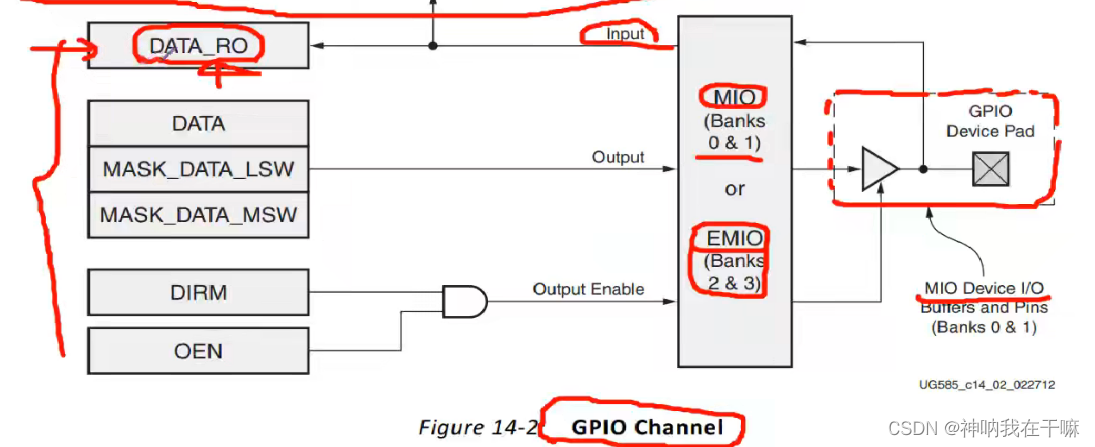

单个GPIO通道功能示意图

右边方框是器件引脚。Bank0和Bank1通过MIO连接到PS端的引脚上。

左边是三组寄存器组。

- DATA_RO(只读)的功能是实现GPIO的观测功能,GPIO作为输入,外部器件引脚上的电平通过input线路反映在DATA_RO寄存器中。想知道器件引脚上的电平状态,只要读寄存器即可。当GPIO作为输出时,DATA_RO寄存器也会返回GPIO引脚的状态(反映写到器件引脚上的数值)。

如果MIO没有被配置成GPIO的引脚,即器件引脚没有连接到GPIO,则DATA_RO是不确定值。 - output所连接的一组寄存器用来控制器件引脚。

DATA:用来控制器件引脚上的数值(例如器件引脚连接到了LED,则往DATA中写1就是点亮),对于单个引脚只有0/1两个状态,由于DATA寄存器是32位的,所以每次都要操作32个器件引脚。仅当GPIO被配置成输出时,DATA寄存器才能控制数值。如何单独操作单个器件引脚后文详述。DATA寄存器可读可写。当读它时,只能读出上一次往DATA中写的数值,而读不到引脚的当前状态(要用DATA_RO)。

MASK_DATA_LSW/MSW(16位寄存器):灵活改变DATA寄存器中的特定位。

MASK_DATA_LSW:用于屏蔽DATA寄存器的低16位(把需要屏蔽的位置1,需要操作的位置0)

MASK_DATA_MSW:用于屏蔽DATA寄存器的高16位 - 最后一组寄存器用来控制输出使能信号。

DIRM:Direction Mode。用来控制I/O引脚是作为输入还是输出。其实就是输出使能。当DIRM赋值为0时,输出驱动关闭,作为输入使用。为1时,打开输出驱动。

OEN:Output Enable。输出使能。仅当I/O被配置为输出时(DIRM=1),才能控制输出打开或关闭。

DIRM和OEN经过了与门,即同时被配置为1时,才能正常输出信号。

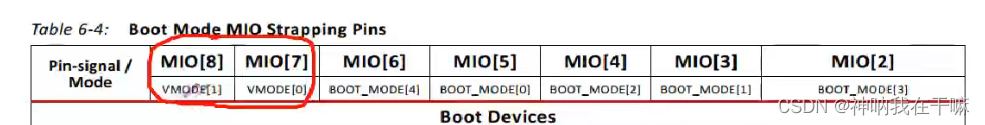

MIO的Bank0的bit8和bit7作输出

MIO的寄存器被分为Bank0(pin0~15)和Bank1(pin16~53两组),两组所接的电压可以不同,如可以设置Bank0接1.8v,Bank1接3.3v。

-

MIO[8:7]在系统复位过程中作为VMODE引脚,是输入信号,用于配置MIO Bank的电压模式。

MIO[7]用来控制Bank0所接电压,当其为0时,Bank0所接电压为2.5/3.3v,当其为1时,Bank0所接电压为1.8v。

MIO[8]用来控制Bank1所接电压,当其为0时,Bank1所接电压为2.5/3.3v,当其为1时,Bank1所接电压为1.8v。

7和8做输入时不能随便设置,要根据板卡手册中bank所需电压进行配置。 -

复位结束后,MIO[8:7]只能作为输出信号,被连接到LED上。

895

895

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?