微处理器基本算数逻辑单元的设计中,着重关注四则运算的设计,本篇列出相关的且常见的设计方案。

加法器

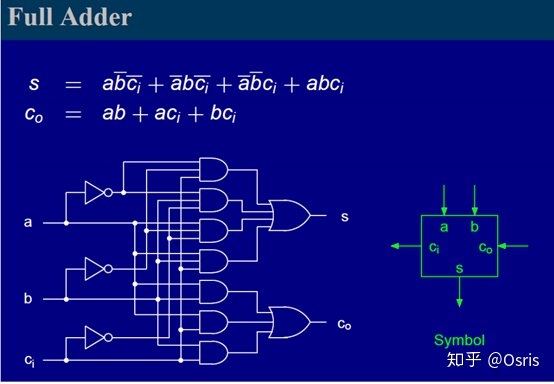

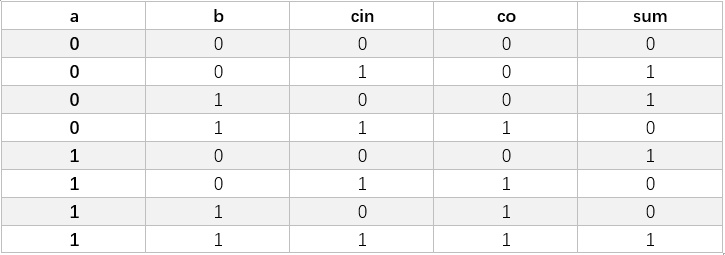

一位全加器:

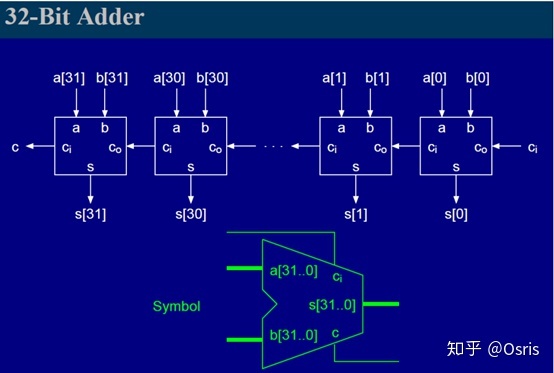

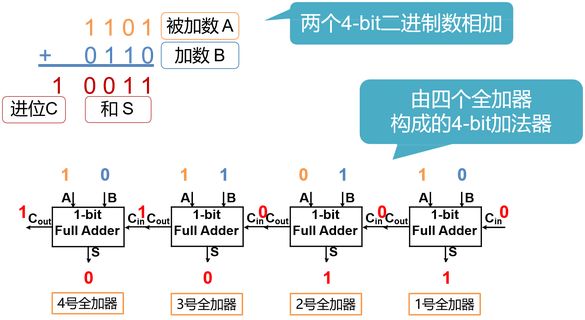

行波进位加法器:

超前进位加法器:

超前进位加法器的门延时相比行波进位加法器要少很多,处理器中常用的也是超前进位加法器。

下面是一些参考链接,比较详细地介绍了CLA。

https://blog.csdn.net/moon548834/article/details/80344335blog.csdn.net 基于Verilog HDL的超前进位全加器设计www.cnblogs.com

乘法器:

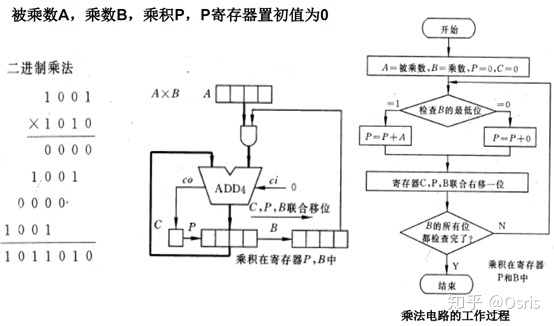

乘法器的基本运算过程如下图所示,基于下述过程可以进行乘法器的设计。

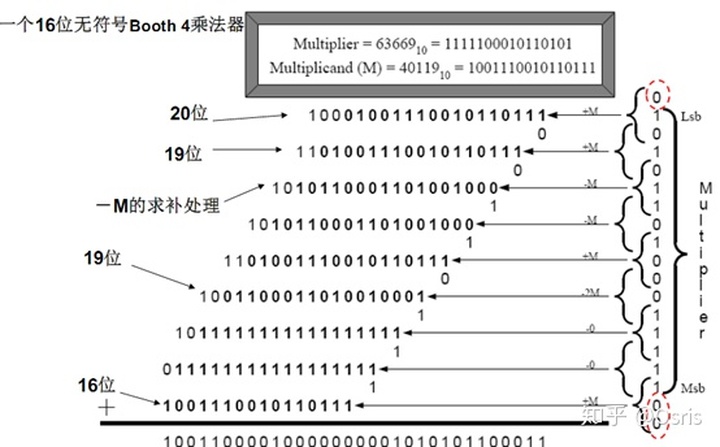

BOOTH编码:

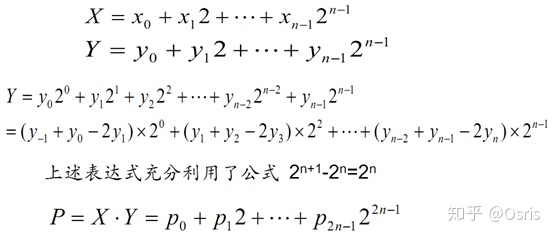

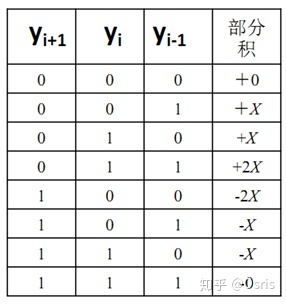

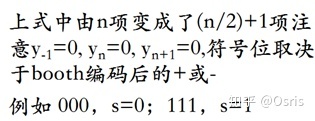

传统的n位乘法器会产生n个部分积,BOOTH编码提出对乘数进行编码,以减少部分积的个数。

n=8时的无符号booth编码下的xy之积:

由于编码后的系数对应的乘量是公比为4的等比数列,所以称为基4的Booth4编码。

部分积:

如果n是偶数:

举例:

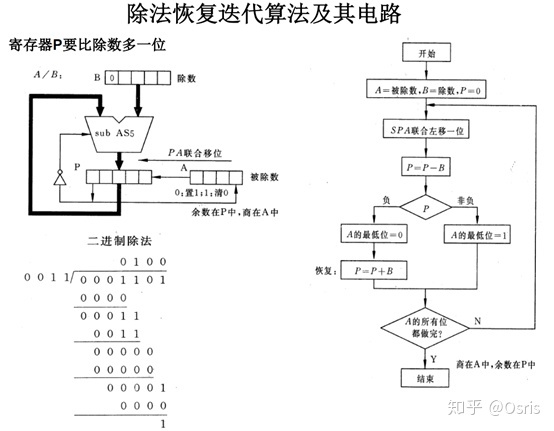

除法器:

除法器的基本运算过程如下图所示,基于下述过程可以进行除法器的设计。

4612

4612

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?