所有的数字电路都需要依靠时钟信号来使组件的运作同步,每单位时间内电路可运作的次数取决于时钟的频率,因此时钟运作的频率即被大家视为系统运作的性能指针。

主机板时钟电路的需求

---熟悉硬件的读者应该都知道,主机板上处理器、芯片组和主存储器等几个主要的组件各有其工作时钟,中央处理器CPU的外部频率依照摩尔定律不断提高,随着英特尔与AMD在近期推出多款新的处理器,200MHz外频的时代也正式来临(CPU上标示的工作速度为处理器内频,是以外频乘以倍频产生,并不由主机板时钟电路直接提供)。处理器和北桥芯片之间以前端总线(FSB)相连接,以CPU的外频为基准,每周期传送两次或四次数据,所以200MHz外频乘上四倍频就可以得到800MHz的FSB速度。内存也随着CPU的脚步,工作频率快速推进到200MHz的DDR400PC3200规格。其余南桥芯片与AGP、PCI、USB等总线则各有其业界规定的工作时钟标准,如PCI为33MHz、AGP为66MHz等等。

---因此主机板的时钟电路必须为许多的组件提供各种不同的工作频率,以往旧式的主机板都是使用石英振荡器来处理,但石英振荡器一次只能输出一种频率,在需要多种时钟输出的新式主机板中,显然不敷使用。所以有些厂商将这些原本散布在主机板上各处的振荡电路整合成一颗可输出各种频率的芯片,主机板采用此类时钟产生芯片将可以达到节省成本与空间的目的。

时钟发生器的基本构造

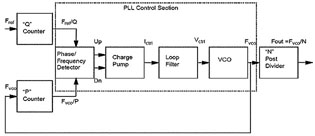

---锁相环(PhaseLockedLoop,PLL)是时钟发生器的核心技术,现代的时钟发生器只需由石英晶体提供一个基准频率,并利用一个以上的PLL,搭配不同比例的除频电路,来产生各种频率的时钟输出,取代传统系统中的多个石英晶体。时钟发生器的基本架构如图1所示。

---其中PLL的部分具有两个输入端,分别为参考频率(Fref)与反馈频率(Fvco),与一个输出端(Fout)。三者之间关系可以公式表示如下。

Fout=(Fref•P)/(Q•N)

---PLL基本上为一个负反馈系统,在回路中利用反馈信号,将输出端的信号频率及相位,锁定在输入端参考信号的频率及相位上。相位频率检波器(PhaseFrequencyDetector,PFD)比较基准参考频率(Fref)及反馈频率(Fvco)两者之间的相位关系与频率的差异,并检知出两者相位的相位差及频率的高低差,以影响电压控制振荡器(VoltageControlledOscillator,VCO)的频率输出。当Fref/Q超前Fvco/P时,UP高电位输出使Fout频率加快;相反的当Fref/Q落后Fvco/P时,DN高电位输出使Fout频率减慢,最后可达到如公式所表示的稳定输出状态,因此只需调整PLL外部除频电路的P、Q、R值之间的比例,就可得到需要的输出频率。

PC超频与时钟电路的关联

---超频对于计算机发烧友来说,可谓是最热衷的一个主题了。所谓超频就是强迫系统的工作时钟于高于标示的频率,从而达到提高性能的目的。

4554

4554

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?