FPGA Verilog 硬件描述 + NIOS II 软核设计

EPCS FLASH 容量解读 (实现最大的利用价值)

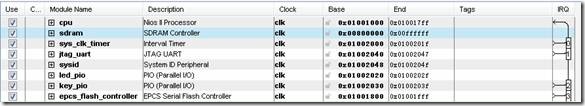

一些基本外设(NIOS/F,SDRAM,LED,KEY,EPCS,JTAG_UART等)

(SOPC IP设计)

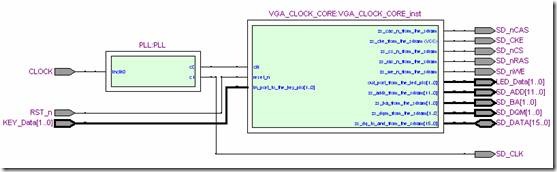

Quartus II Verilog TOP File

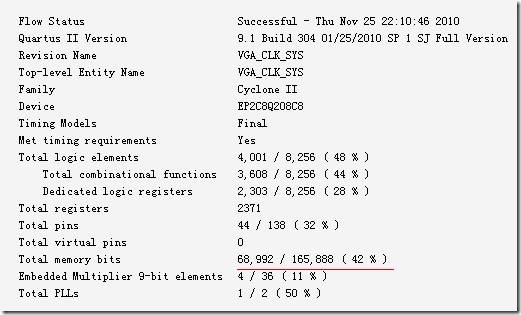

综合后Quartus II 报表

可见,差不多用了1/2的FPGA,相当于120KB的二进制文件

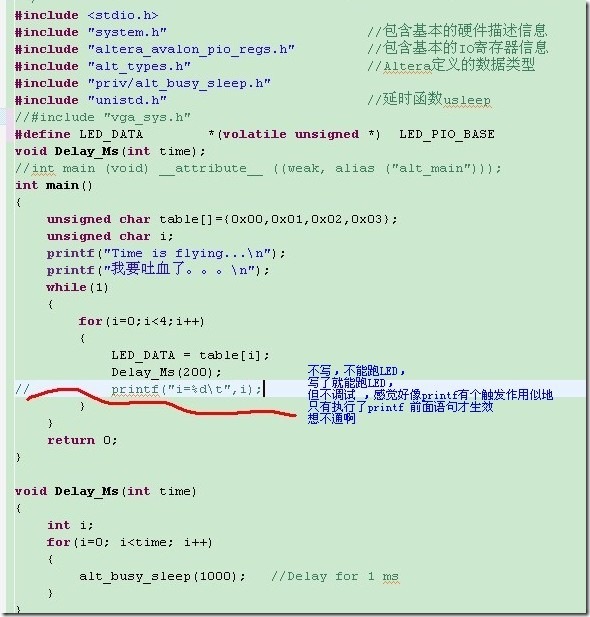

NIOS II中Water_LED程序设计

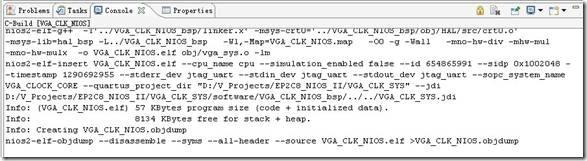

NIOS II软件系统编译结果

由上图可知,最基本的满足SDRAM+EPCS+JTAG_UART+LED+KEY的SOPC硬核设计,以及在NIOS II最简单的流水灯设计,只花费了57KB。

结论:

(一)对于EP2C ,假设我们以上最基本的设计来计算容量,则

Verilog+NIOS II = 120KB+57KB=177KB>128KB

所以EPCS1不够用

因此,(1)若Verilog量相当大,EPCS1一般不够用(149KB > 128KB)

(2) 上系统,一般EPCS1也不够用

若用EPCS4,512KB>177KB,即使硬件描述用了100%,也还有512-57-149=306KB的容量

STC12C1052 51单片机 只有1KB 的FLASH(306倍)

STC89LE516RD+(增强型)单片机 61KB的FLASH(5倍)

ARM7 STM32F103ZET6有512 KB的FLASH(0.6倍)

根据以上数据,您应该看得到,EPCS4是否能满足你的需求

更多关于EPCS16,EPCS64,请自己算

(二) 同样对于EP2C8,我们直接忽略EPCS1,计算EPCS4

Verilog+NIOS II = 120KB+57KB=177KB << 512KB

因此,(1)若Verilog量相当大,EPCS4一般不够用(242KB << 512KB)

(2)若上系统,512KB>177KB,即使硬件描述用了100%,也还有512-57-242=213KB的容量

STC12C1052 51单片机 只有1KB 的FLASH(213倍)

STC89LE516RD+(增强型)单片机 61KB的FLASH(4倍)

ARM7 STM32F103ZET6有512 KB的FLASH(0.4倍)

根据以上数据,您应该看得到,EPCS4是否能满足你的需求

再不行,用EPCS16,EPCS64,EPCS128

NIOS II 的那个bmp上有个问题,那个不知道怎么解决。愿会的给点指点。

谢谢ZLG的《SOPC嵌入式系统设计基础》,我才搞懂了这个,

如果其中有什么错误,请指正,谢谢。。。

![clip_image002[5] clip_image002[5]](https://images.cnblogs.com/cnblogs_com/crazybingo/WindowsLiveWriter/FPGAVerilogNIOSIIEPCSFLASH_AC7C/clip_image002%5B5%5D_thumb.jpg)

![clip_image004[5] clip_image004[5]](https://images.cnblogs.com/cnblogs_com/crazybingo/WindowsLiveWriter/FPGAVerilogNIOSIIEPCSFLASH_AC7C/clip_image004%5B5%5D_thumb.jpg)

1302

1302

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?