1.介绍

System Generator(SG)是Xilinx公司的系统建模工具,在很多方面扩展了Math Works公司的Simulink平台,提供了适合硬件设计的数字信号处理建模环境,加速、简化了FPGA的DSP系统级硬件设计。SG提供了系统级设计能力,允许在相同的环境内进行软、硬件仿真、执行和验证,并不需要书写HDL代码。

本例使用SG做一个Xilinx FPGA流水灯的小实验。

软件环境:matlab 2011b,ISE13.2

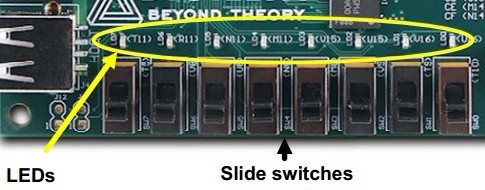

硬件环境:Nexys™3 Spartan-6 FPGA Board ,晶振100MHz

2.实验步骤

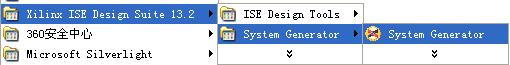

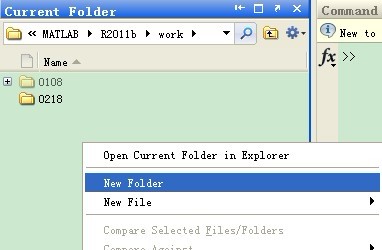

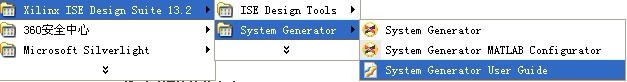

2.1.打开System Generator,创建工作目录。

点击上图所示图标,SG打开后就会弹出Matlab和Simulink Library Browser工具条。这时在matlab右边的Current Folder工具栏里,选择自己平时喜欢的路径,鼠标右键点击New Folder创建一个新的文件,命名为0218,这样有利于文件管理。然后点击进入新建的文件夹0218中。(或者在Command中输入类似于linux的shell命令:cd 0218也可以进入文件夹,cd ..退到上一层)

2.2建立mdl文件

点击Simulink Library Browser工具条中File ->New->Model,新建一个mdl工程文件。

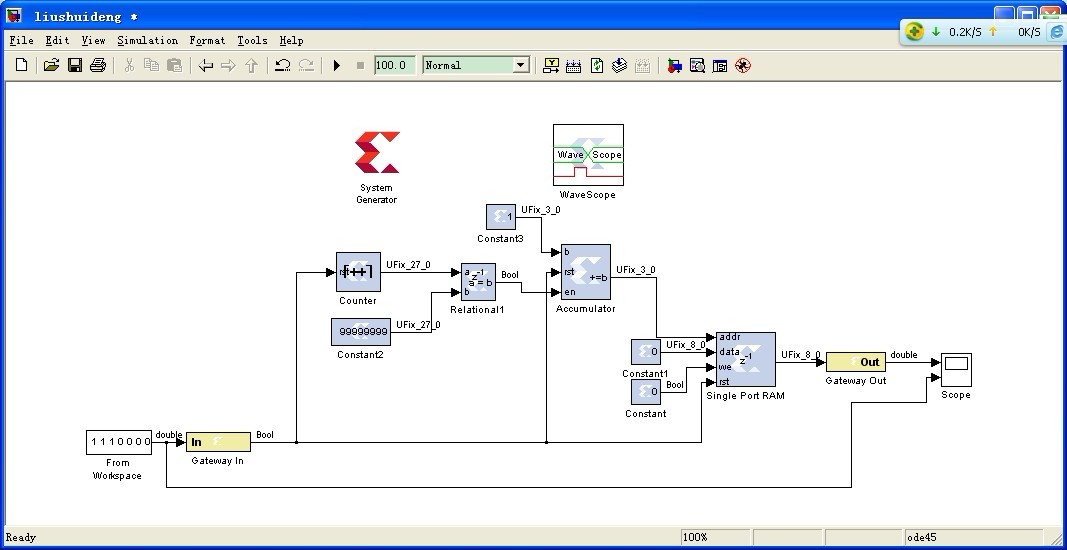

简单介绍:Gateway In模块和Gateway Out模块中间的部分是FPGA硬件要实现的DSP部分,采用的模块组件当然要是Xilinx Blockset、Xilinx Reference Blockset中要有的,这样才能让SG生成可综合的代码。

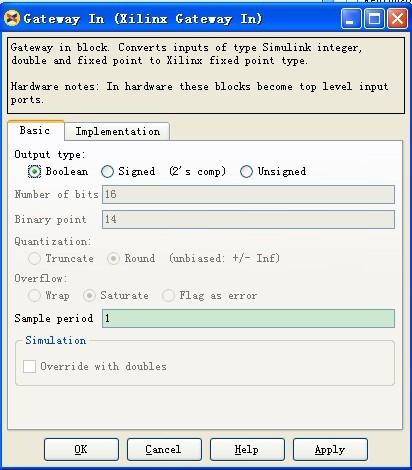

本例中Gateway In模块仅仅用来系统复位,定义的类型为Boolean。输出连接到其他需要复位的分频模块和Single Port Ram模块中。Counter ,Constant,Accumulator定义时都需要用户自定义数据类型。数据类型的选择很重要,选择不当出错那是必然的,数据类型分为Boolean,Signed ,Unsigned三种类型。设计的时候点击mdl文件Format ->Port/Signal Displays ->Port Data Types就可以在图中很直观的看到信号的类型。

Sample period根据需要,如果不涉及多速率问题一般都设置为1。

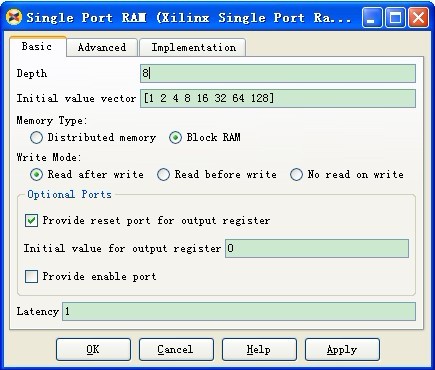

Single Port RAM 中存储需要输出的流水灯的八种状态。Initial value vector中的数据类型在上图中并没有定义,类型默认与在RAM输入端data保持一致,为 UFix_8_0(无符号定点数,位宽为8,小数位0表示没有)。本例中RAM中的数已经预先在Initial value vector写好,所以输入端we(write enalbe)输入0、不使能,输入端data为0也只是起到定义RAM中数据类型的作用。通过控制addr地址输出想要的信号。

ps:自己调试mdl文件的时候,分频100M比较难观察,所以就把Counter 的counter to value从99999999调到3,相应Constant2也设置为3(initial value为0保持不变),先做4分频的实验,在WaveScope中观察波形(WaveScope中可以自由添加需要观察的信号,类似于modelsim),达到预期效果后再把两个模块参数改回99999999,实现流水灯一秒钟移位一次。

2.3生产HDL代码

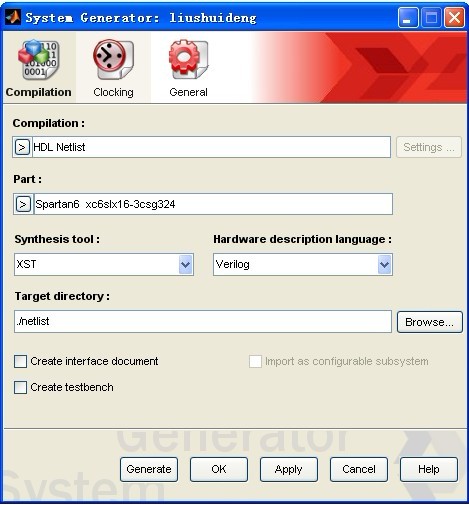

mdl文件设计无误后,先保存一下,命名liushuideng。双击mdl框图中System Generator图标,就会弹出上图所示的对话框,修改默认的Part,芯片类型和封装要和板子上的FPGA芯片一致。Hardware description language尽量选择自己熟悉的。Create interface document和Creat testbench写论文有用,如果做前仿真,它的效果和mdl里的wave Scope一样,感觉没什么必要。

确实无误后点击Generate,耐心等待2分钟后就会生产hdl代码,路径在当前目录下的netlist里。(如果以后做比较大的工程,等待的时间会比较长。完成后如果感觉电脑比较卡,也可以保存mdl文件后把matlab关掉,接下来就用不到它了。)

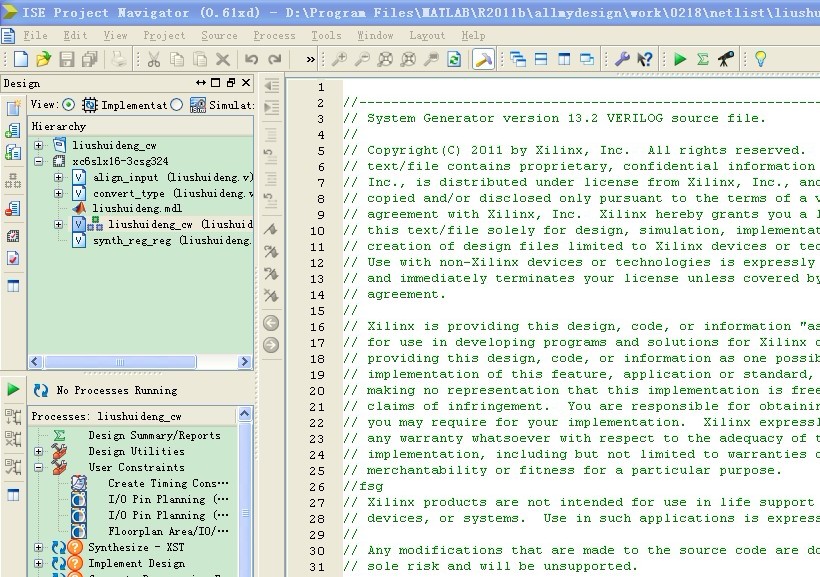

双击上述生成的netlist路径下的liushuideng_cw.xise工程文件,打开后如上图所示。点击选中design里的liushuideng_cw,点击Synthesize-XST综合生成的代码。

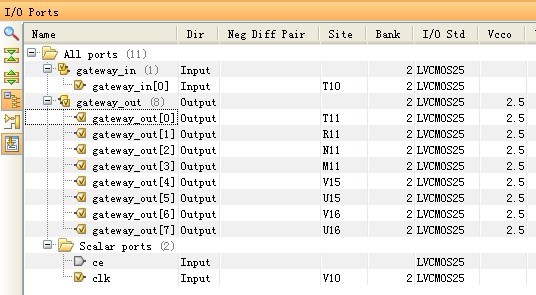

综合无误后,点击User constraints里的 I/O Pin Planning.....进行引脚分配。

参考Nexys™3 Spartan-6 FPGA Board 技术手册,分配合适的引脚给输入gateway_in,输出Gateway_out信号和Scalar ports里的时钟clk信号。(Scalar ports的ce听说是用来进行多速率调试用的,分不分配引脚无关紧要)。保存、退出PlanAhead返回到ISE中。

ISE中依次双击Implement Design ,Generate Programing File 和Configure Targe Device里的Generate Targe PROM/ACE File。打开ISE iMPACT,下载liushuideng_cw.bit文件到板卡中。

拨T10到低电平,就可以观察到,每隔一秒种闪亮的小灯向右循环移位一次。

3.System Generator资料

当然最好的资料要属官方的 System Generator User Guide,国内好多资料也都是翻译后照搬过来的,所以好多书读起来跟技术手册差不多。

《多媒体处理FPGA实现-System Generator篇》这本书中的例子虽然有的有些bug,但总体来讲还不错。书中有一些具体工程的实例,可以参考下。

2022

2022

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?