本教程内容力求以详细的步骤和讲解让读者以最快的方式学会 MC8051 IP core 的应用以及相关设计软件的使用,并激起读者对 SOPC 技术的兴趣。本实验重点讲 8051Core 的应用,并通过一个简单 C51 程序对 51Core 进行硬件测试。

本实验教程的内容编排如下:

第 1 章简单的描述了 MC8051 IP core 的基本结构及一些应用说明。

第 2 章详细的介绍 8051Core 综合、编译应用。包括 Quartus II软件的基本应用,ROM、RAM 模块的生成,8051Core 的封装及应用测试。 附录 A 为 MC8051 IP Core 的指令集。

在阅读本教程的过程中,请读者注意以下几点:

本教程在编写时充分借鉴了周立功编写的mc8051 IP核教程,同时针对其中较为落后的一些内容进行了更新(周立功的教程使用的还是Cyclone系列的器件,软件版本也很低,很多操作与目前使用的主流版本有较大区别),同时删除了其教程中使用Synplicity对工程进行综合的部分,转而使用Quartus II软件直接综合。

本实验教程的 MC8051 IP Core (V1.6) 源于 http://oregano.at/ip/8051.htm 网站,读者如有需要可到该网站下载。

第1章 MC8051 的基本结构

这一章将简单的介绍 MC8051 IP Core 的基本硬件结构和一些设计应用的注意事项,具

体内容包括:

1. 功能特点

2. 顶层结构

3. 设计层次

4. 硬件配置

5. 并行 I/O 口

6. 其它说明

本章介绍的内容可能过于简略,如果要更详细的资料可参考 mc8051_user_guide.pdf

文档(位于:“mc8051_v1.6源码.zip\Version1_6\doc”文件夹里面)。

1.1 功能特点

● 采用完全同步设计

● 指令集和标准 8051 微控制器完全兼容

● 指令执行时间为 1~4 个时钟周期,执行性能优于标准 8051 微控制器 8 倍左右

● 用户可选择定时器/计数器、串行接口单元的数量

● 新增了特殊功能寄存器用于选择不同的定时器/计数器、串行接口单元

● 可选择是否使用乘法器(乘法指令 MUL)

● 可选择是否使用除法器(除法指令 DIV)

● 可选择是否使用十进制调整功能(十进制调整指令 DA)

● I/O 口不复用

● 内部带 256Bytes RAM

● 最多可扩展至 64Kbytes 的 ROM 和 64Kbytes 的 RAM

● 最多可扩展至 64Kbytes 的 ROM 和 64Kbytes 的 RAM

1.2 顶层结构

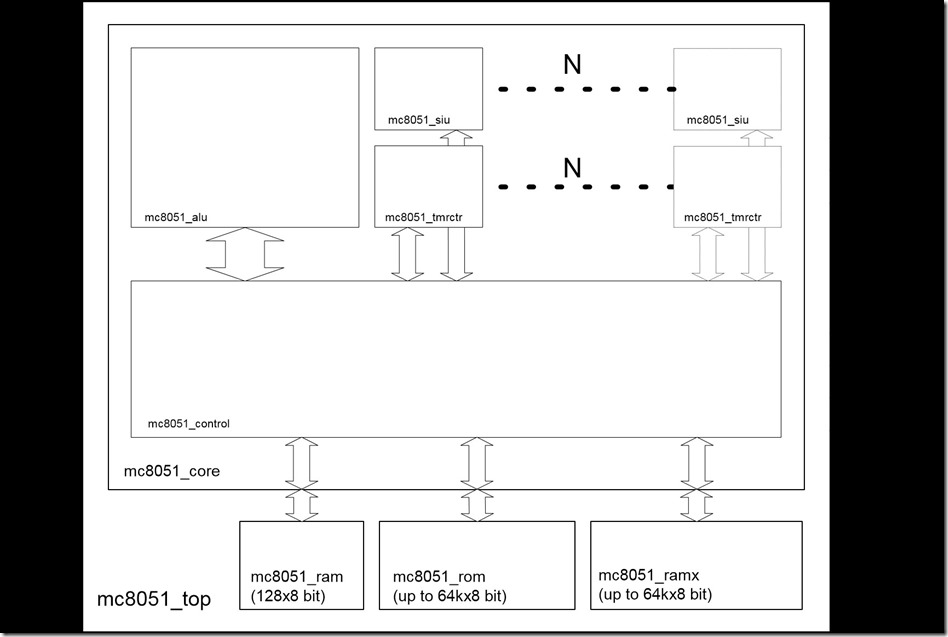

MC8051 IP Core 顶层结构图如图 1.1 所示,图中指示了 mc8051_core 的顶层结构以及同 三个存储模块的连接关系,同时显示了顶层的输入输出 I/O 口,各 I/O 信号的描述如表 1.1 所示。定时器/计数器和串行接口单元对应于图中的 mc8051_tmrctr 和 mc8051_siu 模块,数量是可选择的,在图中用虚线表示。

图 1.1 MC8051 IP Core 顶层结构图

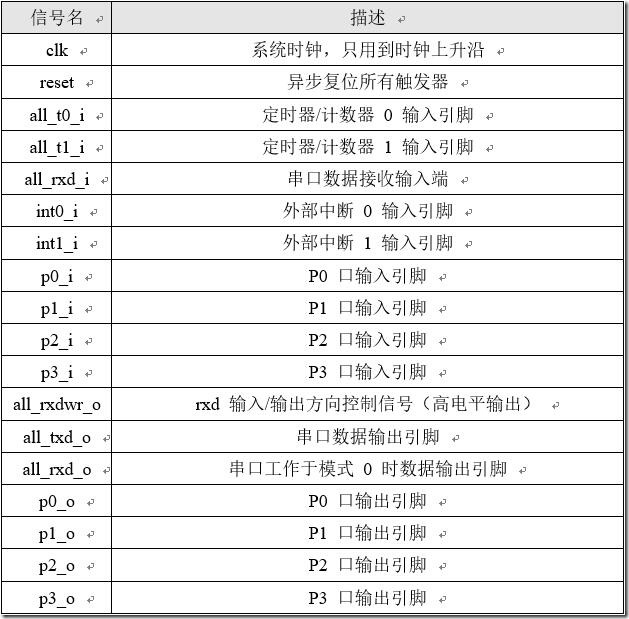

表 1.1 顶层信号名

1.3 设计层次

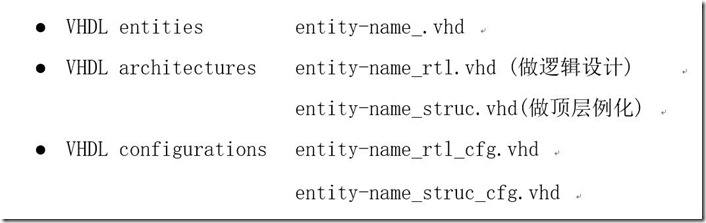

MC8051 IP Core 的层次结构及对应的 VHDL 文件如图 1.2 所示。

VHDL 源文件的命名格式如下:

核心由定时器/计数器、ALU、串行接口和控制单元各模块组成。ROM 和 RAM 模块不

包括于核心内,处于设计的顶层,方便于不同的应用设计及仿真。

图 1.2 MC8051 IP Core 的设计层次

1.4 硬件配置

1.4.1 定时器/计数器、串口和中断

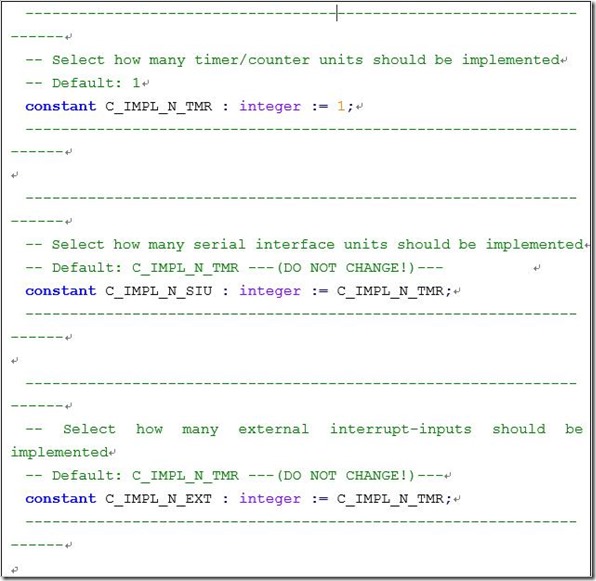

标准的 8051 核只有两个定时器/计数器,一个串口和两个外部中断源。而在 MC8051 IPCore 中,这些单元最多可增加到 256 组,只需要在 VHDL 源程序文件 mc8051_p.vhd 中,更改C_IMPL_N_TMR、C_IMPL_N_SIU、C_IMPL_N_EXT的常量值就可以了,范围是1~256。相关的代码如程序清单 1.1 所示。

程序清单 1.1 定时器/计数器、串口及中断的配置程序

-------------------------------------------------------------------- -- Select how many timer/counter units should be implemented -- Default: 1 constant C_IMPL_N_TMR : integer := 1; -------------------------------------------------------------------- -------------------------------------------------------------------- -- Select how many serial interface units should be implemented -- Default: C_IMPL_N_TMR ---(DO NOT CHANGE!)--- constant C_IMPL_N_SIU : integer := C_IMPL_N_TMR; -------------------------------------------------------------------- -------------------------------------------------------------------- -- Select how many external interrupt-inputs should be implemented -- Default: C_IMPL_N_TMR ---(DO NOT CHANGE!)--- constant C_IMPL_N_EXT : integer := C_IMPL_N_TMR; --------------------------------------------------------------------

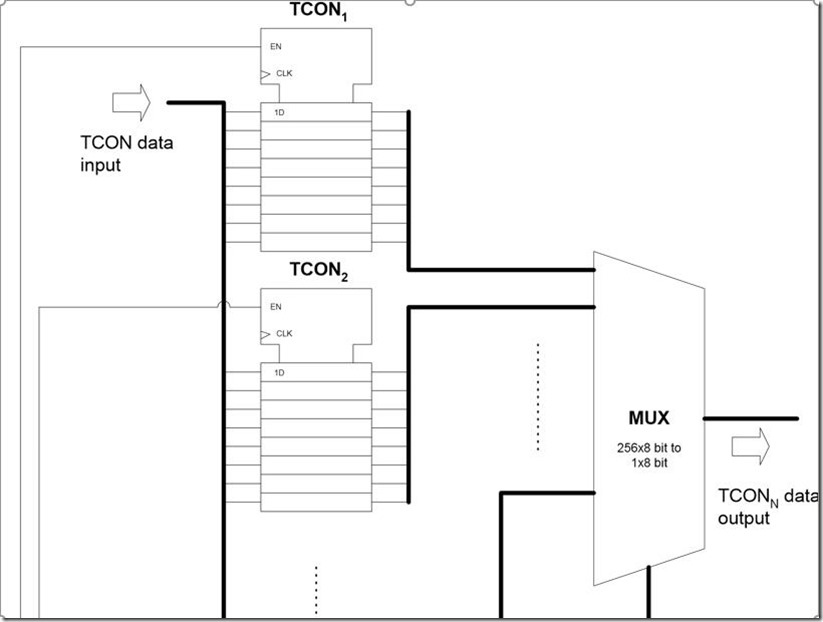

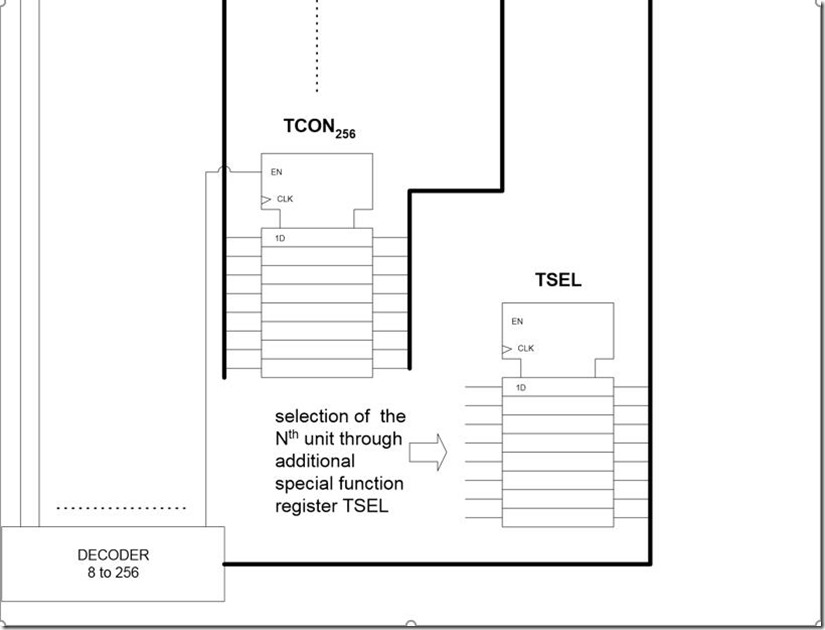

C_IMPL_N_TMR、C_IMPL_N_SIU、C_IMPL_N_EXT 这三个常量是不能独立修改数值的,也就是说只能同时增减。C_IMPL_N_TMR 加一,就意味 IP Core 中同时添加了两个定时器/计数器,一个串口单元和两个外部中断源。 为了控制这些新增的控制单元,微控制器在特殊寄存器内存空间增加了两个寄存器。分别是 TSEL(定时器/计数器选择寄存器,地址为 0X8E)和 SSEL(串口选择寄存器,地址为 0X9A),如果没有对这两个寄存器赋值,其缺省值为 1。电路结构如图 1.3 所示。

图 1.3 使用附加的 TSEL 寄存器选择 TCON 寄存器

如果在中断发生期间设备(寄存器)没被选中(比如 TSEL),那么相应的中断标志位将保持置位,直到中断服务程序被执行。

1.4.2 可选择的指令

在某些场合,有些指令是用不到的,因此可以通过禁用这些指令来节省片上(比如 FPGA)资源。这些指令有 8 位乘法器(MUL)、8 位除法器(DIV)和 8 位十进制调整器(DA)。禁用时只需要在 VHDL 源程序文件 mc8051_p.vhd 中将 C_IMPL_MUL(乘法指令 MUL)、 C_IMPL_DIV(除法指令 DIV)或 C_IMPL_DA(十进制调整指令 DA)的常量值设置为 0。相应的 VHDL 程序代码段如所示。

程序清单 1.2 可选指令配置程序

-------------------------------------------------------------------- -- Select whether to implement (1) or skip (0) the multiplier -- Default: 1 constant C_IMPL_MUL : integer := 1; -------------------------------------------------------------------- -------------------------------------------------------------------- -- Select whether to implement (1) or skip (0) the divider -- Default: 1 constant C_IMPL_DIV : integer := 1; -------------------------------------------------------------------- -------------------------------------------------------------------- -- Select whether to implement (1) or skip (0) the decimal adjustment command -- Default: 1 constant C_IMPL_DA : integer := 1; --------------------------------------------------------------------

这三条可选择指令如果没被设置执行,芯片(FPGA)可节省将近 10%的空间(资源)。

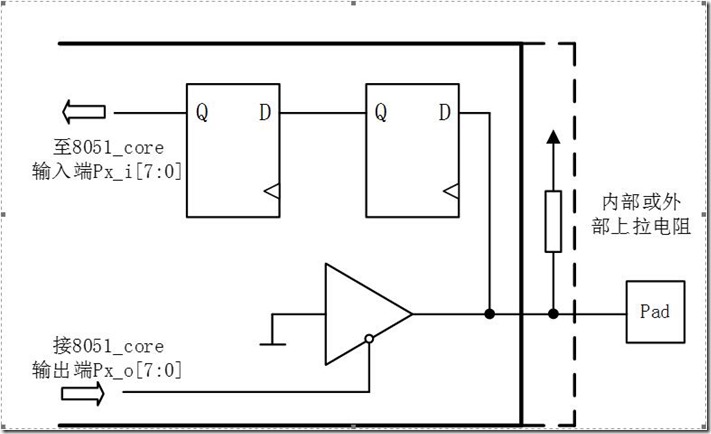

1.5 并行 I/O 口

为了便于 IC 设计,MC8051 IP Core 的 I/O 口不提供复用功能,包括 4 个 8 位输入输出口、串行接口、计数器输入端和扩展存储器接口。如果 I/O 要做为双向口应用,其基本电路

结构图如图 1.4 所示。

图1.4 并行I/O口基本结构

图 1.4 中的两个 D 触发器起同步输入信号的作用(mc8051_core 的输入 I/O 无做同步处理),也可以不用。上拉电阻是必要的,因为 I/O 口输出高电平是靠上拉电阻实现的。

1.6 其它说明

(1) MC8051 IP Core 的定时器和串口波特率的计算和标准 8051 一样,计数时钟也是由系 统时钟经 12 分频得到。

(2) 外部中断信号是经两级寄存器做同步处理后输入的。

(3) MC8051_core 的输入 I/O 没有做同步处理,必要时可自己添加,如图 1.4 所示。

(4) 写应用程序时,I/O 口如果没有做成双向口(如图 1.4 所示),而是输入和输出分开的,那么要特别注意,像 P1=~P1、P1^0=P1^0 这样的 I/O 取反操作是无效(不起作用)的,因为读回来的值不是 I/O 寄存器的值,而是输入引脚的状态。

(5) MC8051 IP Core 经 Quartus II 综合编译后,观看时序分析报告,其最高运行频率为 32MHz(每次编译都可能不同,I/O 分配不同结果可能不同),因此系统时钟不能超过时序报告的时钟最高频率(即 fmax)。

第2章 MC8051 的硬件运行

本实验的硬件平台是采用芯航线FPGA学习套件,关于本实验套件的的详细介绍,请参看《芯航线FPGA学习平台用户手册》,这里就不重复说明。这里只简单说一些本实验用到的硬件资源以及相关软件的基本操作。

本章我们主要讲述 MC8051 core 的生成及封装,最后进行硬件下载运行并测试 I/O 口、 UART 及定时器。用到的硬件资源有为开发套件核心板上的LED0~LED3 、USB转串口接口。 本章将分以下几部分来讲述:

1. MC8051 中 ROM、RAM 模块的生成;

2. MC8051 core RTL 的封装;

3. MC8051 core 在 Quartus II 中的应用;

4. 测试 MC8051 的 I/O、UART 和定时器功能。 本实验力求以详细的步骤和讲解让读者以最快的方式学会 MC8051 IP core 的应用以及

相关设计软件的使用,并激起读者对 SOPC 技术的兴趣。

2.1 MC8051 中 ROM、RAM 模块的生成

本节的内容是建立一个 Quartus II 应用工程,并利用 Quartus II 自身集成的 Megawizard Plug_in Manager 工具(/在Quartus II 14.0版本及以后,名字改为了IP Catlog)来生成 MC8051 中所需的内部 RAM、外扩 RAM 及 ROM。

2.1.1 建立 Quartus II 工程

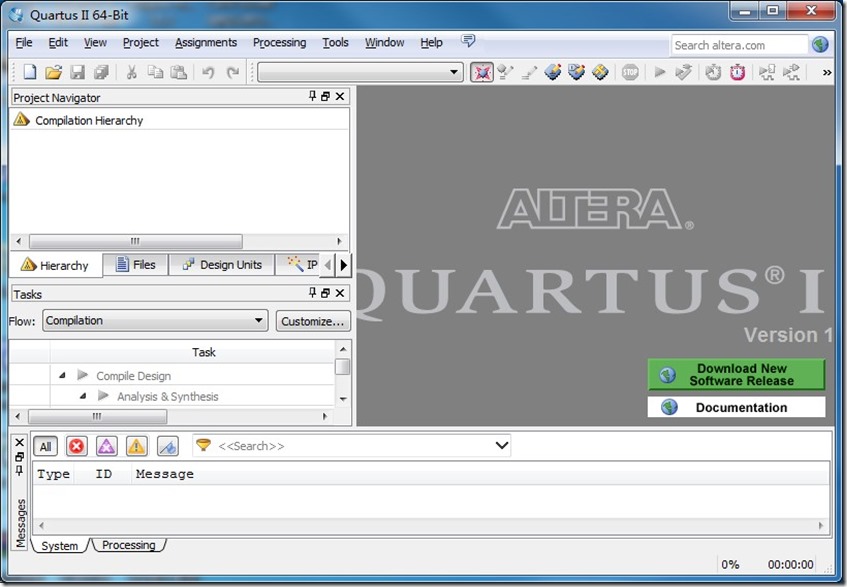

从【开始】>>【程序】>>【Altera】>>【Quartus II 13.0】或直接双击桌面的Quartus II软件图标 打开 Quartus II 13.0 软件,软件界面如图 2.1 所示。

打开 Quartus II 13.0 软件,软件界面如图 2.1 所示。

图 2.1 Quartus II 软件界面

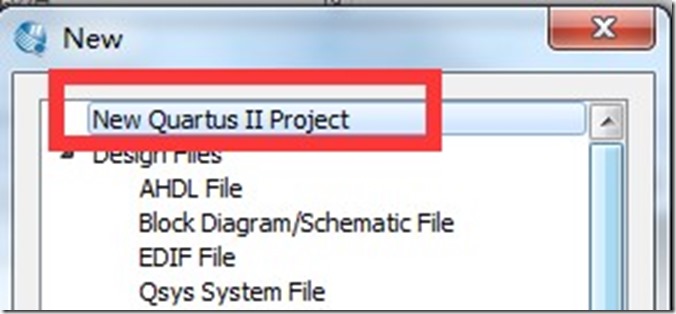

在图 2.1 中从【File】>>【New】打开新建文件选项卡,在选项卡中选择【New Quartus II Project】来新建一项工程,软件界面如图 2.2 所示。

图 2.2 新建Quartus II 文件

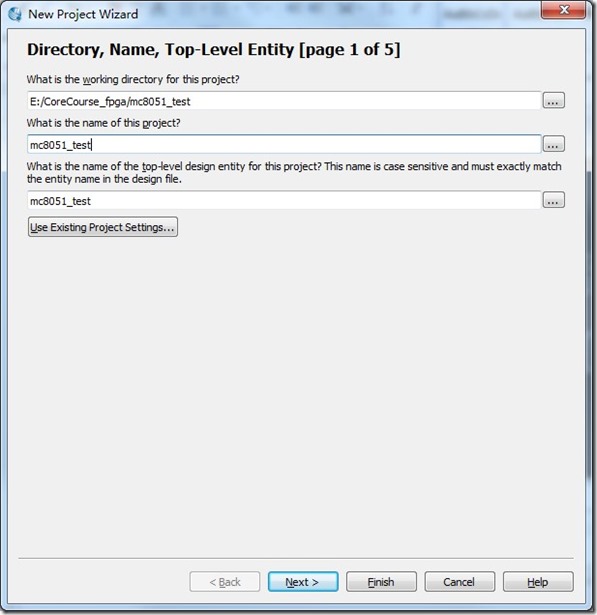

打开后显示界面如下所示:

图 2.3 新建工程路径、名称、顶层实体指定对话框

![]() 不要将文件夹设在计算机已有的安装目录中,更不要将工程文件直接放在安装目录中。文件夹所在路径名和文件夹名中不能用中文,不能用空格,不能用括号(),可用下划线_,最好也不要以数字开头。

不要将文件夹设在计算机已有的安装目录中,更不要将工程文件直接放在安装目录中。文件夹所在路径名和文件夹名中不能用中文,不能用空格,不能用括号(),可用下划线_,最好也不要以数字开头。

图 2.3 第一栏用于指定工程所在的工作库文件夹;第二栏用于指定工程名,工程名可以取任何名字,也可以直接用顶层文件的实体名作为工程名(建议使用);第三栏用于指定顶层文件的实体名。本例工程的路径为 E:\CoreCourse_fpga\mc8051_test文件夹,工程名与顶层文件的实体名同名为 mc8051_test。

本教程详细介绍了如何在FPGA上使用MC8051软核,包括IP核的基本结构、硬件配置、ROM和RAM模块的生成,以及在Quartus II中的应用。教程涵盖从建立工程到综合、编译,再到硬件下载和功能测试的全过程,旨在帮助读者快速掌握MC8051 IP Core的使用和相关设计软件的操作。

本教程详细介绍了如何在FPGA上使用MC8051软核,包括IP核的基本结构、硬件配置、ROM和RAM模块的生成,以及在Quartus II中的应用。教程涵盖从建立工程到综合、编译,再到硬件下载和功能测试的全过程,旨在帮助读者快速掌握MC8051 IP Core的使用和相关设计软件的操作。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

6538

6538

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?