目录

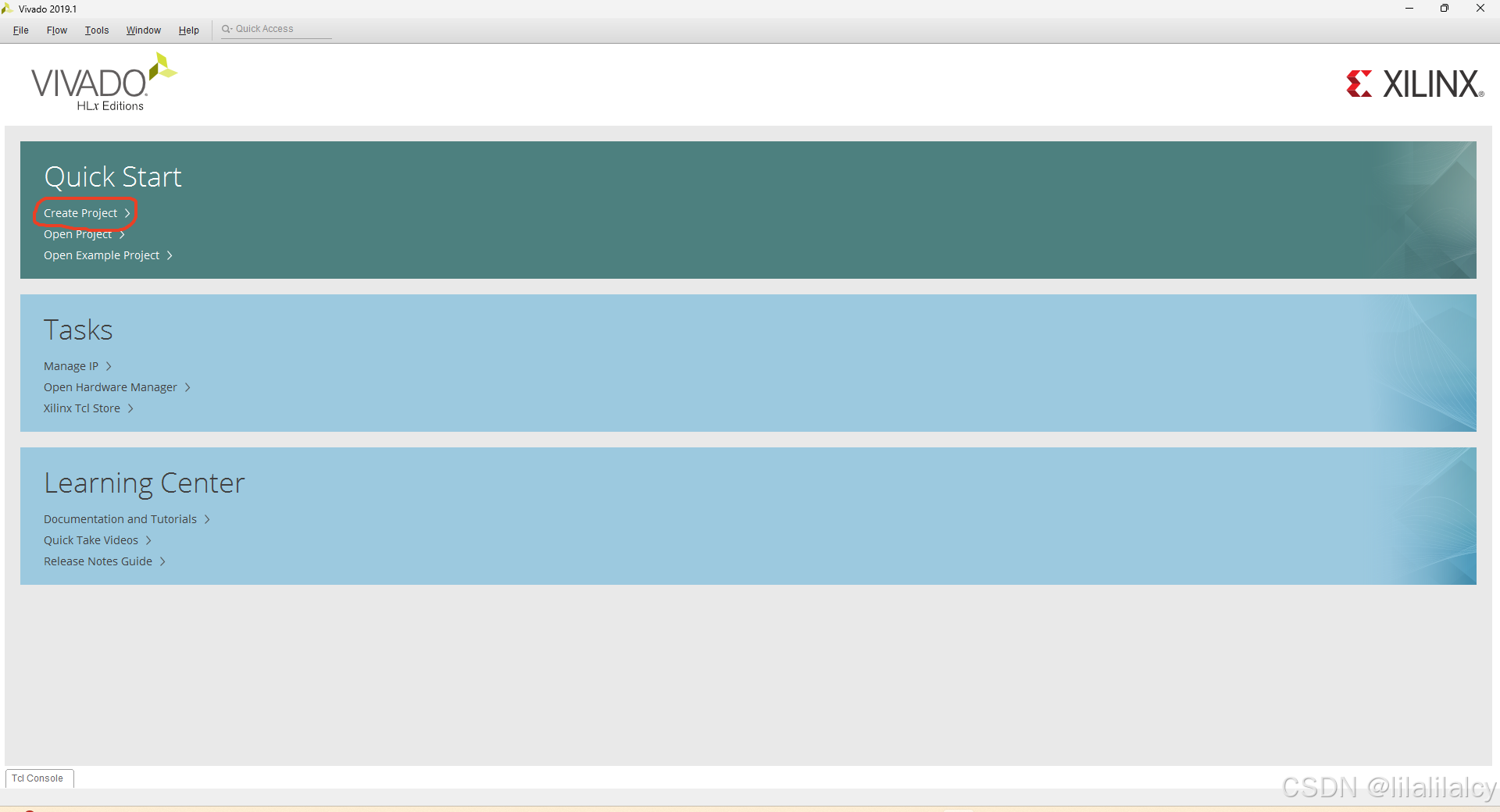

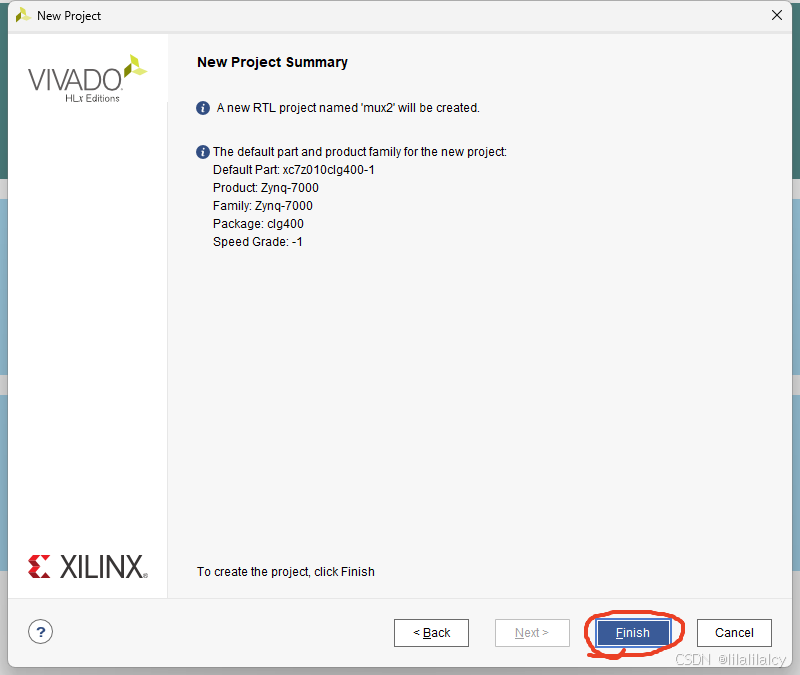

创建工程

1.create project

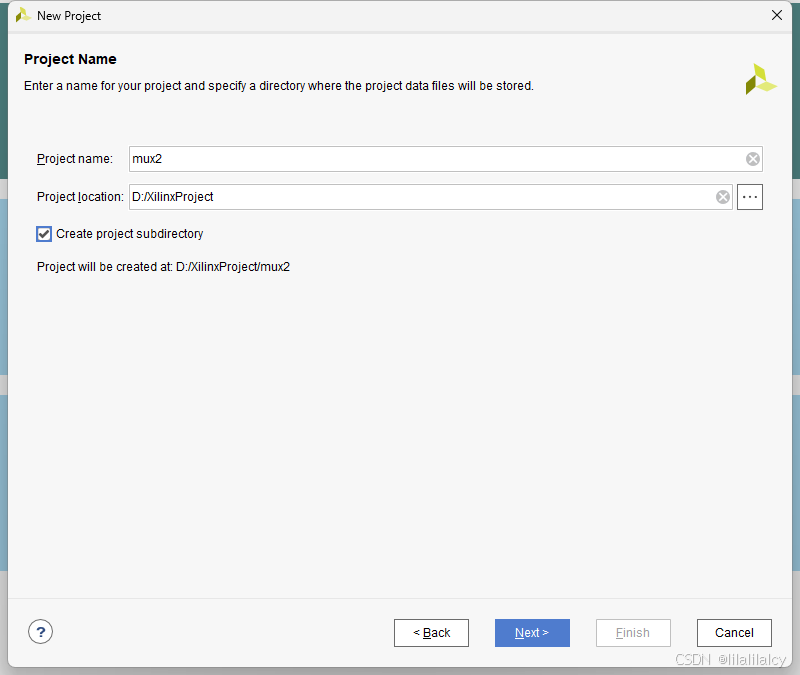

2.工程名称和地址

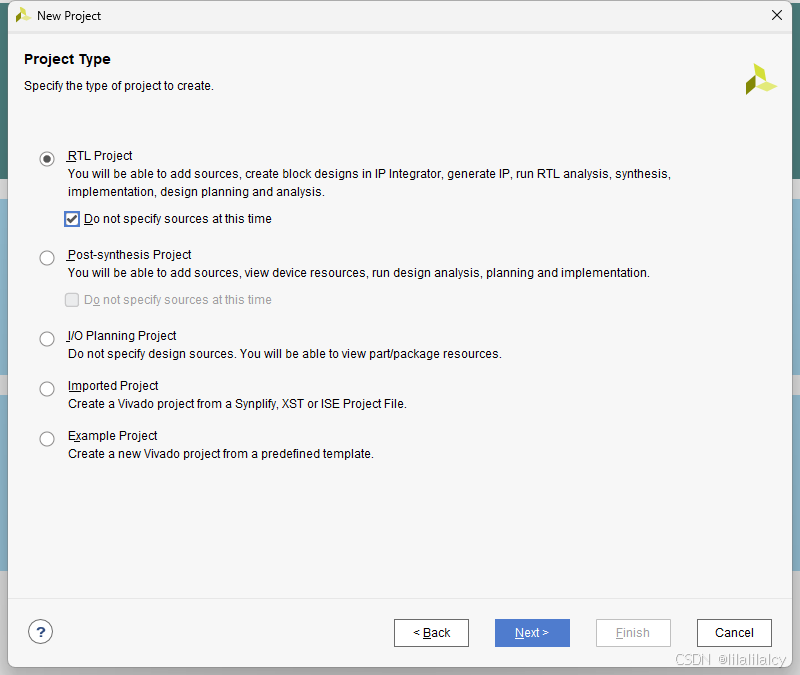

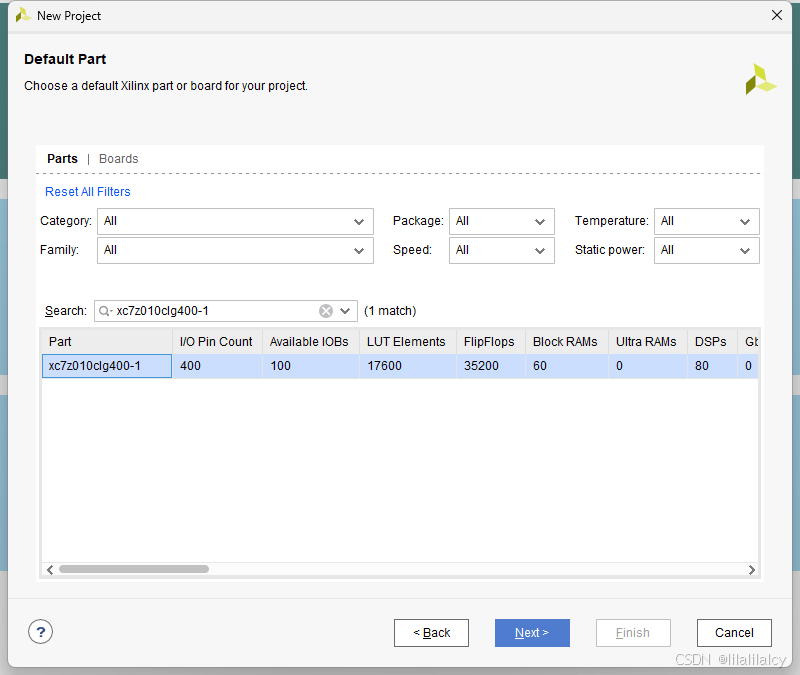

3.根据自己手上的开发板进行选择

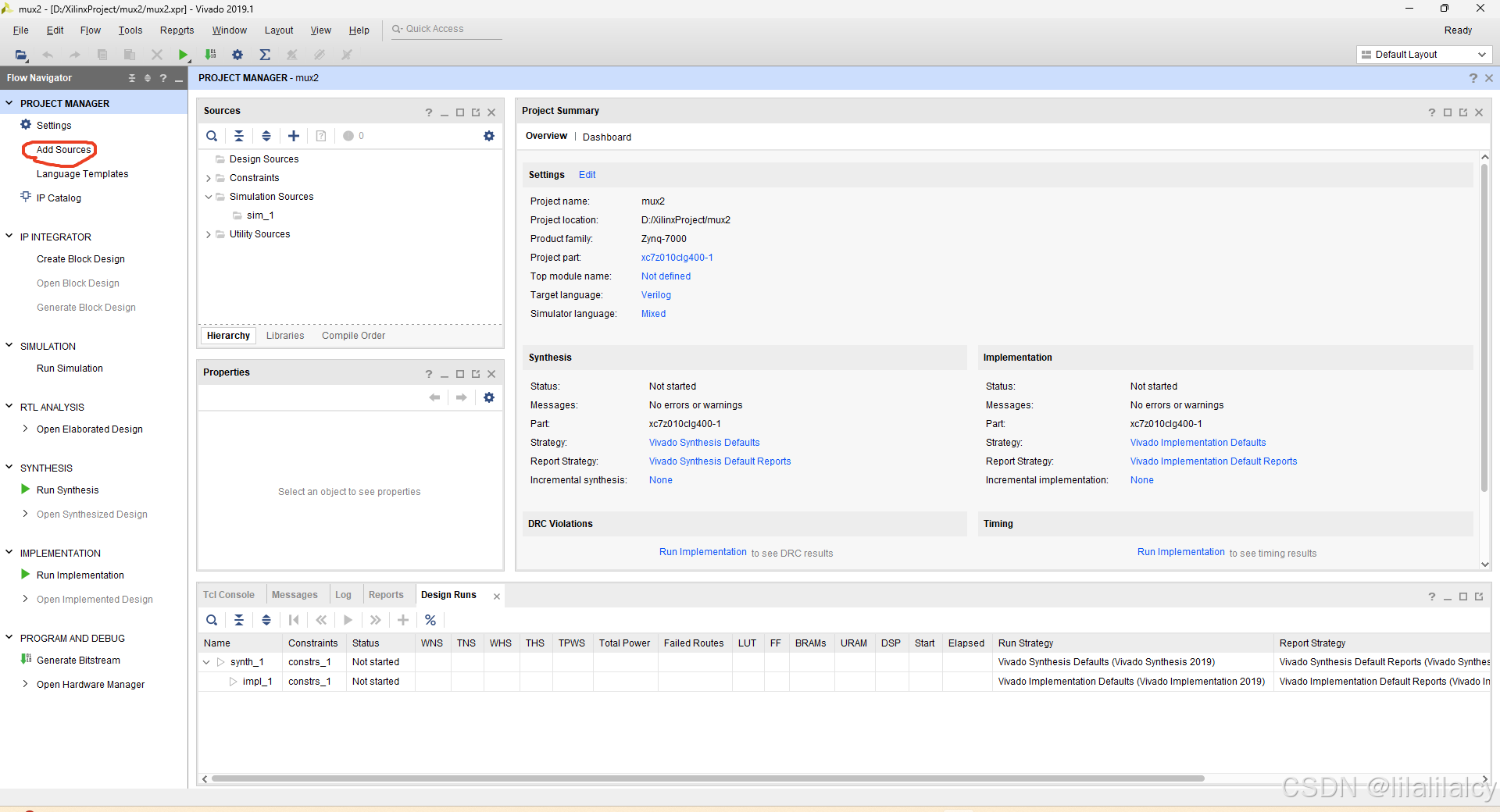

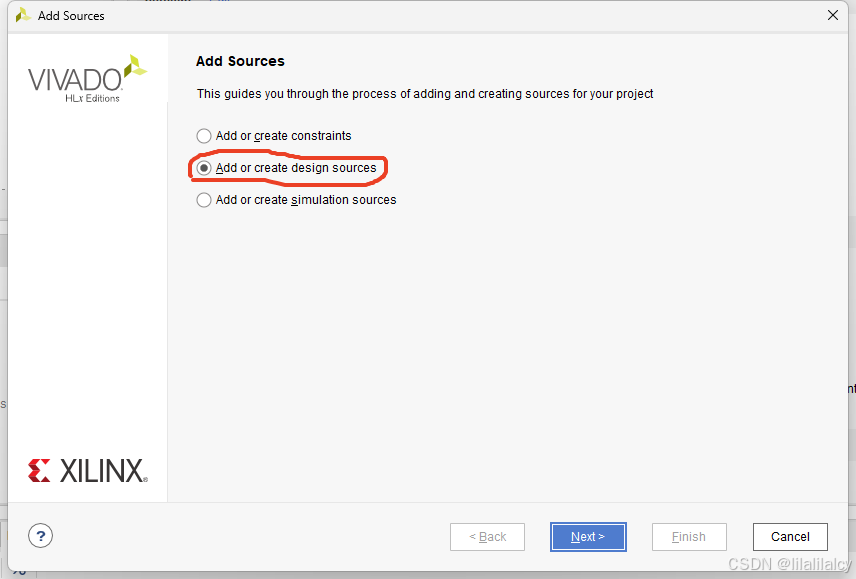

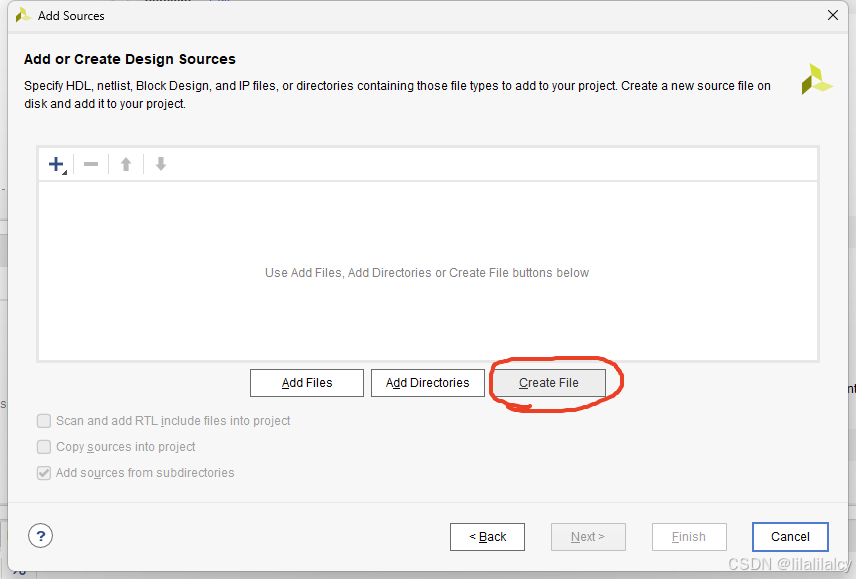

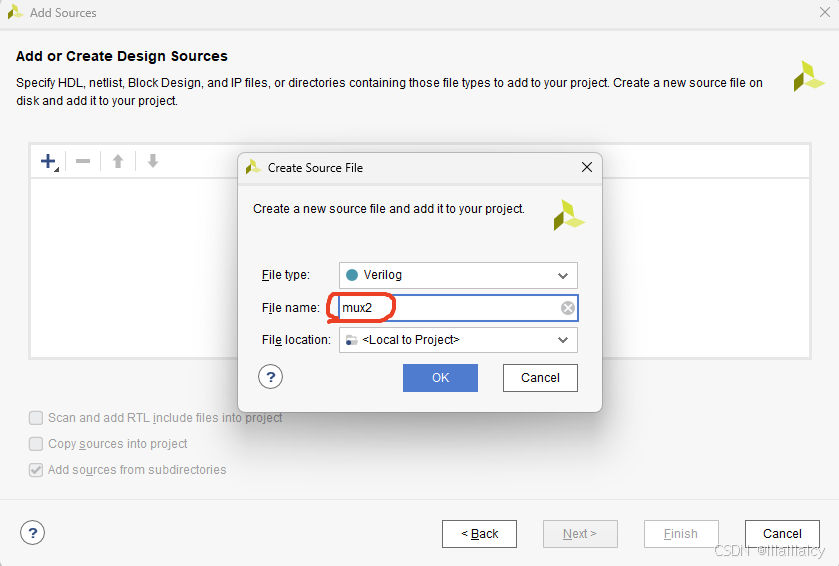

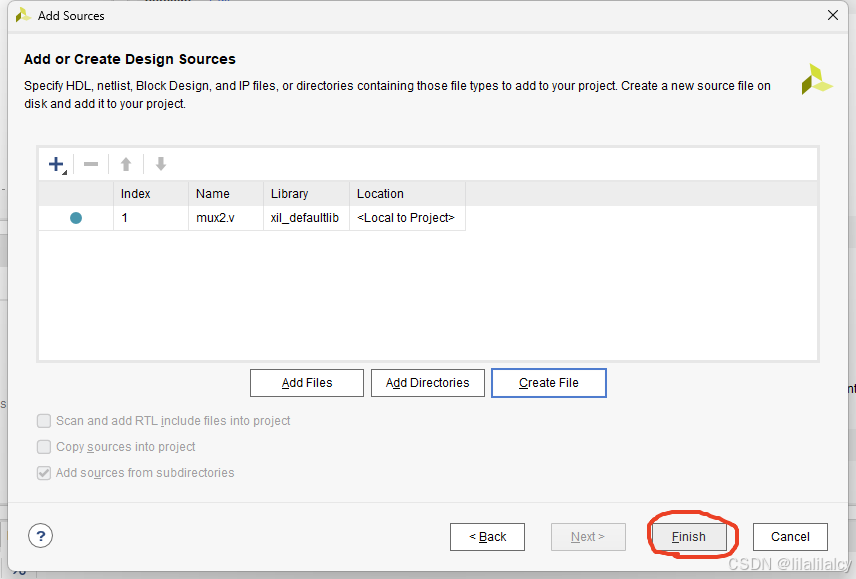

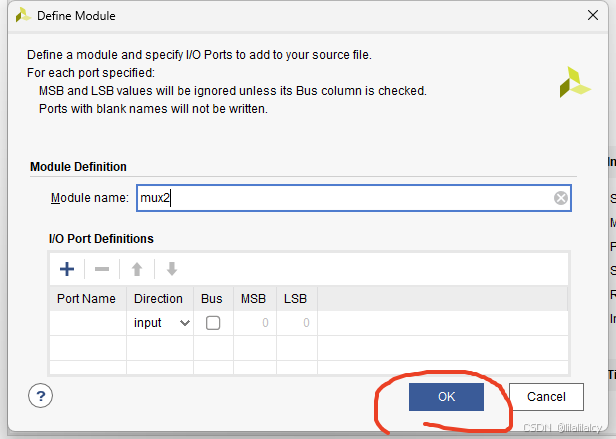

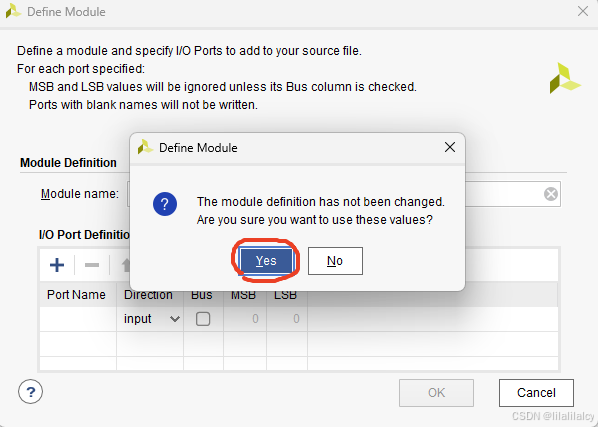

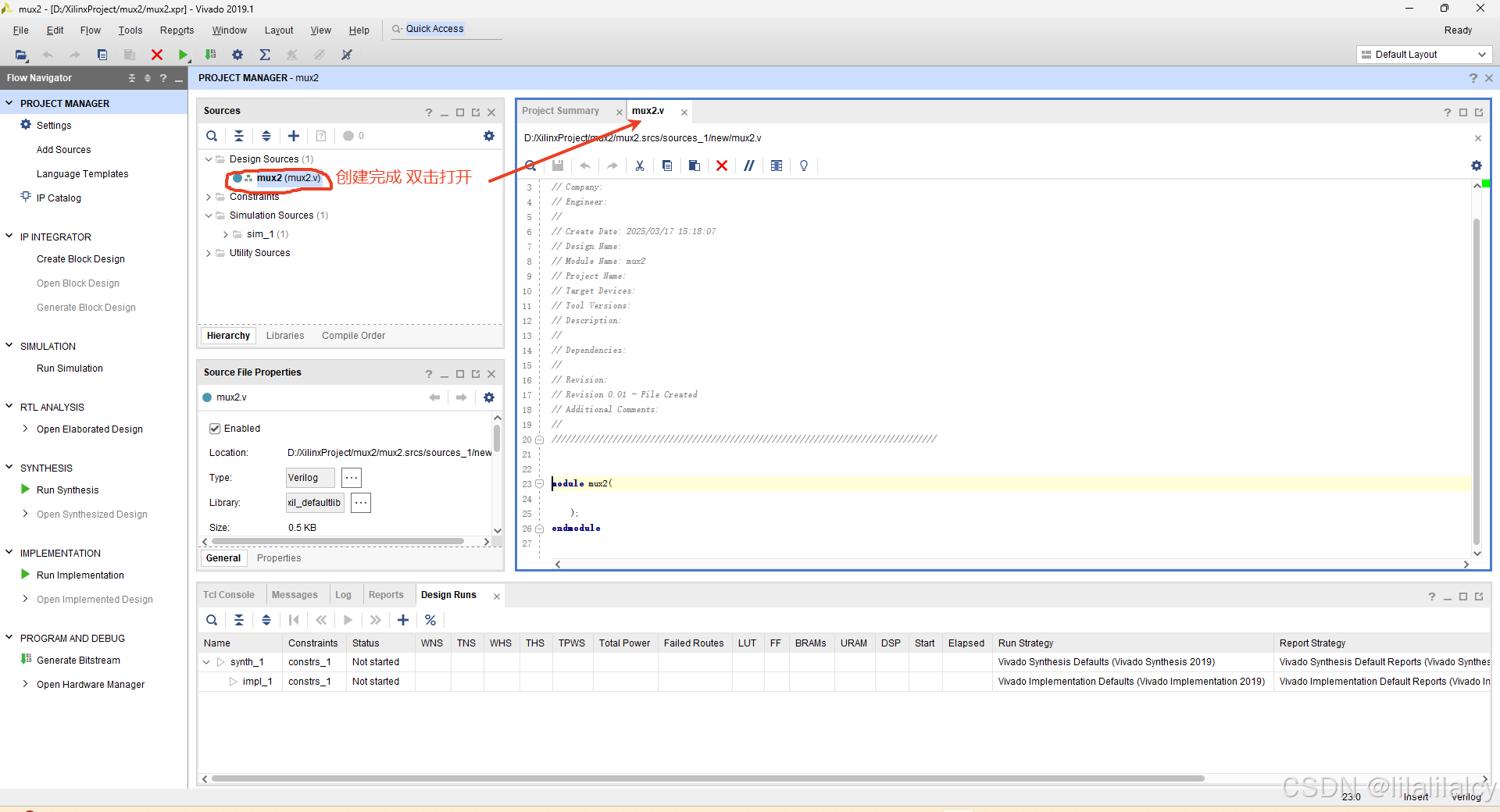

创建设计文件

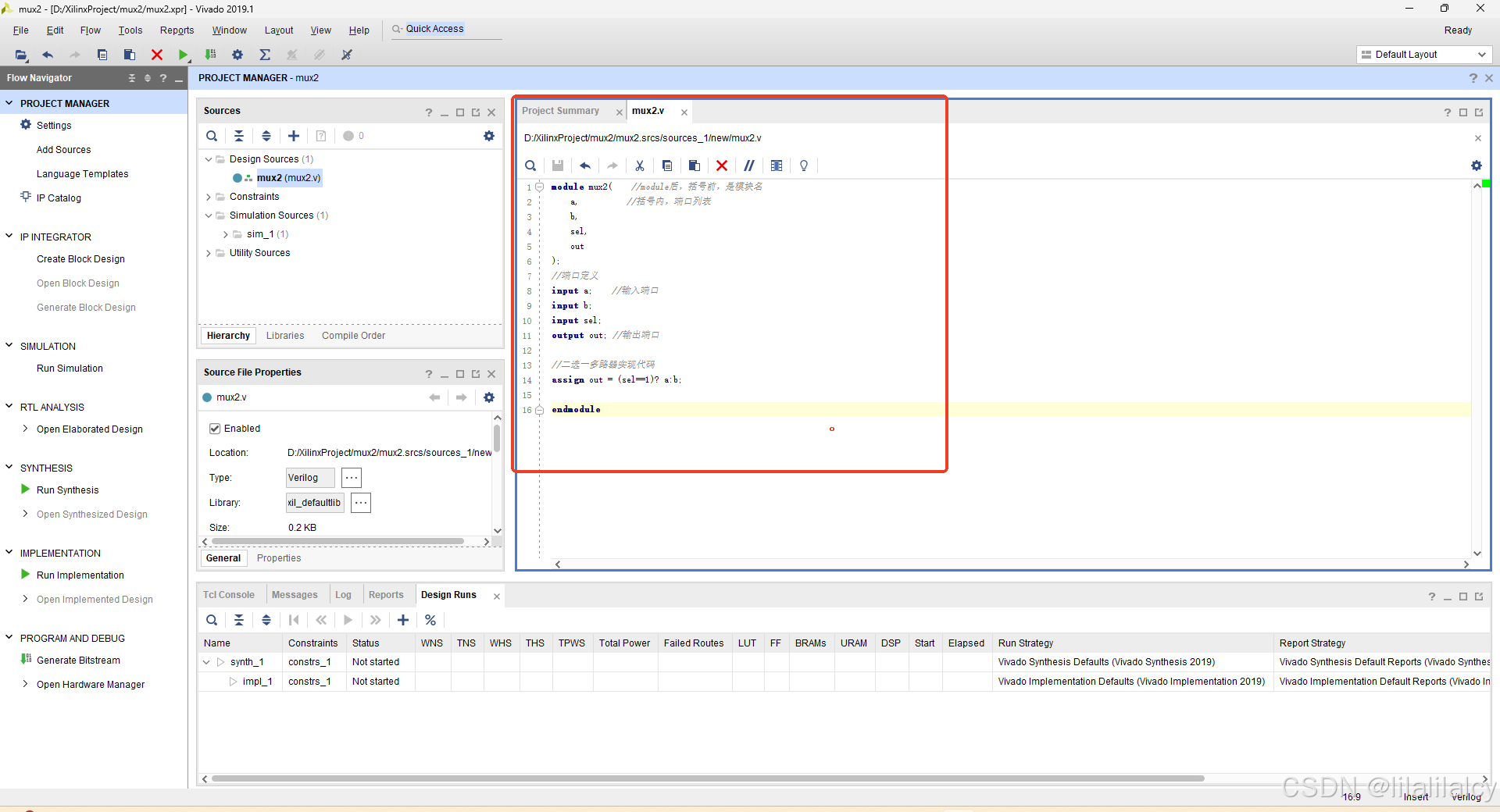

编写代码

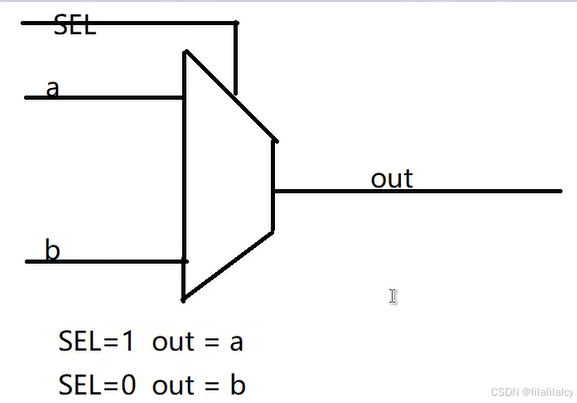

二选一多路选选择器构造与逻辑:

module mux2( //module后,括号前,是模块名

a, //括号内,端口列表

b,

sel,

out

);

//端口定义

input a; //输入端口

input b;

input sel;

output out; //输出端口

//二选一多路器实现代码

assign out = (sel==1)? a:b;

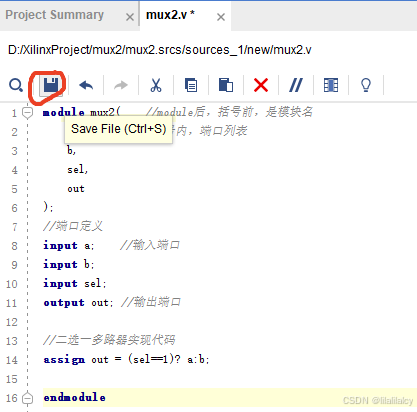

endmodule写完后,保存

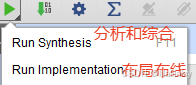

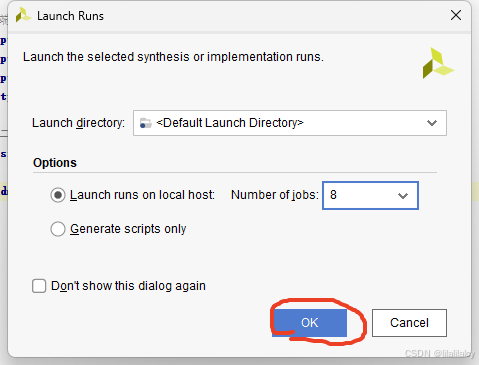

分析和综合

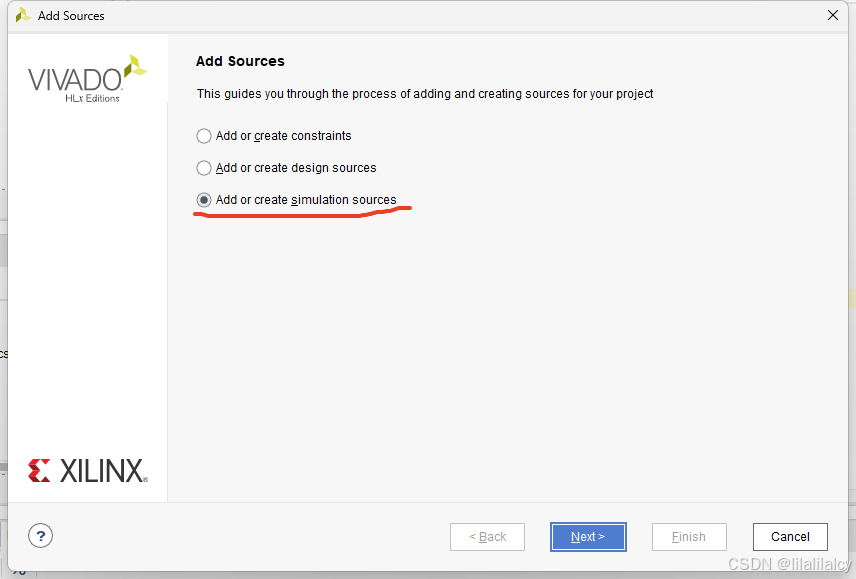

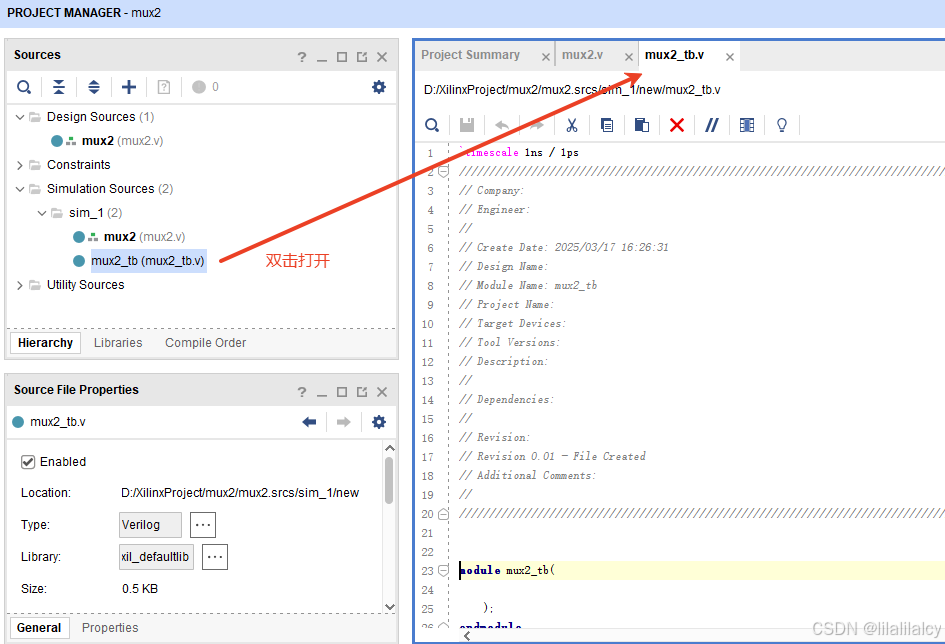

仿真验证(功能仿真)

验证思路:sel接地或者接Vcc时,给a和b输入0或1,观察out

写激励文件:

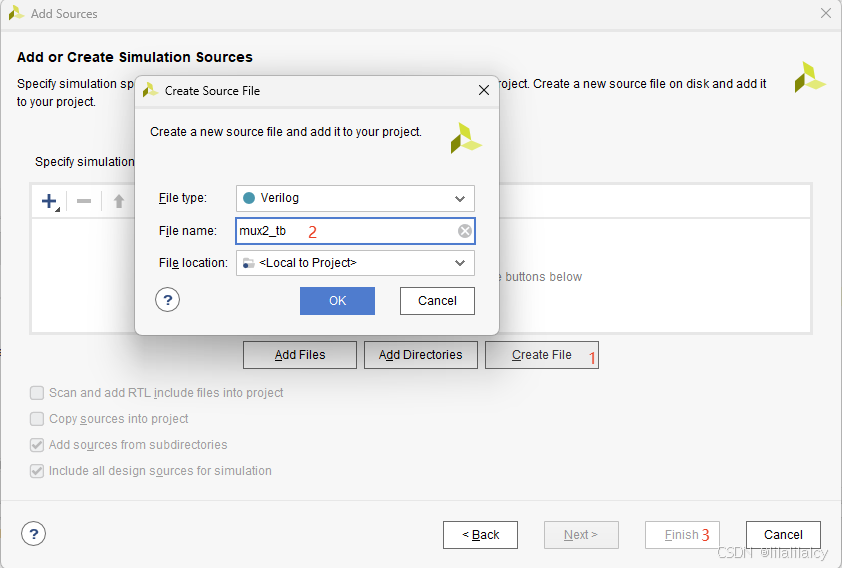

编写仿真文件:

`timescale 1ns/1ps

module mux2_tb();

reg s_a;//激励信号定义为reg型

reg s_b;

reg sel;

wire out;//观察用的输出 wire型

//例化模块

mux2 mux2_inst0( //前一个是模块名称 后一个是标签名称

.a(s_a),

.b(s_b),

.sel(sel),

.out(out)

);

//产生激励

initial begin

s_a=0;s_b=0;sel=0;

#200; //延时200ns

s_a=0;s_b=0;sel=1;

#200;

s_a=0;s_b=1;sel=0;

#200;

s_a=0;s_b=1;sel=1;

#200;

s_a=1;s_b=0;sel=0;

#200;

s_a=1;s_b=0;sel=1;

#200;

s_a=1;s_b=1;sel=0;

#200;

s_a=1;s_b=1;sel=1;

#200;

end

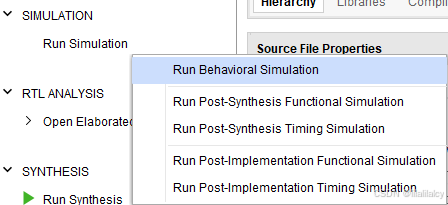

endmodule功能仿真

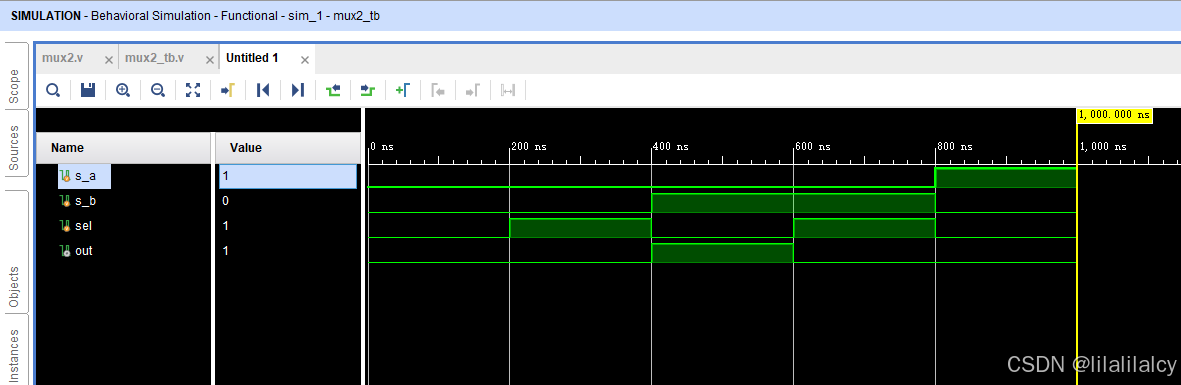

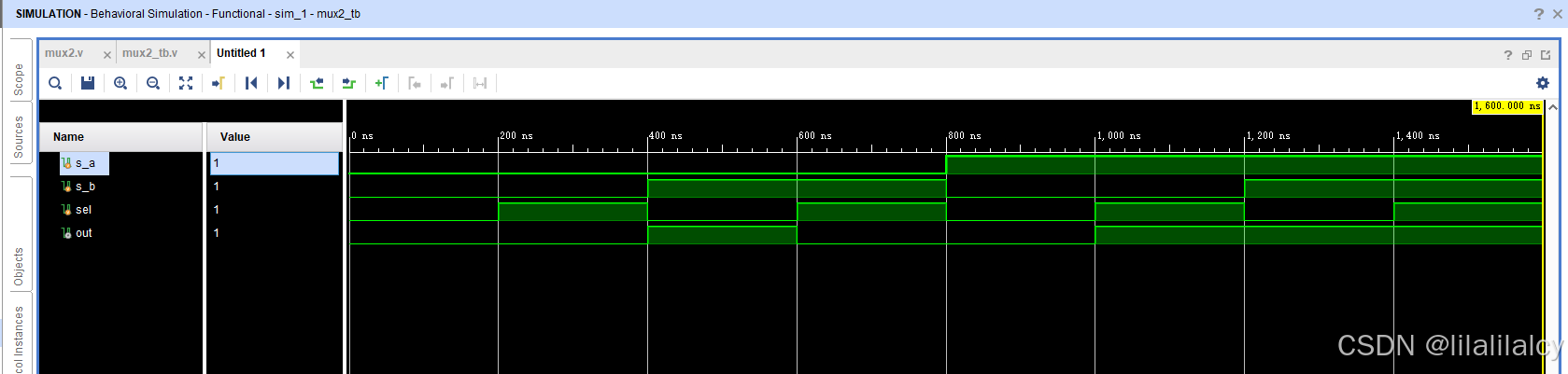

仿真结果:

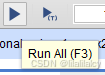

默认仿真到1000ns,但是我们需要1600ns,所以点这个,继续仿真

结果如下:

分析:a、b或者sel变化,out同时变化。

布局布线

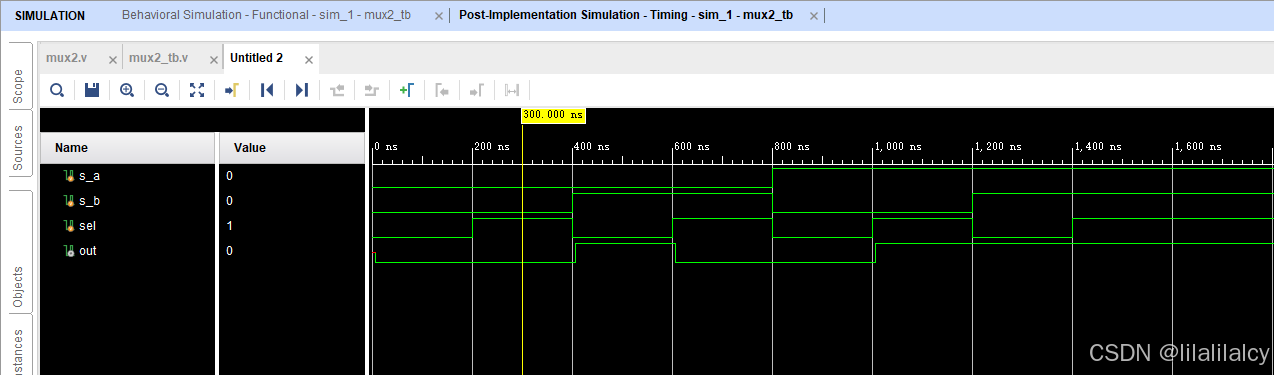

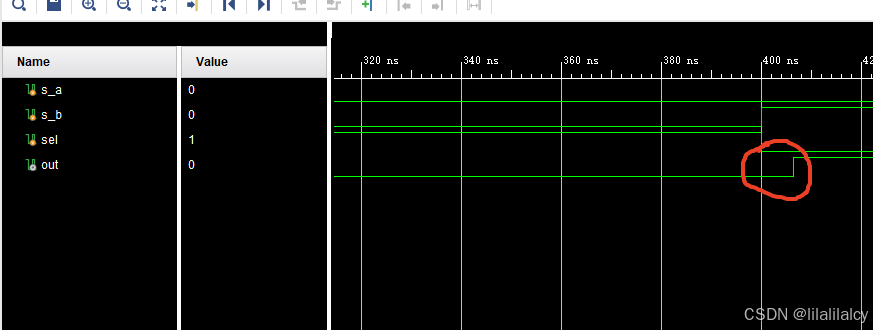

时序仿真

分析:输出变化有延迟。信号从输入端口进来,到内部经过传输,最后实现逻辑功能,有一定的延迟。这是真实存在的传输延迟。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?