软件版本:VIVADO2017.4

操作系统:WIN10

硬件平台:MK7160FA

5.1概述

MK7160FA 开发板的4路SFP+光口均与xc7k160T芯片的GTX 串行收发器连接。使用 FFG676 封装的xc7k160t可以支持高达 12.5Gb/s 的传输速率。因此,在MK7160FA 开发板上可以实现万兆光纤以太网传输。

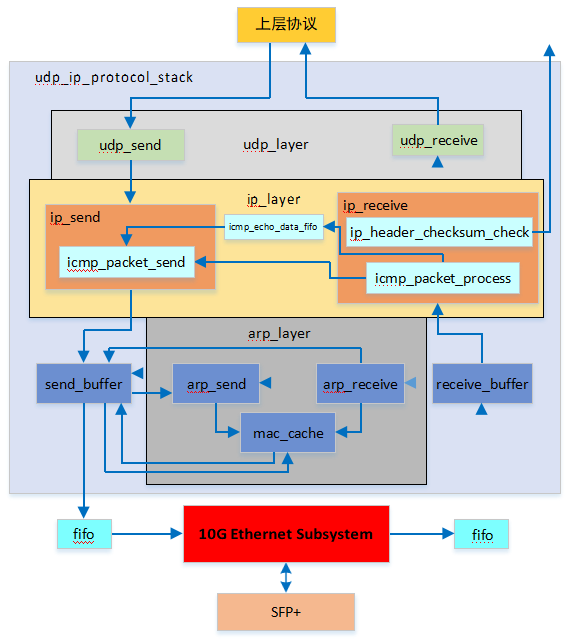

在 MK7160FA 开发板中实现万兆网 UDP 传输的基本逻辑框架如下图所示。FPGA 程序基于米联的新版 UDP IP 协

议栈以及Xilinx 的 IP 核 10G Ethernet Subsystem 而实现。

本文档对应 2 个例程,分别为 udp_ip_10g 和 udp_ip_10g_4ch,分别实现单路和 双路万兆 UDP 光纤传输。

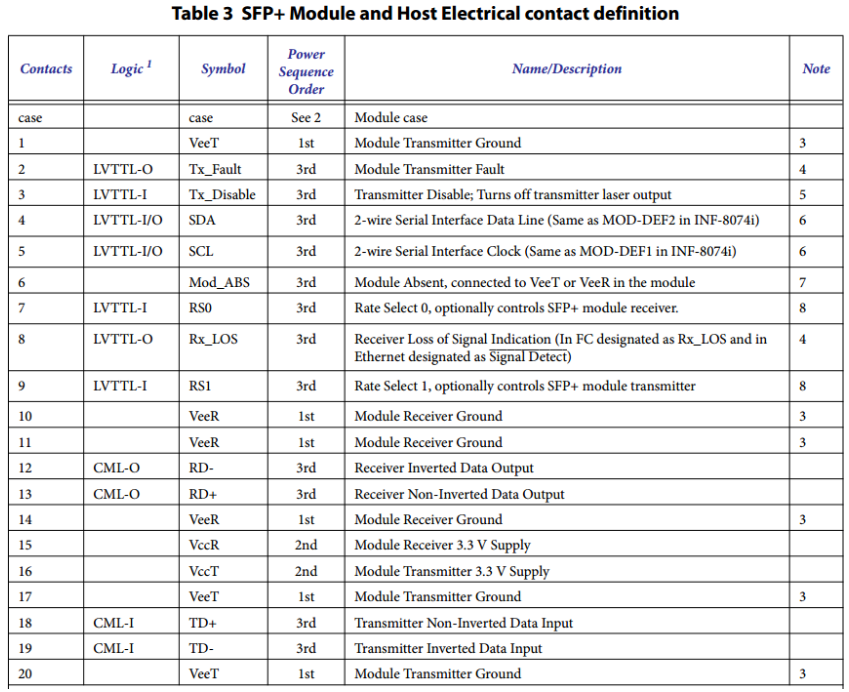

5.2 SFP+接口

MK7160FA 上有4 个SFP+屏蔽笼。MK7160FA 上有4 个SFP+屏蔽笼。SFP+屏蔽笼可以插入千兆或万兆光模块。SFP+信号定义与SFP 一致,如下图所示。

5.3 IP 设置

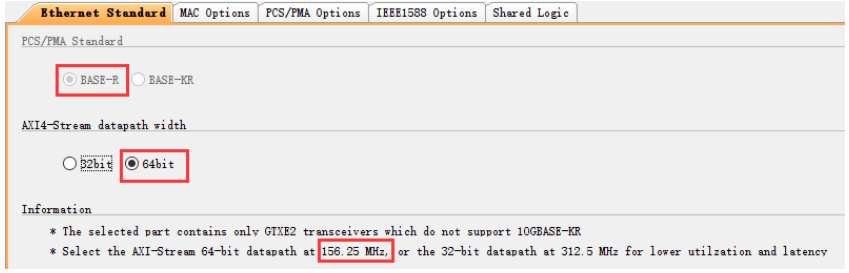

将 IP 核 AXI-Stream 的用户数据接口位宽设为 64bit,此时对应用户接口时钟频率为 156.25MHz。如下图所示。

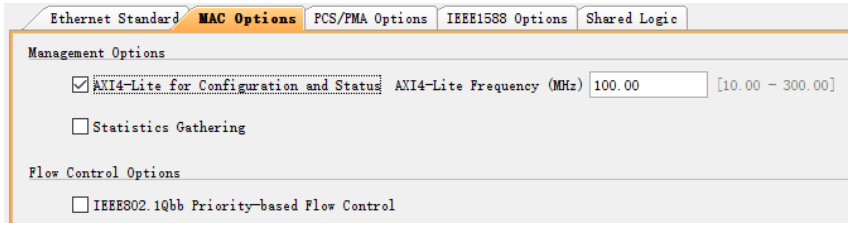

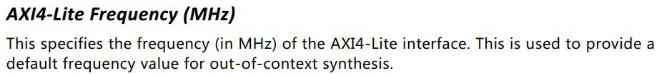

将 AXI-Lite 配置接口时钟频率设置为 100MHz,当然用户也可以自由选择其他的频率。不使用参数统计和优先级流量控制功能。如下图所示。

时钟频率的设置仅对 IP 核单独综合有效。如下图。

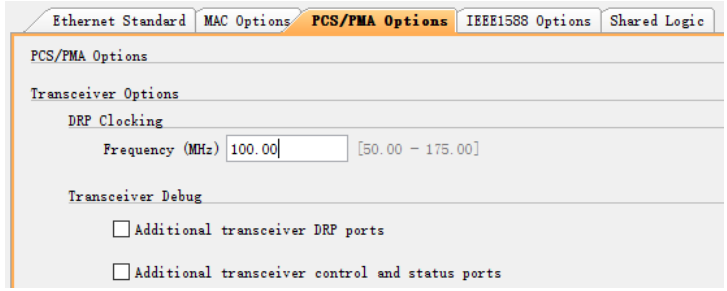

将 GTX 动态重配置端口DRP 的时钟设为 100MHz, Debug 功能不作使用,如下图。

该时钟频率设置也仅对单独综合有效。如下图。

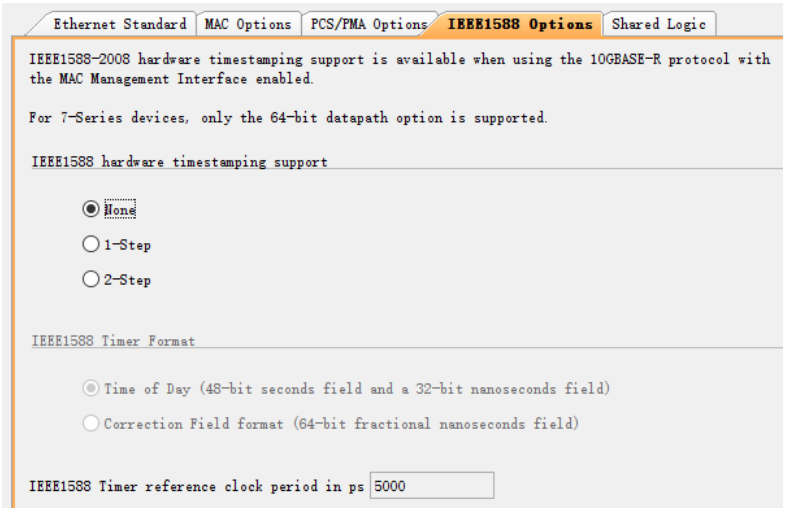

1588 同步功能一般针对某些需要进行网络时间同步的场合,如音视频传输。仅用作数据传输时无需使用。因此

这里不启用 1588 功能。如下图。

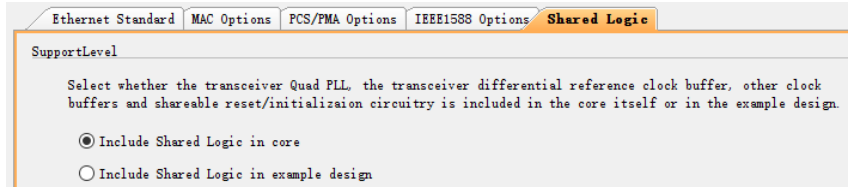

当设计中只包含 1 个此 IP 核时,应当将可共享的逻辑资源和硬件模块包含在 IP 核内部,这样会减少所生成的模块数量,简化设计。如下图所示。

当设计中需要同时使用若干个此 IP 核,且所使用的GTX 均位于同一个GTX BANK 中。此时,只需其中 1 个IP 核内部的共享资源(MMCM、QUADPLL、GTX 参考时钟等)便可以满足所有 IP 核的需求,即选择将共享资源包含在 IP 核内部。其余 IP 核将这些共享资源从其内部剔除即可,即选择将共享资源包含在 example 中。如下图所示。

<

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

9478

9478

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?