对于数字波束形成的相控阵,本地振荡器(LO)生成的一种常见实现方法是将一个公共参考频率分配给分布在天线阵列内的一系列锁相环(PLL)。对于这些分布式锁相环,当前文献中没有很好地记录评估组合相位噪声性能的方法。

在分布式系统中,公共噪声源是相关的,如果保持分布式噪声源不相关,则在RF信号合路时就可以减少它们。可以直观地评估系统中的大多数组件。对于PLL,噪声传递函数与环路中的每个组件相关联,它们的贡献是控制环路中的每个组件以及任何频率转换的函数。当尝试评估合路的相位噪声输出时,这会增加复杂性。通过建立在已知的PLL建模方法上,以及对相关贡献者和不相关贡献者的评估,本文提出了一种跟踪跨频率偏移的分布式PLL贡献的方法。

数字波束成形带来的问题

在任何无线电系统中,对接收器和激励器的LO生成的实现都要进行仔细的设计。随着相控阵天线系统中数字波束赋形的激增,由于LO信号和参考频率向大量分布式接收机和激励器(即发射机)的分配,设计变得更加复杂。

在系统体系结构级别上的权衡是分配所需的LO频率或分配较低的频率参考,并在物理上接近使用点的位置创建所需的LO。一个易于使用且高度集成的选项可以通过PLL在本地创建LO。下一个挑战是评估来自各种分布式组件以及集中式组件的系统级相位噪声。

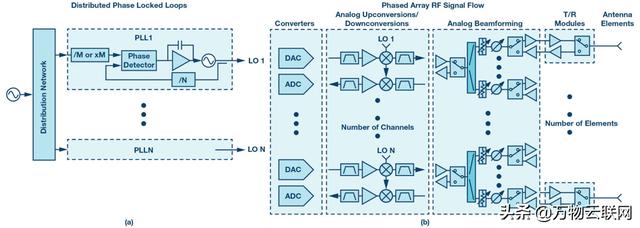

可以将具有分布式锁相环的系统视为图1中所示的系统。将公共参考频率分配给许多锁相环,每个锁相环都会产生一个输出频率。假定图1a的LO输出为图1b中混频器的LO输入。

图1

图1.分布式系统。每个振荡器锁相到一个公共参考振荡器。 LO信号1到N被施加到相控阵所示混频器的LO端口。

系统设计人员面临的一个挑战是跟踪分布式系统的噪声贡献,了解相关和不相关的噪声源,并对整个系统的噪声进行估算。在PLL中,噪声传递函数加剧了这一挑战,噪声传递函数既是PLL中的转换频率的函数又是环路带宽设置的函数。

动机:锁相环合路的测量示例

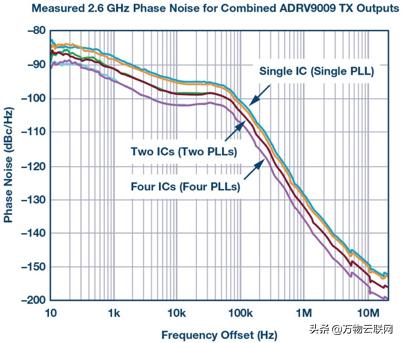

图2给出了组合PLL的测量示例。该数据是通过组合多个ADRV9009收发信机的发送输出而获得的。显示了单个IC,两个合路IC和四个合路IC的测试情况。

在此数据集的情况下,将IC合路在一起,可见10logN的改善。为了获得结果,需要一个低噪声晶体振荡器参考源。下一部分中该模型的动机是推导一种方法,用于计算该测量如何在具有许多分布式收发信机的大型阵列中进行缩放,并且更普遍地适用于具有分布式PLL的任何体系结构。

图2

图2.组合的两个锁相环的相位噪声测量结果。

锁相环模型

PLL中的噪声建模已得到充分证明(参考1-5)。输出相位噪声图如图3所示。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

949

949

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?