世界上没有PLL不能生成的时钟,如果一个PLL不够,那就两个 —— 尼古拉斯·赵四

前两天调试一个项目的时候遇到一个pll的问题,感觉以后也会遇到类似的问题,记录一下。

调试平台

调试平台如下图所示,基带主时钟为56MHz,由外部输入125MHz的参考时钟给到PLL生成,DDC做一个14MHz的频谱搬移,DDC时钟也是56MHz,使用Cordic算法生成cos和sin信号(其实这里不需要用Cordic,因为采样率是cos信号频率的4倍,是整数倍,甚至都不需要乘法器,直接变换符号就可以了)。

// 4倍采样率的cos sin信号

cos: 1 0 -1 0

sin: 0 1 0 -1

// 相位左移pi/4

cos: 1 -1 -1 1

sin: 1 1 -1 -1

问题的现象是频偏估计值始终在2600Hz左右。

分析

最开始怀疑的是收发频合存在频偏,但是经过频谱仪测试之后排除了,还做了很多其他尝试,最后才怀疑到pll上。

如果是pll有问题,那么产生的cos、sin信号的频率就不对,实际的频率应该是13.9974Mhz,这样根据公式推算,DDC的时钟频率为55.9896MHz.

F

c

o

s

=

F

s

×

M

2

N

F_{cos} = \frac{Fs \times M}{2^N}

Fcos=2NFs×M

55.9896

=

13.9974

×

4

55.9896 = 13.9974\times4

55.9896=13.9974×4

修改频率控制字 M M M,让55.9896MHz的时钟产生14MHz的cos、sin信号,频偏就消失了,与推测结果吻合。同时将时钟输出到频谱仪查看,频谱仪显示频率也确实为55.9896MHz,而输入的125MHz参考时钟是准确的,说明确实是pll产生的时钟有问题。

PLL分析

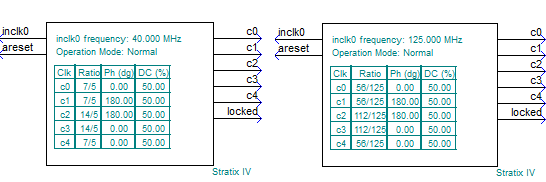

PLL为什么会出现这样的问题?个人推测是PLL的除法器和乘法器资源有限,并不能进行任意的分频,如下图,同样是生成56MHz的时钟,不同频率的参考时钟输入,其需要的乘除法是不一样的。

下图是典型的PLL结构,我们知道PLL是硬核,所以它的资源肯定是有限的。但是为什么在配置PLL IP核时,actual setting没有报错?由于没有找到更多的资料,所以分析就只能到这里了。

解决方案: PLL级联

一个PLL硬核的资源有限,不能做到任意分频,但是2个PLL呢?根据这个思路,我们可以通过PLL级联的方式生成准确的56MHz时钟。

我们这里是先用一个PLL(参考时钟125MHz)生成40MHz的时钟作为第二个PLL的参考时钟,这样第二个PLL就可以输出准确的56MHz时钟了(频谱仪测试通过)。

20190417 更新

看了下stratix 4的资料,PLL的原理是设置 V C O VCO VCO的频率,然后 V C O M \frac{VCO}{M} MVCO的频率和 r e f c l k N \frac{refclk}{N} Nrefclk通过鉴频鉴相器(PFD)锁定VCO, c 0 、 c 1 、 … 、 c 8 和 M c_0、c_1、…、c_8和M c0、c1、…、c8和M是后缩放计数器,计数范围 1 1 1~ 512 512 512,并且可以级联,VCO通过它们进行分频输出。所以VCO的频率是设置为所有输出时钟频率和 r e f c l k N \frac{refclk}{N} Nrefclk的最小公倍数。

我这里用125MHz输入做参考时钟生成56MHz和112MHz,VCO的频率是560MHz,

N

=

25

N=25

N=25,

M

=

112

M=112

M=112,这样看来一个PLL的资源是够用的,可是为什么输出的频率不是准确的56MHz呢?

.

.

.

.

.

.

.

.

.

.

.

.

.

1350

1350

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?