欢迎FPGA工程师加入官方微信技术群

点击蓝字关注我们FPGA之家-中国最好最大的FPGA纯工程师社群

FPGA - Zynq - 加载 - BootROM

题外话

BootROM

BootROM Header Definition

BootROM Header Searching and Loading

总结

题外话

第一次使用Markdown编写博客,之前都是直接用word或者onenote写好之后复制到博客上,发现文字编排效果很差,不忍翻阅下去。所以转投markdown怀抱。

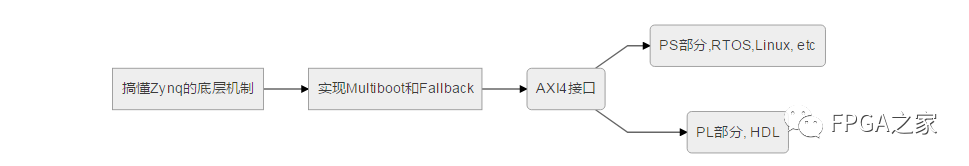

这里将会新开一个章节,专门更新关于Zynq的一些心得,我希望能够完成以下几个方面:

因此,我希望能够通过Zynq片上强大的FPGA资源和ARM资源,来完成FPGA工程师和ARM工程师的协同工作,一般来说FPGA部分来完成所有高速接口驱动以及一些高速算法(并行独立或者串行复用),然后ARM部分来完成通信协议的实现,不管是私有的(如用户自定义的串口协议的封包和解包)或者标准的(如TCP/IP或者USB等),以及FPGA的流程控制,错误状态控制还有远程更新控制等。

为了完成上述化学反应,一个很重要的方面就是如何协调ARM和FPGA(都是Zynq片上的资源),这个其实很多开发板的学习手册都已经给出了答案,那就是应用AXI4总线。那剩下的问题就是,如何实现Multiboot以及fallback。

因为在S6或者其他7系列的FPGA中,是有一套非常成熟的FPGA加载机制(Xilinx有很详细的指导手册),但是来到Zynq时代,这个方式变了。为什么呢?因为现在zynq上有ARM了,所有的加载工作实际上可以借由ARM来实现,这无疑也给用户带来了灵活的操作空间,即用户可以自己整一套属于自己的,满足要求的加载方式,这也是本文研究的重点:解析Zynq的加载方式。

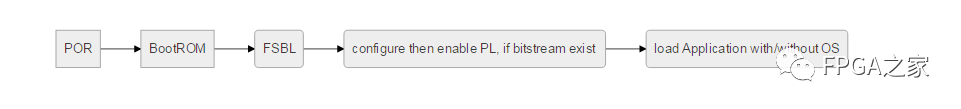

这里将通过对比Zynq的TRM和FSBL源码,来一步一步解析Zynq的加载流程,如下所示

运行流程简单的说就是:

触发条件 POR或者non-POR

ARM加载BootROM,这个程序停留在Zynq内部ROM,用户无法修改,用于实现搜索FLASH中的BootROM header,然后根据Header(这个header在整个FLASH中至少需要一个,Xilinx的软件会自动整合出来这哦头文件)信息,将FSBL加载到OCM(on chip memory)

开始运行FSBL,进一步加载Bitstream(PL用,如果有bit文件在FLASH中的话)或者其他镜像(PS用,裸机或者带系统)

run 上述的其他镜像,裸机或者RTOS的话直接run,linux的话需要先运行u-boot

BootROM

永远问自己,我们的芯片(在这里是Zynq)在POR复位或者non-POR 复位后,ARM是怎么样一步一步最终来到用户的main.c,对FPGA工程师而言,就是FPGA是怎么完成初始化任务的。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

234

234

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?