简介:本压缩包资源为初学者提供了FPGA实现HDLC协议的入门级教程,包括使用VHDL语言编写的代码实例。HDLC是一种同步通信数据链路层协议,该教程详细讲解了如何在FPGA硬件上实现HDLC协议的相关模块,包括接收、发送和错误校验过程。源码文件包括接收和发送端的FIFO缓冲区、不同校验方式的实现代码,以及关于HDLC协议的PowerPoint演示文稿。通过学习这些资料,可以加深对HDLC协议和FPGA编程的理解,为在通信等领域的应用打下基础。

1. FPGA与VHDL基础

在现代数字电路设计中,现场可编程门阵列(FPGA)因其灵活性和高性能而成为关键组件。VHDL(Very-High-Speed Integrated Circuit Hardware Description Language)是一种硬件描述语言,用于通过高级抽象来设计复杂的数字系统,尤其是FPGA。在深入探讨VHDL和FPGA在高速通信协议如HDLC的实现之前,我们先从基础开始了解FPGA与VHDL。

1.1 FPGA的概念及应用

FPGA是一种可以由用户定义其逻辑功能的半导体设备。它们具有可重复编程特性,这意味着可以无数次修改电路设计,而无需更改物理硬件。FPGA的这些特性使其在需要频繁更改设计或者需要快速原型设计的场合中尤为有用。从高速网络路由器到复杂的数据采集系统,FPGA的高性能和灵活的配置能力为各种应用提供了可能。

1.2 VHDL的简介

VHDL作为一种硬件描述语言,具备强大的能力,能够描述复杂的硬件逻辑。从简单的逻辑门到复杂的处理器,都可以通过VHDL来表达。其主要特点包括并行操作、模块化设计和可重用性。VHDL允许设计者以类似于软件编程的思维来设计硬件,这让设计和调试过程变得更为高效。

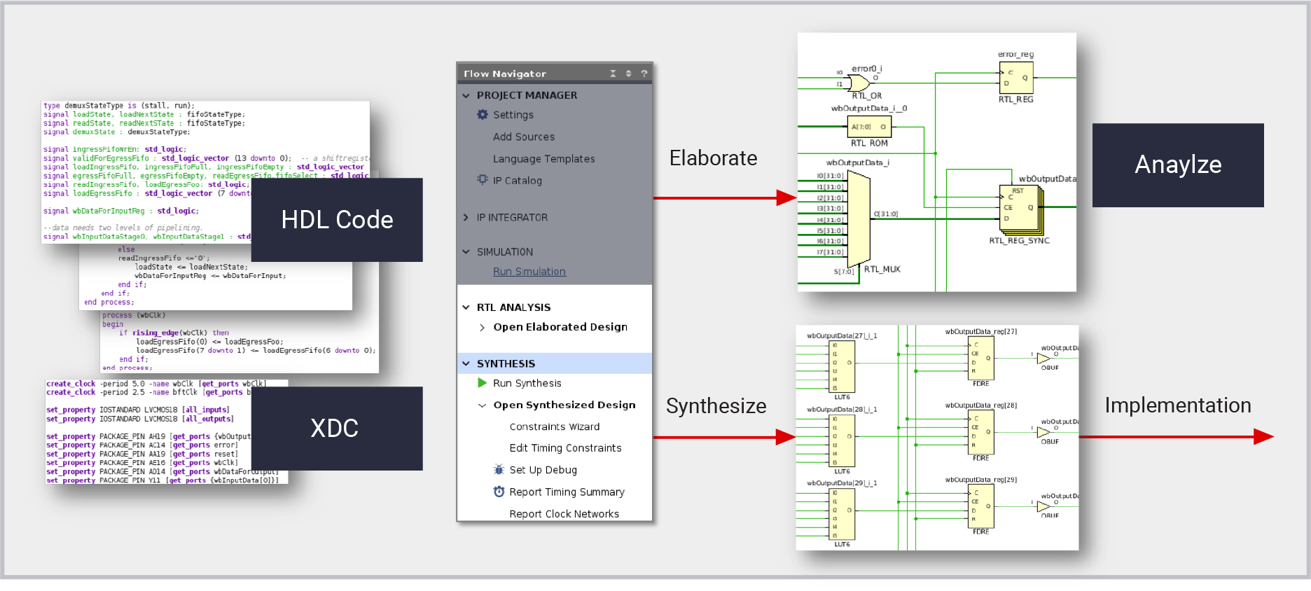

1.3 FPGA与VHDL的结合

VHDL是实现FPGA设计的最常用语言之一。VHDL描述的逻辑可以通过专门的软件编译和综合,最终生成可以在FPGA上运行的配置文件。这种结合使得FPGA能够实现各种自定义功能,从而为高速数据处理和通信提供了强大的硬件平台。

1.4 代码示例及解释

让我们通过一个简单的VHDL代码段来演示如何描述一个2输入与门(AND gate):

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity AND_gate is

Port ( A : in STD_LOGIC;

B : in STD_LOGIC;

Y : out STD_LOGIC);

end AND_gate;

architecture Behavioral of AND_gate is

begin

Y <= A and B;

end Behavioral;

这段代码定义了一个名为 AND_gate 的实体,拥有两个输入端口A和B以及一个输出端口Y。在 architecture Behavioral 部分,我们描述了这个与门的行为:输出Y是输入A和B的逻辑与操作结果。这是通过 Y <= A and B; 这一行来实现的。这个例子展示了VHDL描述硬件逻辑的简洁性。

在下一章中,我们将探讨HDLC协议的原理与实现,这是在通信网络中常用的比特级同步协议,非常适合用FPGA结合VHDL来实现。

2. HDLC协议原理与实现

2.1 HDLC协议概述

2.1.1 HDLC协议的历史背景

HDLC(High-Level Data Link Control)是ISO(国际标准化组织)为数据通信设计的一种高级数据链路控制协议。HDLC协议的雏形起源于IBM的SDLC(Synchronous Data Link Control)协议,其设计初衷是为了提供一种可靠的数据传输方式,在多种通信介质上进行同步通信。随着计算机网络的发展,HDLC逐渐演变为一种通用的帧传输协议,被广泛应用于各种网络设备和通信链路中。

HDLC协议被定义为一种面向比特的协议,它采用帧的方式进行数据封装和传输,能够支持多种传输模式,包括异步平衡模式(ABM)、异步响应模式(ARM)和异步传输模式(ATM)。它能够在不保证数据传输顺序的情况下提供高效率和高可靠性。

2.1.2 HDLC协议的基本特点与优势

HDLC协议有以下特点:

- 透明传输 :HDLC协议能够保证数据传输的透明性,这意味着任何比特组合的数据都能被封装进帧中传输,而不会因为特殊数据的出现而产生错误。

- 流量控制 :HDLC协议内置了流量控制机制,通过监控传输和接收缓冲区的状态,动态调整数据发送速率,避免数据丢失。

- 错误检测与处理 :通过帧检验序列(FCS),HDLC能够检测传输过程中可能发生的错误,并采取措施如请求重传,以确保数据的准确性。

- 高效的多路复用 :HDLC协议支持多路复用,允许在一个物理链路上同时传输多个数据流。

HDLC协议的优势在于:

- 广泛的应用范围 :HDLC协议可以在多种通信环境下使用,包括卫星通信、无线通信以及现代的网络设备中。

- 高效的数据传输 :由于其高效的帧结构和流量控制机制,HDLC协议可以实现较低的传输延迟和较高的吞吐率。

- 良好的互操作性 :标准化的协议能够确保不同制造商生产的设备之间良好的互操作性。

2.2 HDLC帧结构分析

2.2.1 HDLC帧的组成与格式

HDLC帧由以下几部分组成:

- 标志字段(Flag) :标志帧的开始和结束,其值固定为

0x7E(即***),用于帧的同步和分界。 - 地址字段(Address) :标识数据链路上的一个站,长度可变,用于多点通信环境中的地址识别。

- 控制字段(Control) :指示帧的类型(信息帧、监督帧、无编号帧)和序列号,用于流量控制和错误恢复。

- 信息字段(Information) :携带有效载荷数据,其长度可变。

- 帧检验序列(Frame Check Sequence,FCS) :用于错误检测,采用CRC(循环冗余检验)算法。

HDLC帧的基本格式如下:

+--------+--------+--------+-----------+---------+

| Flag | Address| Control| Information| FCS |

| 8 bits | 8/16b | 8/16b | N bits | 16/32b |

+--------+--------+--------+-----------+---------+

其中 N 为信息字段的长度,当信息字段长度为0时,表示无信息帧。

2.2.2 控制字段的解析与应用

控制字段是HDLC帧中实现流量控制和错误恢复的关键部分。它由8或16位二进制数据组成,具体取决于协议的具体实现:

- 比特0 :总是设置为0。

- 比特1-2 :用于指定帧类型(信息帧、监督帧或无编号帧)。

- 比特3-4 :当使用16位控制字段时,这两个比特用于指示帧编号(帧序列号)。

- 比特5-6 :控制字段中可能包含附加的控制信息位,这依赖于帧类型。

信息帧(I帧)用于传输用户数据,监督帧(S帧)用于传输控制信息,如请求重传,确认帧等;无编号帧(U帧)用于传输协议管理信息。

在数据传输过程中,控制字段在确保信息的正确传输和同步的同时,还提供了流量控制功能。例如,接收方可以通过发送特定的S帧来指示发送方暂停发送,直至接收到更多缓冲空间的通知。

2.3 HDLC协议的同步机制

2.3.1 同步字节和标志字段的作用

同步字节(标志字段)在HDLC协议中起着至关重要的作用,确保了数据帧的正确同步。标志字段不仅标志着一个帧的开始和结束,而且也是接收设备在数据流中定位帧的边界的关键。由于HDLC是一种面向比特的协议,其标志字段的值必须在信息字段中被避免。为解决这一问题,HDLC采用了位填充(Bit stuffing)技术。

位填充技术原理是在发送端的传输数据中,每遇到5个连续的1就插入一个0,保证信息字段中不会出现与标志字段相同的 *** 。接收端在接收到数据后,要检查并删除这些被填充的0,恢复原始数据。

2.3.2 HDLC链路的建立和终止过程

HDLC链路的建立和终止是一个同步的过程。链路建立通常通过发送和接收一系列标志字段(或无编号帧)来完成,以确保双方通信设备的同步。链路终止则通过发送一个特殊序列的标志字段来实现,表示数据传输的结束。在链路终止过程中,还可能涉及特定的监督帧来确保数据的完整性,如在终止前完成未完成的帧传输。

此外,HDLC协议还定义了超时机制来处理未收到响应的帧,以及如何在发生错误时恢复链路同步。例如,若发送方在发送一定数量的数据帧后未收到应答(ACK),则会启动超时重传机制。如果在链路终止后,接收方未收到终止确认帧,则可能重发终止帧。

通过这些同步机制,HDLC协议确保了通信的可靠性和数据传输的完整性。

3. FPGA上HDLC协议的接收和发送流程

3.1 FPGA中的HDLC协议实现方法

3.1.1 FPGA实现HDLC协议的设计思路

在FPGA中实现HDLC协议,设计的起点是理解HDLC协议的细节和特点,包括其帧结构、控制字段、同步机制等。为了在FPGA中实现这一协议,设计者需要创建一个能够处理这些细节的硬件描述。设计的主要思路是将协议的各个部分转化为硬件逻辑,并使用VHDL或Verilog等硬件描述语言来描述这些逻辑。

硬件逻辑设计的层次化和模块化是关键。这意味着将HDLC协议的不同功能分离到独立的模块中,例如,一个模块用于帧的发送,另一个用于帧的接收,第三个用于错误检测和处理等。这种模块化设计有助于代码的维护和未来的升级。

3.1.2 VHDL代码中HDLC协议的模块化设计

-- VHDL代码片段:HDLC协议模块化设计

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.NUMERIC_STD.ALL;

entity HDLC_Transceiver is

Port (

clk : in STD_LOGIC;

rst : in STD_LOGIC;

rx_data : in STD_LOGIC_VECTOR(7 downto 0);

rx_valid : in STD_LOGIC;

tx_data : out STD_LOGIC_VECTOR(7 downto 0);

tx_request : out STD_LOGIC;

tx_busy : in STD_LOGIC;

-- 更多端口定义...

);

end HDLC_Transceiver;

architecture Behavioral of HDLC_Transceiver is

-- HDLC接收模块声明

component HDLC_Receiver is

-- 模块端口定义...

end component;

-- HDLC发送模块声明

component HDLC_Transmitter is

-- 模块端口定义...

end component;

-- 实例化接收和发送模块

signal hdlc_rx_to_tx : hdlc_signal_type;

signal hdlc_tx_to_rx : hdlc_signal_type;

begin

-- 接收模块逻辑

receiver : HDLC_Receiver

port map (

-- 映射端口...

);

-- 发送模块逻辑

transmitter : HDLC_Transmitter

port map (

-- 映射端口...

);

-- 接收和发送模块之间的交互逻辑

-- ...

end Behavioral;

在这个VHDL代码示例中,我们定义了一个名为 HDLC_Transceiver 的实体,它包含了所有必要的端口来接收和发送数据,以及与其他系统组件进行通信。然后,在架构体中,我们声明了两个组件: HDLC_Receiver 和 HDLC_Transmitter ,分别用于处理接收和发送逻辑。在实际的应用中,这些模块会被进一步定义和实现,以完成各自的功能。

3.2 HDLC接收模块的设计与实现

3.2.1 字符和帧的接收处理逻辑

HDLC接收模块负责将串行接收到的比特流转换成完整的帧结构。这个过程涉及位同步、字符定位、以及帧的识别和校验。通常,设计者会使用一个状态机来控制接收逻辑的流程。

-- VHDL代码片段:HDLC接收状态机

type hdlc_state is (ST_IDLE, ST_RECEIVING, ST_CHECK CRC, ST_FRAME_END);

signal state : hdlc_state := ST_IDLE;

process(clk, rst)

begin

if rst = '1' then

state <= ST_IDLE;

elsif rising_edge(clk) then

case state is

when ST_IDLE =>

-- 空闲状态的逻辑...

when ST_RECEIVING =>

-- 接收比特流的逻辑...

when ST_CHECK_CRC =>

-- CRC校验的逻辑...

when ST_FRAME_END =>

-- 帧结束处理的逻辑...

end case;

end if;

end process;

在上述代码片段中,我们定义了一个状态机 hdlc_state ,它可以处于 ST_IDLE 、 ST_RECEIVING 、 ST_CHECK_CRC 或 ST_FRAME_END 状态。在每个状态中,接收模块执行不同的任务:空闲时等待帧的开始,接收时同步并收集数据,校验时执行CRC计算,以及在帧结束时处理接收到的帧。

3.2.2 接收过程中的错误检测与处理

HDLC协议要求具备较强的错误检测能力,因此接收模块还必须能够检测和处理各种潜在的错误情况,比如帧校验序列(FCS)错误、帧长度异常、格式错误等。

-- VHDL代码片段:HDLC接收错误处理

if (FCS calculated != FCS received) then

-- 发现CRC校验错误

error <= '1';

-- 发出错误信号,进行相应的错误处理逻辑

end if;

if (frame_length < MIN_FRAME_LENGTH or frame_length > MAX_FRAME_LENGTH) then

-- 发现帧长度错误

error <= '1';

-- 发出错误信号,进行相应的错误处理逻辑

end if;

if (control_field /= EXPECTED_CONTROL_FIELD) then

-- 发现控制字段错误

error <= '1';

-- 发出错误信号,进行相应的错误处理逻辑

end if;

上述代码展示了如何处理几种常见错误。如果检测到任何错误,接收模块将设置错误标志位,并触发相应的错误处理逻辑,这可能包括丢弃错误帧或通知上层协议。

3.3 HDLC发送模块的设计与实现

3.3.1 数据封装与帧的发送流程

HDLC发送模块负责将上层数据封装到HDLC帧中,并通过FPGA的I/O接口发送出去。这涉及到数据的封装、CRC校验码的计算以及帧的构造。

-- VHDL代码片段:HDLC帧封装过程

process(clk, rst)

begin

if rst = '1' then

-- 初始化变量

elsif rising_edge(clk) then

if (send_request = '1' and tx_busy = '0') then

-- 数据封装和帧构造的逻辑...

-- 包括帧起始标志、地址字段、控制字段、数据字段、FCS计算和帧结束标志等

end if;

end if;

end process;

该代码示例展示了在数据发送请求被接收并且传输介质未忙的情况下,发送模块如何封装数据并构造HDLC帧。实现过程中需要考虑数据封装的顺序和校验码的正确计算。

3.3.2 流量控制和发送缓冲管理

为了防止发送缓冲区溢出,发送模块需要实现有效的流量控制机制。通常情况下,这涉及到与接收方进行交互,以确认接收方可以接受新的帧。

-- VHDL代码片段:HDLC发送流量控制

if (tx_request = '1' and tx_busy = '0') then

-- 有数据待发送且链路空闲

if (tx_buffer_not_full = '1') then

-- 缓冲区未满,可以发送数据

-- 将数据放入发送缓冲区并更新状态

else

-- 缓冲区已满,需要等待或实现流量控制逻辑

-- 如:暂停发送请求,或发送窗口控制信号

end if;

end if;

在该段代码中,我们根据发送请求和链路状态来决定是否进行数据发送。如果发送缓冲区未满,数据可以立即发送;如果缓冲区已满,则需要实现适当的流量控制措施,比如暂停发送或调整发送窗口。

3.4 本章小结

本章节深入探讨了在FPGA上实现HDLC协议接收和发送流程的具体方法。通过分析设计思路和模块化的设计,我们了解了如何将HDLC协议的不同部分转化为硬件逻辑。接收模块的设计和错误处理机制确保了数据传输的可靠性。而发送模块则负责数据封装和流量控制,保障了数据的有序发送。通过以上的分析和代码示例,我们可以看到FPGA硬件实现的灵活性和高效性,为复杂的通信协议提供了坚实的基础。

4. FIFO缓冲区设计与应用

4.1 FIFO缓冲区的工作原理

FIFO(First In First Out)缓冲区是一种常见的数据存储结构,它模拟了现实世界中的队列,按照“先到先服务”的原则处理数据。FIFO缓冲区常用于数据在不同处理速度的系统或模块之间的传输,它能够缓和速度差异,降低数据传输过程中发生阻塞的风险。

4.1.1 FIFO的基本概念和数据结构

FIFO缓冲区通常由一组固定大小的存储单元组成,这些存储单元在逻辑上串联起来形成队列。数据以写入(enqueue)的方式进入队列,以读出(dequeue)的方式离开队列。FIFO的两端分别为写入端(尾部)和读出端(头部)。当有新数据到来时,它会从尾部被添加到缓冲区;当有读取请求时,数据会从头部被移除。这种操作方式确保了最先写入的数据也是最先被读出的,这样就保证了数据的顺序性。

FIFO设计的一个重要考量是深度(depth),它决定了缓冲区可以存储多少数据。深度越深,缓冲能力越强,但相应的资源消耗也会增加。合理设计FIFO深度是确保系统稳定运行的关键。

4.1.2 FIFO的读写指针管理与溢出防范

为了有效管理FIFO缓冲区,需要维护两个指针:读指针(read pointer)和写指针(write pointer)。这两个指针分别记录了下一个读出位置和下一个写入位置。在数据的读写过程中,指针相应地前进,并且需要有机制来处理指针到达缓冲区末尾的情况。常见的处理方法是让指针循环回到缓冲区的开始,这种方法也被称为环形缓冲区(circular buffer)。

为了防止数据溢出,需要在设计FIFO缓冲区时考虑其溢出检测机制。通常,当缓冲区满时,会阻止进一步的数据写入,直到有足够空间释放。相应地,当缓冲区为空时,也应当防止数据的读取操作。在硬件实现中,可以通过设置标志位来表示FIFO的满和空状态,并在相应的控制逻辑中使用这些标志位。

4.1.3 FIFO设计的代码实现

-- VHDL code for a simple FIFO buffer

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.NUMERIC_STD.ALL;

entity fifo is

generic(

DATA_WIDTH : natural := 8; -- Number of bits in each FIFO entry

FIFO_DEPTH : natural := 16 -- Number of entries in the FIFO

);

port(

clk : in std_logic; -- Clock signal

reset : in std_logic; -- Reset signal

wr_en : in std_logic; -- Write enable

rd_en : in std_logic; -- Read enable

data_in : in std_logic_vector(DATA_WIDTH - 1 downto 0); -- Data input

data_out : out std_logic_vector(DATA_WIDTH - 1 downto 0); -- Data output

fifo_full : out std_logic; -- FIFO full flag

fifo_empty : out std_logic -- FIFO empty flag

);

end entity;

architecture Behavioral of fifo is

type fifo_array is array (0 to FIFO_DEPTH - 1) of std_logic_vector(DATA_WIDTH - 1 downto 0);

signal fifo_mem : fifo_array := (others => (others => '0'));

signal wr_ptr, rd_ptr : integer range 0 to FIFO_DEPTH - 1 := 0;

begin

process(clk, reset)

begin

if reset = '1' then

-- Reset all signals to initial state

-- ...

elsif rising_edge(clk) then

if wr_en = '1' then

-- Write data to FIFO memory

-- ...

end if;

if rd_en = '1' then

-- Read data from FIFO memory

-- ...

end if;

end if;

end process;

-- Additional logic to handle read and write pointers and FIFO status flags

-- ...

end architecture;

上述代码展示了FIFO的基本VHDL实现框架。代码中定义了数据宽度、FIFO深度、输入输出端口等。一个重要的逻辑部分留待实现,那就是如何处理读写指针以及如何设置满和空标志。在实际设计中,这些操作可能包括计数器的递增/递减逻辑和指针指向的更新。

FIFO缓冲区的设计与实现是确保通信系统稳定性的关键步骤之一,特别是在处理高速数据流时。在本章的后续部分,我们会探讨FIFO在HDLC协议中的应用以及如何优化FIFO设计以提高性能。

5. HDLC协议帧结构与同步机制

5.1 HDLC帧的构造与解析

HDLC协议的帧结构是数据传输的基础,它定义了数据包的格式和传递方式。了解和实现HDLC帧的构造与解析是通信协议开发中的关键步骤。

5.1.1 HDLC帧头和帧尾的结构意义

HDLC帧由若干字段组成,关键字段包括标志字段(Flag)、地址字段(Address)、控制字段(Control)、信息字段(Information)和帧校验序列(FCS)。

- 标志字段(Flag) :标志字段用于标识帧的开始和结束,它通常由0x7E的固定比特模式表示。这种模式在数据中是唯一的,因此它可以用作帧边界。

- 地址字段(Address) :地址字段包含被通信节点的地址信息,用于区分不同的通信终端。

- 控制字段(Control) :控制字段用于定义帧的类型(信息帧、监控帧、未编号帧)以及序列号等信息。

- 信息字段(Information) :信息字段携带实际要传输的数据,长度可变。

- 帧校验序列(FCS) :FCS字段用于确保数据的完整性,通常是一个CRC校验码。

sequenceDiagram

participant F as Flag Field

participant A as Address Field

participant C as Control Field

participant I as Information Field

participant FCS as FCS Field

F->>A: Start of Frame

A->>C: Address Information

C->>I: Control Information

I->>FCS: Data Payload

FCS->>F: End of Frame

5.1.2 数据封装和去封装的实现过程

在FPGA中实现数据的封装和去封装过程涉及对HDLC帧结构的理解和编程实践。

封装过程:

- 将数据包装进信息字段。

- 根据数据长度和协议要求计算FCS校验码。

- 将地址字段、控制字段、信息字段和FCS字段依次拼接,最后添加标志字段以构造完整的帧。

去封装过程:

- 检测到标志字段,确认帧的开始。

- 读取地址字段,确认帧的目的地。

- 解析控制字段,确定帧类型。

- 使用计算的FCS与帧尾的FCS进行比较,验证数据的完整性。

- 若数据完整,则提取信息字段的内容。

在实际的VHDL代码中,封包和解包操作可以被封装成函数或过程,以方便复用。例如:

-- HDLC Packet Encoder

procedure hdlc_encode(data_in : in std_logic_vector; encoded_packet : out std_logic_vector) is

begin

-- Encode data according to HDLC frame structure

-- Include flag fields, address field, control field, information field, and FCS field

end hdlc_encode;

-- HDLC Packet Decoder

function hdlc_decode(encoded_packet : in std_logic_vector) return std_logic_vector is

variable decoded_data : std_logic_vector;

begin

-- Decode packet, verifying FCS, extracting address/control/information fields

return decoded_data;

end hdlc_decode;

5.2 HDLC同步的实现机制

同步机制是HDLC协议能够正常通信的关键,主要依赖于标志字段和FCS序列。

5.2.1 同步字节的检测与匹配

HDLC通信双方通过检测标志字段来实现帧同步。标志字段的值为0x7E,它具有特殊的比特模式,由连续的'***'组成,易于硬件检测。

在接收端,FPGA会不断扫描接收到的比特流,寻找标志字段模式以确定帧的开始和结束。以下是一个简化的伪代码示例,展示了如何实现标志字段的检测:

-- Detection of Flag Sequence

signal flag_pattern : std_logic_vector(7 downto 0) := "***";

signal bit_stream : std_logic_vector(...);

signal received_flag : boolean := false;

-- Inside main receive process

if bit_stream = flag_pattern then

received_flag <= true;

end if;

5.2.2 链路层的自动重同步策略

在实际通信中,可能会遇到比特错误导致同步丢失。HDLC协议具有自动重同步的机制,即接收方可以通过连续读取标志字段来重新获得帧边界,即使这些字段是由于比特错误而插入的。

自动重同步不仅保障了通信的可靠性,也增强了系统对噪声和干扰的鲁棒性。在设计时,必须确保接收逻辑能够在连续检测到多个标志字段后快速恢复同步,防止错误传播。

5.3 HDLC帧同步的故障分析与排除

HDLC协议的帧同步在实施过程中可能会遇到各种问题,如同步丢失、多帧错误等。故障分析与排除是确保通信链路稳定运行的重要环节。

5.3.1 同步故障的常见原因与诊断

同步故障的常见原因包括物理层噪声、信号衰减、时钟偏差和硬件故障等。为了诊断同步故障,需要在FPGA中设置同步检测日志,记录同步过程中的异常事件。

诊断步骤:

- 记录同步异常事件 :记录何时检测到异常的标志字段,以及连续出现的次数。

- 分析异常模式 :分析连续标志字段出现的模式和错误位置,以便确定故障原因。

- 信号质量检查 :使用示波器或逻辑分析仪检查信号的完整性,寻找潜在的信号干扰源。

5.3.2 同步恢复的策略与实施

一旦检测到同步故障,必须采取措施恢复。HDLC协议支持通过连续的标志字段自动恢复同步,但在某些情况下可能需要手动干预。

恢复策略:

- 软件重置 :在检测到同步故障时,重置接收逻辑并重新启动帧同步过程。

- 硬件复位 :在硬件层面上,如果软件重置无法解决问题,可能需要复位通信硬件。

在实施同步恢复时,可以编写特定的VHDL代码段来实现这些策略,例如:

-- Synchronization Recovery Process

if sync_loss_detected then

software_reset := true;

if software_reset then

-- Reset the synchronization state machine

-- and try to re-establish the frame boundary

end if;

if hardware_reset then

-- Perform a hardware reset of the communication port

end if;

end if;

在上述章节中,我们逐步深入地探讨了HDLC协议帧结构和同步机制的各个方面,从HDLC帧的构造与解析,到同步的实现机制,以及如何进行故障分析与排除。通过本章内容的学习,您不仅能够理解HDLC协议的理论和实践,还能够掌握在FPGA环境下实现这些功能的具体方法。这对于任何需要实现高效、可靠的数据通信系统的开发者来说,都是一个宝贵的知识点。

6. CRC32、CRC16和CCITT校验方法

6.1 CRC校验原理与计算方法

6.1.1 CRC校验的理论基础

循环冗余校验(CRC,Cyclic Redundancy Check)是一种根据数据内容计算出固定位数校验码的错误检测技术。它是通过将数据视为一个长的多项式,并将它除以另一个固定多项式(生成多项式)来获得余数,该余数即为校验码。

CRC的理论基础基于二进制算术和多项式除法。在二进制中,加法是通过异或(XOR)操作来实现的,而乘法则可以通过逻辑与(AND)操作后左移操作来实现。CRC计算实质上是模拟二进制除法,最终的余数(校验码)被附加到数据后面发送出去。接收方通过相同的生成多项式去除接收到的数据(包括校验码),如果余数为零,则认为数据在传输过程中没有发生错误。

6.1.2 CRC32、CRC16的计算过程与实现

CRC32和CRC16的计算方法类似,只是所使用的生成多项式不同。以CRC32为例,常用的生成多项式为 0x04C11DB7 。计算过程中通常采用位反转(bitwise reversal)和模2除法:

- 将数据位进行位反转。

- 将位反转后的数据左移(位数等同于生成多项式中1的个数减1)。

- 使用模2除法将左移后的数据与生成多项式的二进制表示进行除法运算,得到余数。

- 将余数进行位反转,得到的即为CRC32校验码。

下面是一个简单的CRC32的计算示例代码:

def crc32(data):

crc = 0xFFFFFFFF

crc ^= int.from_bytes(data, byteorder='big')

for _ in range(len(data) * 8):

if crc & 1:

crc = (crc >> 1) ^ 0xEDB88320

else:

crc >>= 1

return ~crc & 0xFFFFFFFF

此代码中,首先初始化CRC寄存器为0xFFFFFFFF,然后对数据进行字节与字节的CRC计算,并在最后取反,得到最终的CRC32校验码。

6.2 CCITT校验的具体应用

6.2.1 CCITT校验码的生成与检测

CCITT(Consultative Committee on International Telegraph and Telephone)校验码是另一种常见的校验方法,也称为CRC16或Xmodem CRC。最常用的生成多项式为 0x1021 。

生成CCITT校验码的过程与CRC32类似,不同之处在于使用的生成多项式和初始值以及最终结果的处理。通常,CCITT校验码的计算过程中初始寄存器值为 0xFFFF ,并在最后结果取反但不加1。

示例代码如下:

def ccitt(data):

crc = 0xFFFF

for byte in data:

crc ^= byte

for _ in range(8):

if crc & 1:

crc = (crc >> 1) ^ 0x8408

else:

crc >>= 1

return crc & 0xFFFF

在上述代码中,采用0x8408作为生成多项式,初始值设为 0xFFFF ,对每个字节进行处理后得到的16位值即为CCITT校验码。

6.2.2 CCITT校验在HDLC协议中的角色

CCITT校验方法被广泛应用于HDLC协议中,用于确保数据传输的完整性。在HDLC协议中,每一帧数据的传输都包含了一个16位的CRC校验码,这个校验码正是通过CCITT方法计算得出。接收方在接收到数据后,对数据进行同样的CRC计算,通过比较计算结果与帧内包含的校验码,可以检测出数据在传输过程中是否出现了错误。

6.3 校验方法的性能比较与选择

6.3.1 不同校验方法的优缺点分析

CRC校验方法提供了较高的错误检测能力,尤其是CRC32,它能够检测出较多的错误模式,适用于对错误检测要求较高的场景。然而,它计算起来相对复杂,占用资源较多。

CCITT校验码相对简单,计算效率较高,适用于资源有限的系统,比如小型嵌入式设备。尽管它提供的错误检测能力比CRC32弱,但在许多实际应用中已经足够。

6.3.2 校验方法在不同场景下的选择建议

选择校验方法时需要考虑特定应用的需求:

- 对于要求高错误检测能力的应用,推荐使用CRC32。

- 对于资源受限的环境,如便携设备或实时系统,建议使用CRC16或CCITT。

- 在选择校验方法时,还应考虑计算速度、硬件资源利用率以及与其他系统组件的兼容性。

最后,实际应用中的选择可能还需要考虑诸如实现复杂度、功耗、传输速率等因素,以确保系统整体性能与稳定性。

flowchart LR

A[应用需求分析] --> B{资源限制}

B -->|限制较高| C[CCITT校验]

B -->|限制一般| D[CRC16校验]

B -->|无限制| E[CRC32校验]

C --> F[嵌入式系统]

D --> G[中等复杂度应用]

E --> H[高可靠性应用]

7. 通信系统的设计与代码实现

7.1 通信系统设计的整体架构

7.1.1 系统设计的目标与要求

在设计通信系统时,首先要明确系统的总体目标和具体要求。通常,这些目标和要求包括支持多通道的数据传输、保证数据的高完整性与可靠性、提供低延迟的响应时间,以及确保系统的可扩展性和灵活性。设计时还应考虑系统的安全性,以防止数据泄露和其他潜在的安全威胁。此外,设计还应该考虑硬件资源的限制,如FPGA内部资源(如逻辑单元、存储器等)的使用,以及系统功耗和成本。

7.1.2 系统架构的层次划分与模块化设计

为了更好地管理通信系统的复杂性,可以采用分层的架构设计。每一层负责一组特定的功能,例如物理层、数据链路层、网络层、传输层和应用层。在数据链路层,专门设计了HDLC协议处理模块,而在物理层,可能涉及到串行通信模块的实现。模块化设计允许不同的开发团队独立工作,简化了代码的维护和升级工作。

7.2 FPGA代码的编写与调试

7.2.1 HDLC协议代码的实现要点

编写HDLC协议代码时,需要遵循协议规范,实现必要的帧结构和同步机制。VHDL代码的编写要点包括使用状态机来处理帧的接收和发送状态,以及正确处理控制字段来实现错误检测和流量控制。同时,要在FPGA的有限资源内实现高效的CRC校验计算,保证数据的完整性和正确性。

7.2.2 代码的测试流程与调试技巧

在代码编写完成之后,需要进行严格的测试流程以确保实现的功能符合预期。测试流程包括单元测试、集成测试和系统测试。首先,单元测试应该针对每个独立模块进行,确保它们按照协议规范正确工作。集成测试则需要将各个模块组合在一起,并确保它们协同工作无误。系统测试是在真实的硬件上进行的,包括稳定性测试和性能测试。调试技巧包括在代码中插入日志语句来追踪问题,以及使用逻辑分析仪监控信号状态和时序关系。

7.3 系统的集成测试与性能评估

7.3.1 系统集成的步骤与方法

系统集成是一个将各个模块组装成完整系统的过程。在FPGA上,系统集成的步骤通常包括将各个VHDL模块编写成顶层实体,并连接到适当的I/O端口。集成方法包括自底向上和自顶向下两种。自底向上是先集成底层模块,然后逐层向上集成;而自顶向下则是先定义系统顶层,然后分块实现并集成。

7.3.2 系统性能的评估指标与优化措施

系统性能评估通常关注数据吞吐率、延迟、丢包率和资源利用率等指标。优化措施包括硬件资源的重新分配、算法优化、缓存管理优化等。在代码层面,可以通过优化状态机设计、减少不必要的状态转换、使用流水线技术和并行处理等方法来提高性能。性能评估与优化是一个持续的过程,随着系统在实际运行中的表现,可能需要不断地调整和改进。

简介:本压缩包资源为初学者提供了FPGA实现HDLC协议的入门级教程,包括使用VHDL语言编写的代码实例。HDLC是一种同步通信数据链路层协议,该教程详细讲解了如何在FPGA硬件上实现HDLC协议的相关模块,包括接收、发送和错误校验过程。源码文件包括接收和发送端的FIFO缓冲区、不同校验方式的实现代码,以及关于HDLC协议的PowerPoint演示文稿。通过学习这些资料,可以加深对HDLC协议和FPGA编程的理解,为在通信等领域的应用打下基础。

744

744

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?