题目:

描述:

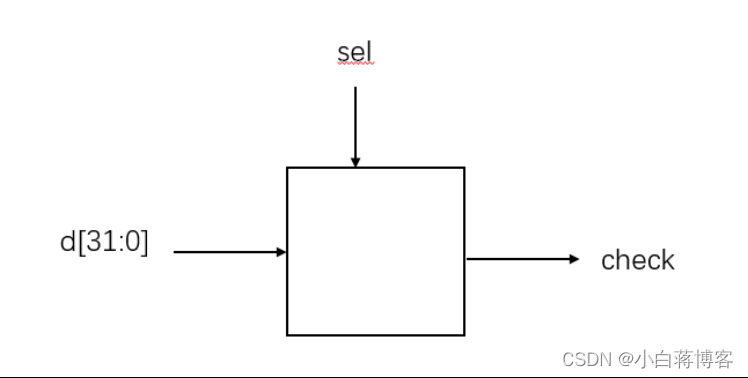

现在需要对输入的32位数据进行奇偶校验,根据sel输出校验结果(1输出奇校验,0输出偶校验)

信号示意图:

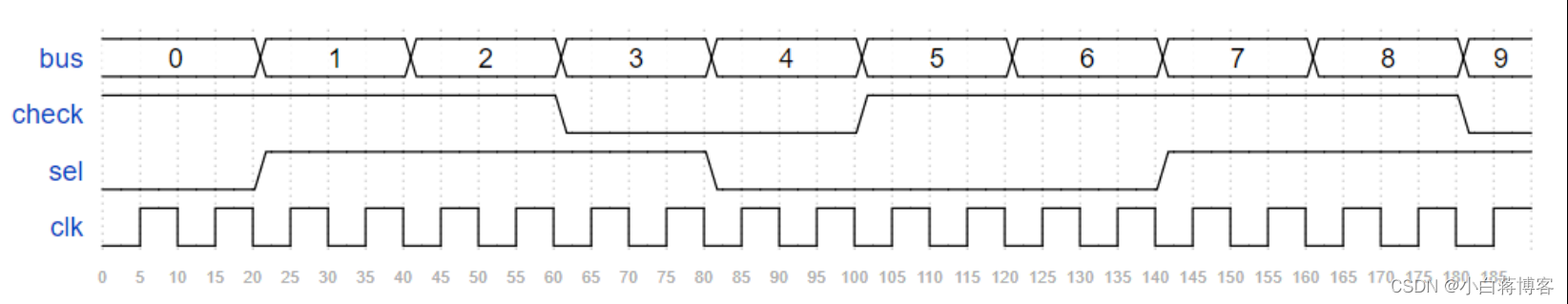

波形示意图:

输入描述:

输入信号 bus sel

类型 wire

输出描述:

输出信号 check

类型 wire

解答:

1、简单理解奇偶校验

奇校验:原始码流+校验位 总共有奇数个1

偶校验:原始码流+校验位 总共有偶数个1

2、计算奇偶校验的方法 按位求异或得到奇校验结果,对其求反得到偶校验结果

3、连续进行异或 odd = ^bus 对bus进行异或位操作

设计代码实现:

将电路转换成Verilog代码描述如下

wire odd;

assign odd = ^bus;

assign check = sel?odd:~odd;

在命令行输入g odd.v,然后复制下面代码:

`timescale 1ns/1ns

module odd_sel(

input [31:0] bus,

input sel,

output check

);

wire odd;

assign odd = ^bus;

assign check = sel?odd:~odd;

endmodule

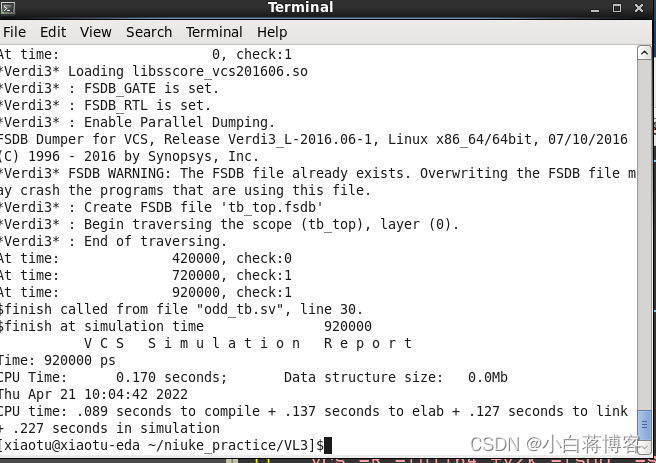

验证平台实现:

在命令行输入g odd_tb.v,然后复制下面代码:

`timescale 1ns/1ps

module tb_top();

logic [31:0] BUS;

logic SEL;

logic CHECK;

logic clk;

initial begin

#0;

clk = 1;

#20;

forever #50 clk = ~clk;

end

initial begin

BUS = 1;

SEL = 1;

$display("At time:%t, check:%h", $time, CHECK);

repeat(5) @(posedge clk);

SEL = 0;

$display("At time:%t, check:%h", $time, CHECK);

repeat(3) @(posedge clk);

BUS = 'h3;

$display("At time:%t, check:%h", $time, CHECK);

repeat(2) @(posedge clk);

$display("At time:%t, check:%h", $time, CHECK);

$finish;

end

odd_sel u0_odd (

.bus(BUS),

.sel(SEL),

.check(CHECK)

);

initial begin

$fsdbDumpfile("tb_top.fsdb");

$fsdbDumpvars(0, tb_top);

end

endmodule

makefile脚本实现:

在命令行输入g Makefile,然后复制下面代码:

#-----------------------------------------------------------

#// FileName: makefile

#// Creator: xiaobaijiang

#// time: 2022-04-21

#// wchat: jianfuk

#//-----------------------------------------------------------

run:

vcs -R -full64 +v2k -fsdb -sverilog odd.v odd_tb.sv -l run.log

verdi:

verdi -sv odd.v odd_tb.sv -ssf tb_top.fsdb &

clean:

@rm -rf verdiLog *.log *.fsdb csrc ucli.key simv* *.conf *.rc

仿真看波形:

命令行输入 make run

命令行输入make verdi,查看波形

更多芯片验证自学教程,请访问->传送门

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?