《Rockchip RK3568 TRM Part2 V1.1-20210301.pdf》 VOP、IEP 章节阅读笔记

目的:了解 FB to VideoSignal 的过程,以及如何在 rk3568 上进行配置实现。

VOP2 是framebuffer(内存中)到显示设备之间的接口。就是这东西将fb转为hdmi串行视频信号的。

IEP 是Image Enhancement Processor,功能为 YUV420/YUV422 及其他格式互转?

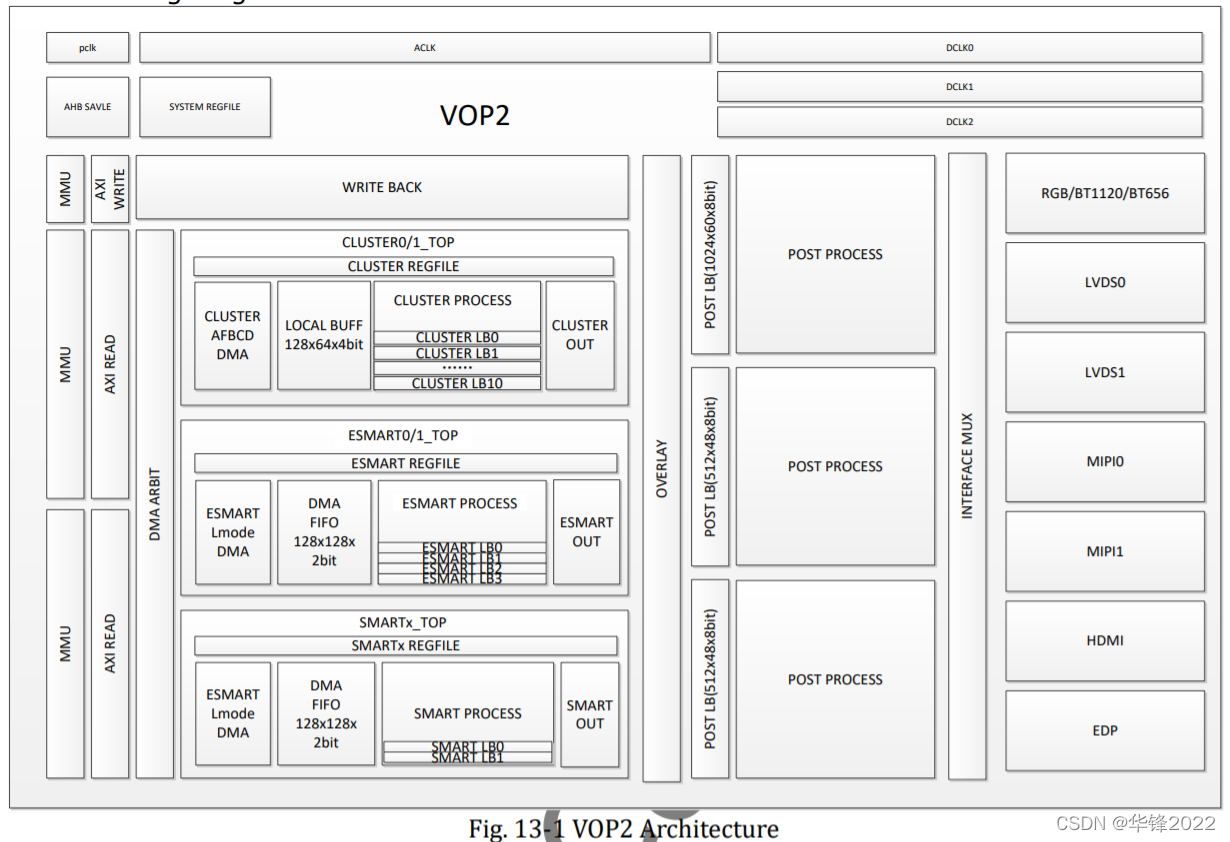

vop2 内:

既有 AHB slave,让CPU对vop2进行配置的通道

也有 AXI Master,像素数据的传输通道

支持的输出接口:HDMI、LVDS、EDP、MIPI、BT656、RGB/BT1120

BUS

One 32bit AHB Slave to configure registers

Two 128bit AXI read bus

One 128bit AXI write bus

3个Video ports

vp0 vp1 vp2(rk3399中好像是两个video ports)

其中 vp0 支持到 4k 显示,vp1/vp2 支持到2k显示

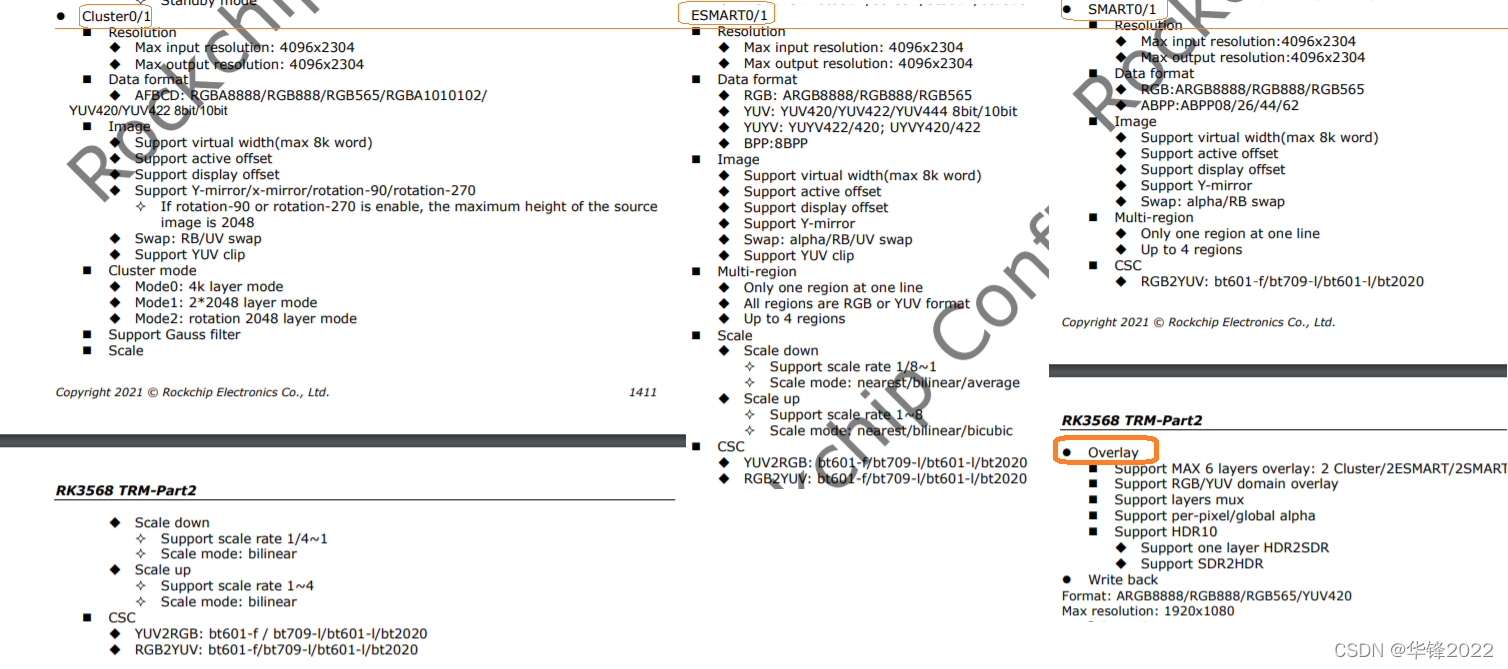

Cluster0/1

不懂 Data format: AFBCD: RGBA8888/RGB888/RGB565/RGBA1010102/

YUV420/YUV422 8bit/10bit

这个不是led面板像素排布情况吗?为何 vop2 中也有这东西?

ESMART0/1

不懂

SMART0/1

不懂

Overlay

模模糊糊的了解一点

Support MAX 6 layers overlay: 2 Cluster/2ESMART/2SMART

Support RGB/YUV domain overlay

Support layers mux

Support per-pixel/global alpha

Support HDR10

Support one layer HDR2SDR

Support SDR2HDR

Write back

不懂

Format: ARGB8888/RGB888/RGB565/YUV420

Max resolution: 1920x1080 (1080p)

有3类中断

1). Vop_intr

System0 interrupt

axi bus 相关的中断

Video port0/1/2 interrupt

Frame start interrupt 等等

AFBCD interrupt

Cluster、win 相关的中断

2). Vop_intr_ddr

dma 相关的中断

3). Vop_intr_lb

不懂

rk3568 中的 VOP2 的架构图:

像素格式:

从架构图看, cluster、ESmart、smart 是平级的关系,功能是类同的吗?

都是 overlay 子模块的前级,主要差别在所支持的 data format 不同

(data format 是不是像素格式 pixel format?)

VOP2的虚拟显示模式(13.3.2 Virtual display)

在 virtual display 模式下, fb 中的图像不会全部显示,而只显示其中的活动区域(active area)

此时整个fb所描述的图像称为 virtual image

active area 所描述的图像秒为 active image

VIR_STRIDE 系列寄存器表示 virtual width (32bits)

如 RGB/BPP 像素格式下的 yrgb_vir_stride

如 YCbCr 像素格式下的 yrgb_vir_stride 和 cbcr_vir_stride

对于 RGB-8bit and YUV-8bit 两种像素枨,stride 必须是4字节对齐的(能被4整除)

如果不能整除,应该补够字节,使得总字节数能被整除。

吐:明明是在讲 virtual image width,为何要给寄存器起个带 stride 的名字?

VOP2的AFBCD (13.3.3 AFBCD) AFBC=Arm Framebuffer Compression

这种压缩格式设计用于纹理和帧缓冲区。它已经过优化,可以减少外部带宽,并且可以随机访问,并且可以以线速度对纹理缓存进行解码。单个16x16块可以随机访问,而这些块反过来索引单个4x4块。这是通过一种结构来实现的,在这种结构中,每个16x16块的头块都存储在一个可预测的内存地址中,称为头缓冲区。

也是属于读不懂系列。综合搜索得知这是一种节省 fb 占用的内存空间、节省显示带宽的技术。主要基于类似固定面积的瓦片(16*16、4*4 pixel)的技术。

13.3.7 BCSH

Brightness, Contrast, Saturation, and Hue controls

亮度、对比度、饱和度和色调控制

13.3.8 Gamma 伽马校正

RGB在传输前通过逆变换进行了伽马校正.

13.3.9 3D_LUT( 3d lookup table)

不懂,好像是一种调色表、变色表,反正就是颜色映射关系表。什么是 3D LUT

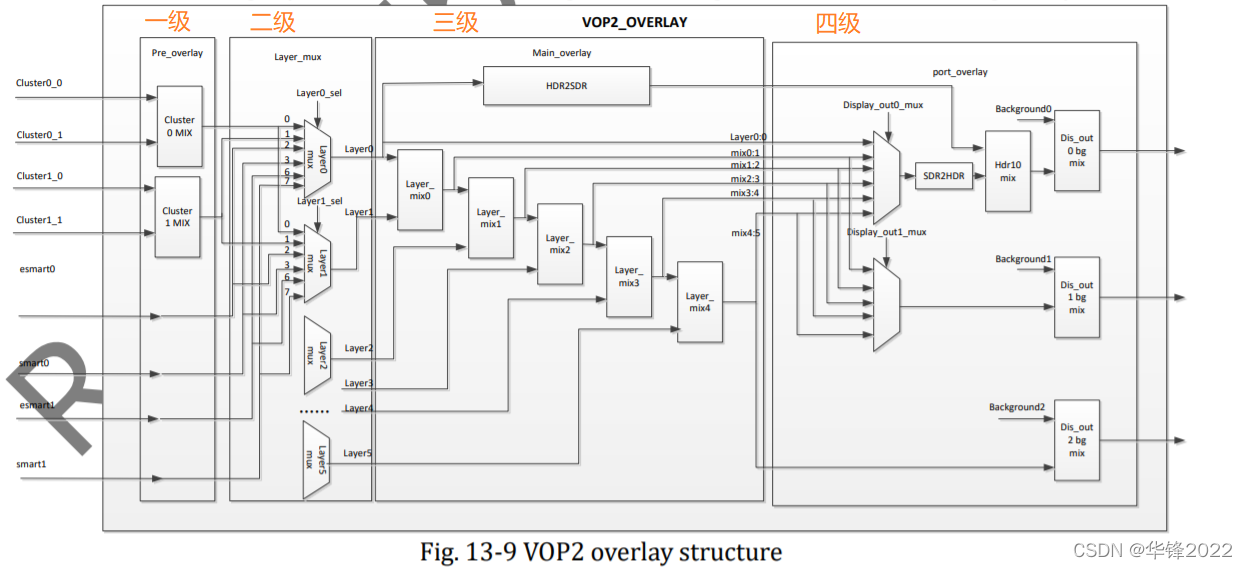

13.3.11 Overlay (关键内容)

混合视频信号可能就像在两个视频源之间切换一样简单。对于大多数其他应用程序,应使用称为alpha混合的技术将计算机生成的文本和图形叠加到视频信号上。该图显示了在VOP中混合8层。

第一级 pre_overlay, 同 cluster 的混合

第二级 layer_mux,同 window number 混合,最大支持6个layer,所以里面有6个mix

第三级 main_overlay,所有图层逐层混合,内有5个mix (0..5) ,即可混合前级的6个layer

第四级 post_overlay,混合不同的背景色后,为不同的应用产生不同的输出

13.3.11.1 Alpha mixing

alpha 混合,至少有一个 src 层和一个 dst 层。这两层在混合时,都要设置各自的透明度。

13.3.12 HDR10

摄像头画面高质量回显相关标准?

13.3.13 Mirror display

镜像显示,左右镜像、上下镜像,不管

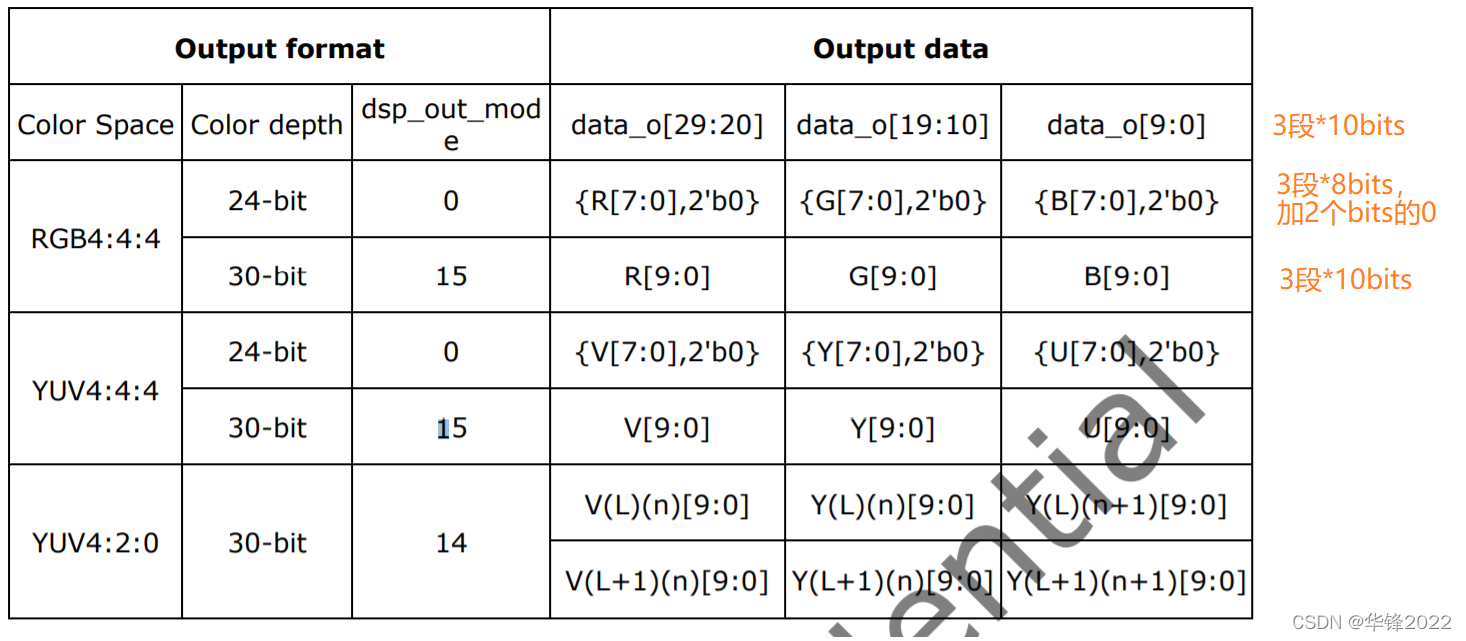

13.3.14 Display outputs

VOP2 能输出30-bit颜色模式的4k画面,输出模式可以通过 dsp_out_mode 寄存器进行设置。具体值参考这个表:

关键寄存器:

VOP2_SYS_AUTO_GATING_CTRL_IMD:看名称了

VOP2_SYS_DSP_INFACE_EN:[11:10] 设置 vp0~vp3 中的哪一个输出到 hdmi 接口,[1] hdmi_out_en ,默认是0, 得设置为1,才会给 vop2 内部的hdmi interface!

VOP2_SYS_STATUS0:vp0 的状态寄存器

VOP2_SYS_LINE_FLAG0:

VOP2_PORT0_INTR_EN:中断启用,相关的还有 VOP2_PORT0_INTR_CLR, VOP2_PORT0_INTR_STATUS

VOP2_OVERLAY_CTRL:vop2 overlay 主控寄存器

VOP2_LAYER_SEL:overlay 支持 6个layer,这个寄存器用来设置哪一个模块当做哪一个layer

VOP2_POST0_DSP_CTRL:控制vp0的display mode

VOP2_POST0_DSP_BG: vp0 的背景色

pdf 文档中 VOP2 相关的寄存器总共有几百页, 列个目录方便以后自己查算了,哈哈,除了厂家写驱动的外,也就是我这种闲渣才会查这几百页的跟字典一样的内容。

13.4 Register Description VOP2_BASE = 0xFE040000,共64kb

13.4.1 System Register description 0x0000

13.4.2 Overlay register description 0x0600

13.4.3 Post-process0 register description 0x0c00

13.4.4 Post-process1 register description 0x0d00

13.4.5 Post-process2 register description 0x0e00

13.4.6 Cluster register description

The base address of cluster0 registers is 0x1000.

The base address of cluster1 registers is 0x1200.

13.4.7 Esmart register description

The base address of esmart0 registers is 0x1800.

The base address of esmart1 registers is 0x1a00.

13.4.8 Smart register description

The base address of smart0 registers is 0x1c00.

The base address of smart1 registers is 0x1e00.

13.4.9 HDR10 register description 0x2000

13.4.10 MMU register description

The base address of MMU0 registers is 0x3e00.

The base address of MMU1 registers is 0x3f00.

13.4.11 LUT address summary

The base address of GAMMA LUT is 0x4000, it’s size is 0x1000. The base address of BPP LUT is 0x5000, it’s size is 0x0400.

13.5.7 The delay number of overlay application note

The delay number used in different application scenarios is shown as below

13.5.8 HDR10 application note

If HDR10 is enable, overlay_mode must be RGB.

不晓得不启用CPU 的 DMA MMU这两个功能, VOP2能不能产生视频信号。

本文详细介绍了Rockchip RK3568芯片中VOP2模块的功能与配置方法,包括帧缓冲到视频信号转换过程、图像增强处理、数据格式支持等内容,并探讨了虚拟显示模式及多种显示输出特性。

本文详细介绍了Rockchip RK3568芯片中VOP2模块的功能与配置方法,包括帧缓冲到视频信号转换过程、图像增强处理、数据格式支持等内容,并探讨了虚拟显示模式及多种显示输出特性。

5854

5854

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?