为什么时钟树上要用clock inverter(min pulse width check)

文章右侧广告为官方硬广告,与吾爱IC社区无关,用户勿点。点击进去后出现任何损失与社区无关。

Min pulse width 定义

最小脉冲宽度检查可确保时钟信号的宽度足够宽,以便采集到正确的数据,保证设计功能。即为了获得稳定的输出,需要确保时钟信号宽度至少达到某个 “最小宽度”。比如 lib 中就对寄存器 Flipflop 的 CLK pin 有 min pulse width 的 check。

- High pulse width

If you need a formal definition of the term, it is the interval between the rising edge of the signal crossing 50% of VDD and the falling edge of the signal crossing 50% of VDD.

- Low pulse width

If talking in terms of low signals, it is the the interval between falling edge of the signal crossing 50% of VDD and the rising edge of signal crossing 50% of VDD.

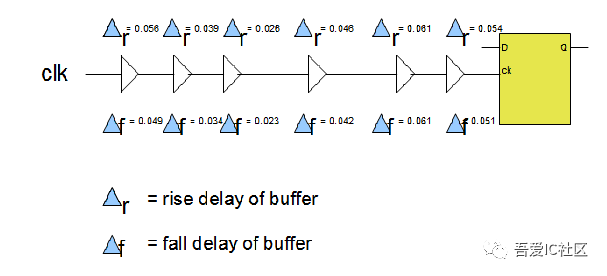

以下图为例,一个时钟信号 CLK,经过六级普通 buffer(各自的 rise time 和 fall time 是不相同的) 到达一个寄存器的 CK 端。我们来计算下 high pulse width,low pulse width 以及判断是否存在 min pulse width 违例(uncertainty:80ps Reg ck pin requirement min pulse width:0.420ns)。

High pulse width = 0.5 + (0.049-0.056) + (0.034 -0.039) + (0.023-0.026) + (0.042-0.046) + (0.061 – 0.061) + (0.051-0.054) = 0.478ns

Low Pulse width = 0.5 + (0.056 – 0.049) + (0.038 – 0.034) + (0.026 – 0.023) + (0.046 – 0.042) + (0.061 – 0.061) + (0.054 – 0.051) = 0.522ns

high pulse width = 0.478-0.080 = 0.398ns (小于 0.420ns)

因此,存在 min pulse width violation。

Min pulse width 检查方式

- Liberty 文件

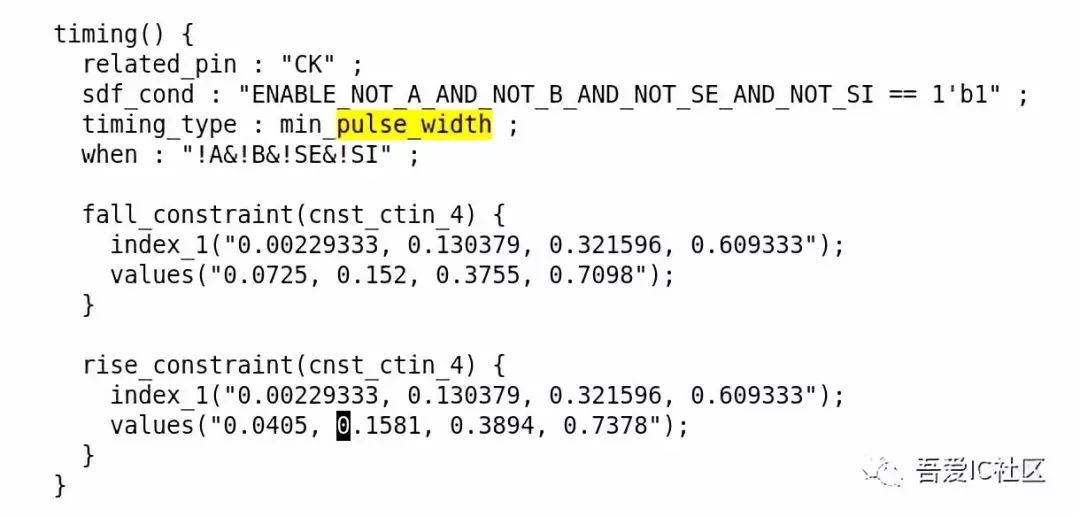

Liberty 文件中对寄存器的 CLK pin 和 reset pin 均有一个默认的 min pulse width check 值。在 STA 分析时工具会自动载入进行 check。如图 1 所示,index_1 为 input transition。

图 1 lib 中 min_pulse_width 属性定义

- SDC 约束

除了采用 lib 文件中默认的 min pulse width 值 check 外,我们还可以通过如下 SDC 命令来设置特殊的约束条件。

set_min_pulse_width -high 2 [get_clocks clk]

set_min_pulse_width -low 1 [get_clocks clk]

理想 clock buffer/inverter 的特性

-

Equal rise and fall times

-

Less delay variations with PVT and OCV

-

Clock buffer 能够驱动较长的 net 以及更多的 fanout

普通 buffer 如何导致 pulse width violation?

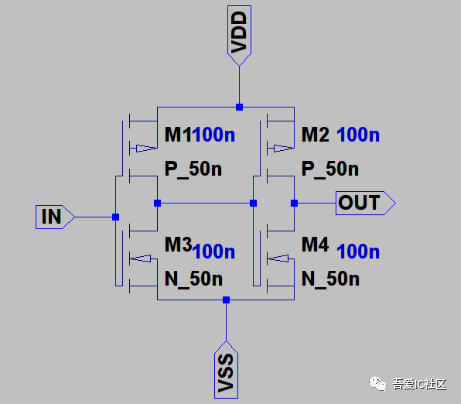

图 2 显示了 Wp = 100nm&Wn = 100nm 的 Buffer 电路的示意图。β比率(PMOS 的宽度与 NMOS 的宽度的比率)由于 NMOS 的迁移率高于 PMOS,因此上升时间大于下降时间。这个结论是根据电流公式得出的,不懂的请移步模拟电路查阅。

图 2 Unbalanced Buffer 电路原理图

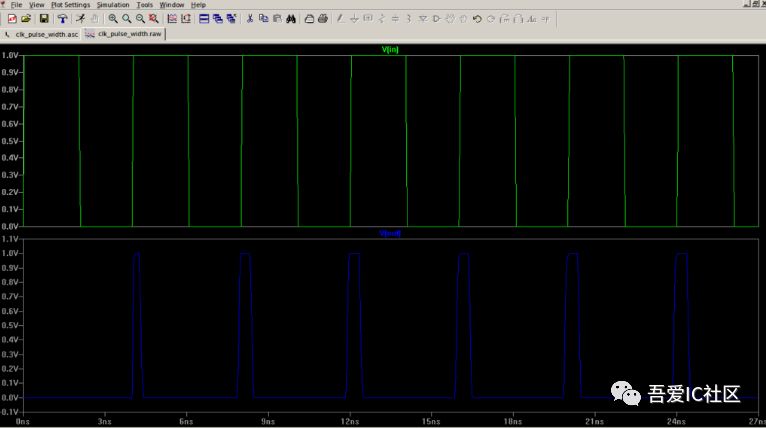

这里的每个 buffer 都需要更多的时间来充电 (相比放电过程)。输入为占空比为 50%的周期为 4ns 的脉冲信号。当时钟信号通过 buffer chain 传播时,脉冲宽度如下图 4 所示减少相当多。最后一个 buffer 的输出具有相同的周期,但占空比发生了变化。在最坏的情况下,这种情况可能会小于设计所需的脉冲宽度(最小脉冲宽度)。

图 3 Unbalanced Buffer Chain

图 4 pulse width reduction

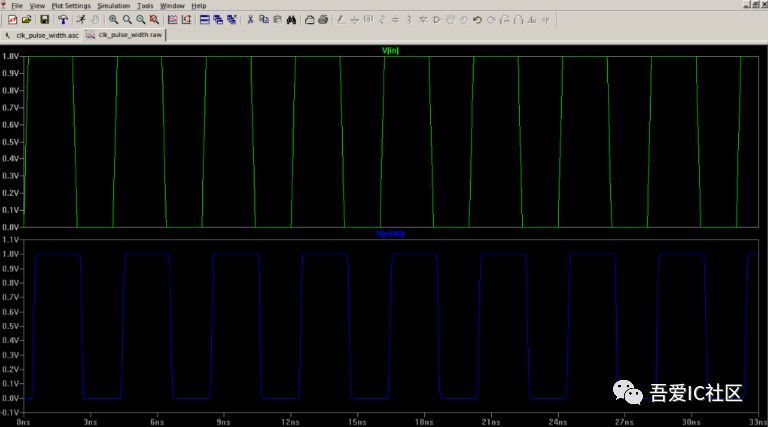

Balanced buffers have equal rise and fall time

为了使得 buffer 的上升和下降时间一致,PMOS 的宽度应该约为 NMOS 的两倍(具体倍数关系取决于工艺)。Balance buffer 电路结构图如图 5 所示。图 6 为一堆 balanced buffer 级联的 buffer chain 的输出波形。从输出波形看到,当我们在 clock path 上使用这种 balanced buffer,输出时钟信号周期未发生变化且占空比仍然为 1:1,即不会出现 pulse width violation。

图 5 balance buffer 电路结构图

图 6 Balanced Buffer Chain 输出波形

unbalanced inverter 有没有 min pulse width 问题?

如果在时钟路径中使用偶数个反相器,一对反相器上升和下降时间会相互补偿,所以脉冲宽度并不会改变。所以反相器输出不会导致脉冲宽度违规。

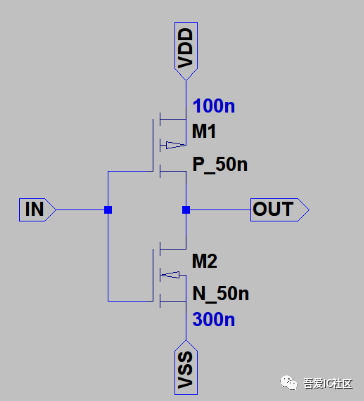

图 7 所示为一个反相器的电路结构图。其中 Wp = 100nm,Wn = 300nm。根据 P 管和 N 管的尺寸,我们得知上升时间比下降时间小得多。

图 7 Unbalanced 反相器原理图

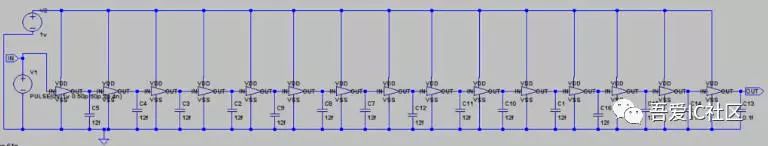

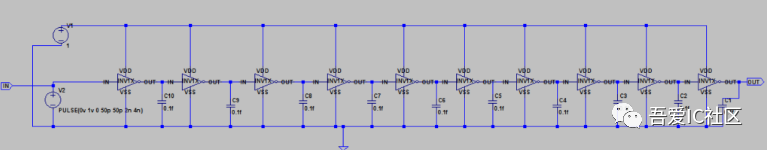

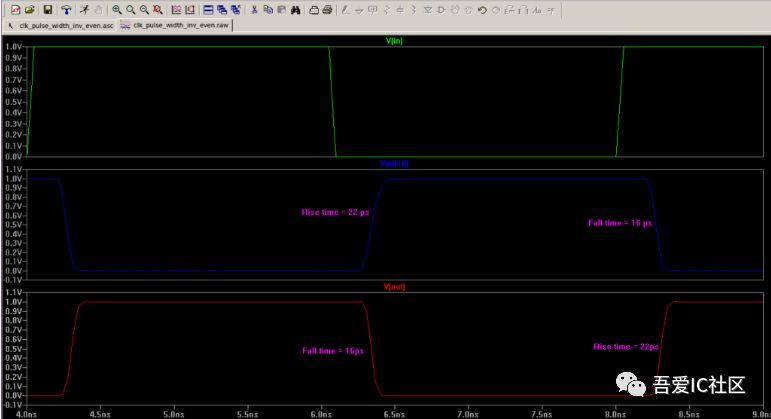

图 8 所示为一个十级反相器级联的电路图。图 9 为第九级和第十级反相器输出波形图。从图中可以得知,unbalance inverter 同样也不会导致 min pulse width 问题。

图 8 unbalanced inverter chain

图 9 第九级,第十级反相器输出波形图

所以,在做时钟树综合时,我们往往选用 clock inverter 来长 clock tree。

时钟树综合(clock tree synthesis)基础篇

思考题:

如果用 clock buffer 来长 clock tree 呢?各自的优缺点分别是什么?clock buffer 和普通 buffer 的优缺点各是什么?(答案均在本文中)

小编知识星球简介:

在这里,目前已经规划并正着手做的事情:

-

ICC/ICC2 lab 的编写

-

基于 ARM CPU 的后端实现流程

-

利用 ICC 中 CCD(Concurrent Clock Data)实现高性能模块的设计实现

-

其他内容待定

在这里,各位可以提问(支持匿名提问,提问从此不再害羞),小编会在 24 小时内给予解答(也可以发表你对某个知识点的看法,项目中遇到的难点,困惑或者职业发展规划等)。

反正它是一个缩减版的论坛,增强了大家的互动性。更为重要的是,微信有知识星球的小程序入口。星球二维码如下,可以扫描或者长按识别二维码进入。目前已经有十二位星球成员,感谢这十二位童鞋的支持!欢迎各位铁杆粉丝加入!

相关文章推荐(不看保证后悔)

PBA(Path Base Analysis)想说爱你不容易(静态时序分析基础篇)

【惊呆了!】你居然还在用 flatten 方式进行 timing signoff

合理的时钟结构能够加速 Timing 收敛(时钟树综合中级篇)

【机密】从此没有难做的 floorplan(数字后端设计实现 floorplan 篇)

听说 Latch 可以高效修 hold 违例(Timing borrowing 及其应用)

秒杀数字后端实现中 clock gating 使能端 setup violation 问题

教你轻松调 DCT 和 ICC 之间 Timing 与 Congestion 的一致性

Scan chain reordering 怎么用你知道吗?

数字后端实现时 congestion 比较严重,你 hold 得住吗?

Final netlist release 前,你应该做好哪些工作?

深入浅出讲透 set_multicycle_path,从此彻底掌握它

数字后端实现时 congestion 比较严重,你 hold 得住吗?

时钟树综合(clock tree synthesis)基础篇

好了,今天的码字就到这里了,原创不容易,喜欢的可以帮忙转发和赞赏,你的转发和赞赏是我不断更新文章的动力。小编在此先谢过!与此同时,吾爱 IC 社区(52-ic.com)也正式上线了。吾爱 IC 社区(52-ic.com)是一个专业交流和分享数字 IC 设计与实现技术与经验的 IC 社区。如果大家在学习和工作中有碰到技术问题,欢迎在微信公众号给小编留言或者添加以下几种联系方式进行提问交流。

打赏的朋友,请长按下方二维码,识别小程序进行打赏,欢迎砸钱过来!小编晚饭能不能加个鸡腿,全靠它了,呵呵!

作者微信:

4640

4640

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?