一、概述

作用:串口数据收发IP核。

特点:

- AXI4-Lite接口

- 16450与16550的硬件和软件寄存器兼容

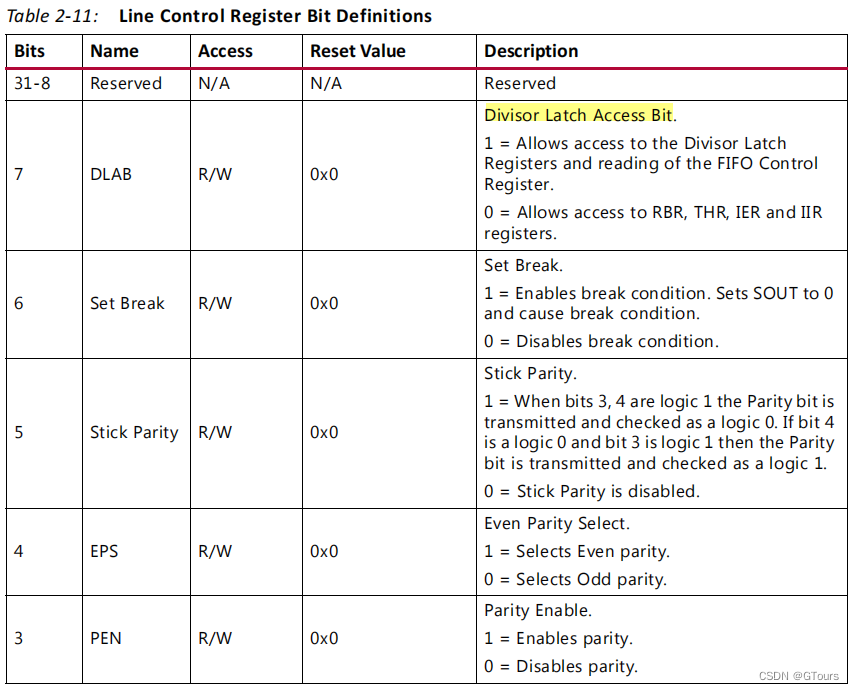

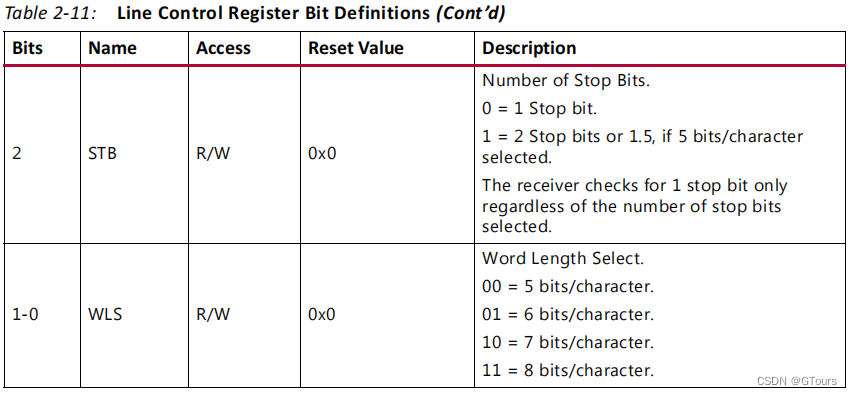

- 默认波特率9600、数据位8、停止位1、无校验位

- 5、6、7、8数据位

- 奇、偶、无校验

- 1、1.5、2停止位(1.5表示电平持续1.5个波特率时钟周期)

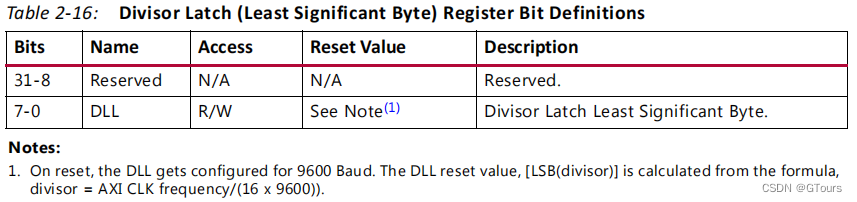

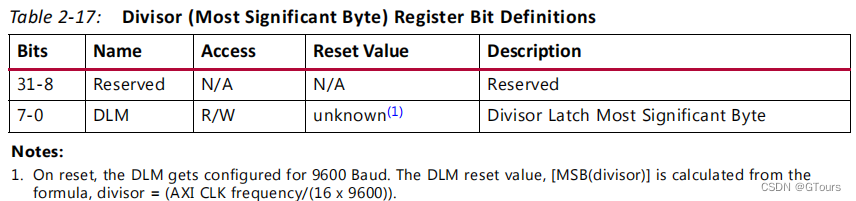

- 波特率发生器【divisor = AXI CLK frequency/(16 x 波特率))】

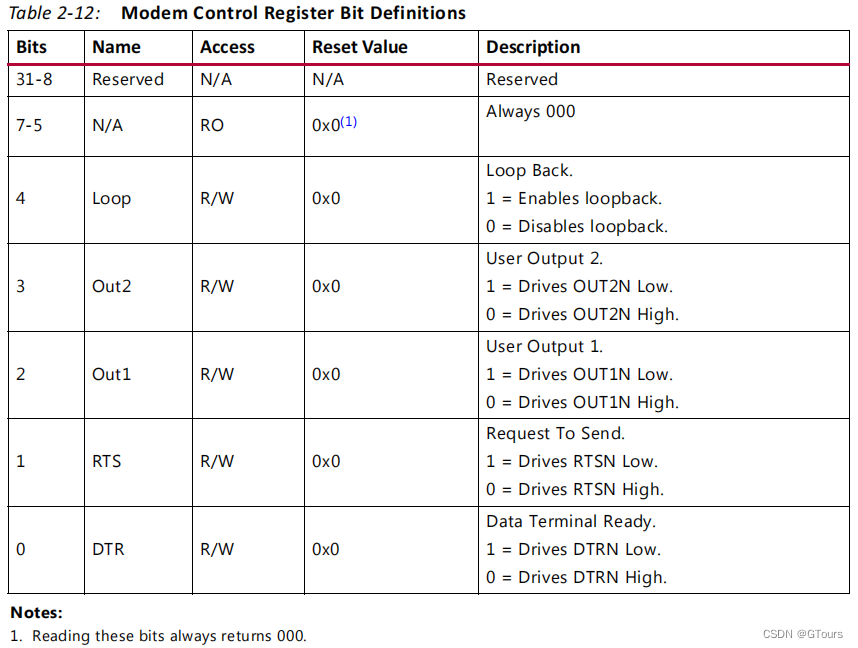

- 调制控制功能

- 中断:电平触发(level-sensitive)、可屏蔽、优先级(can be masked and prioritized),包含传输、接收、线路状态、调制解调器中断

- 起始位错误检测与复位

- 内部回环测试

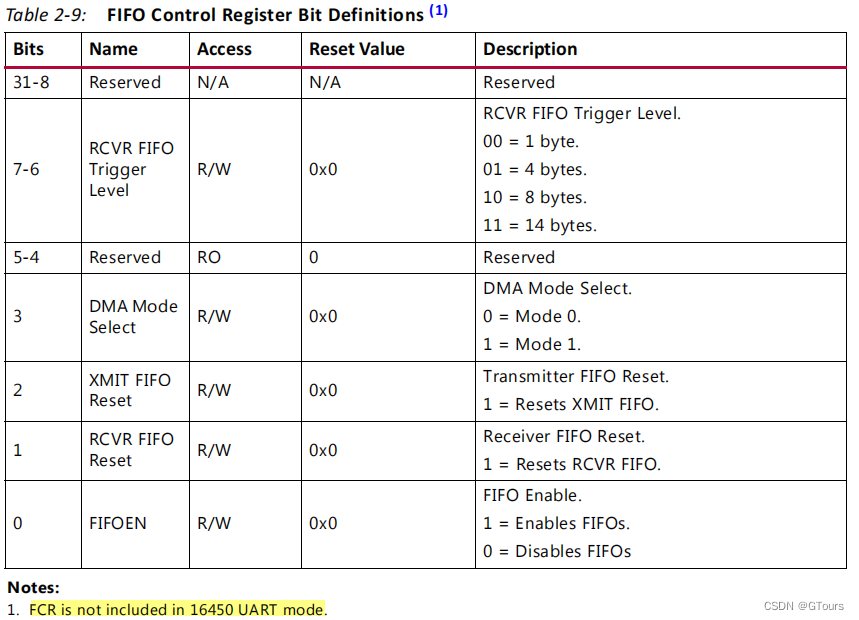

- 16bit、可编程、独立、16字节长度的接收和发送FIFO,FIFO可使能控制

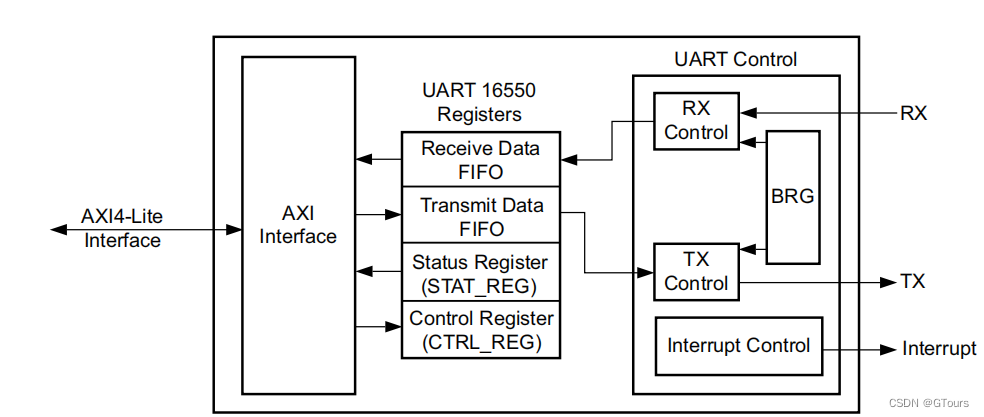

二、框架

RX:UART RX引脚—>Receive Data FIFO

TX:Transmit Data FIFO—>UART TX引脚

BRG:Baud Rate Generator

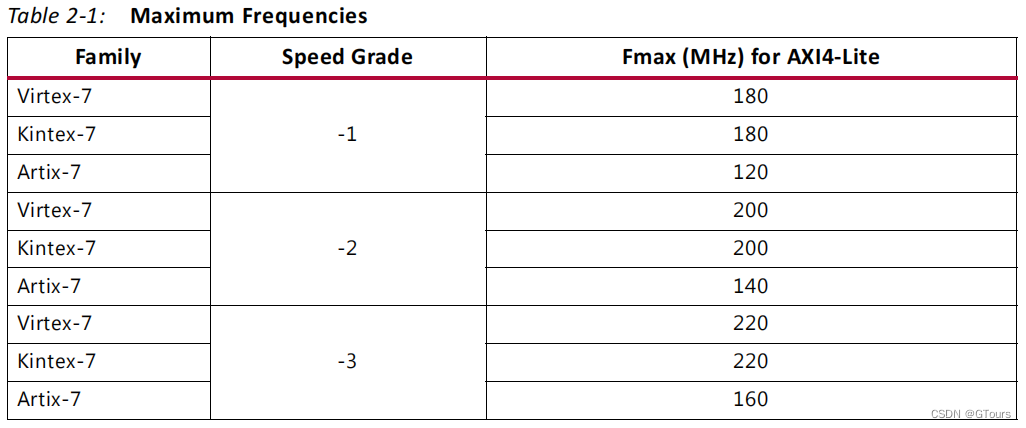

三、时钟

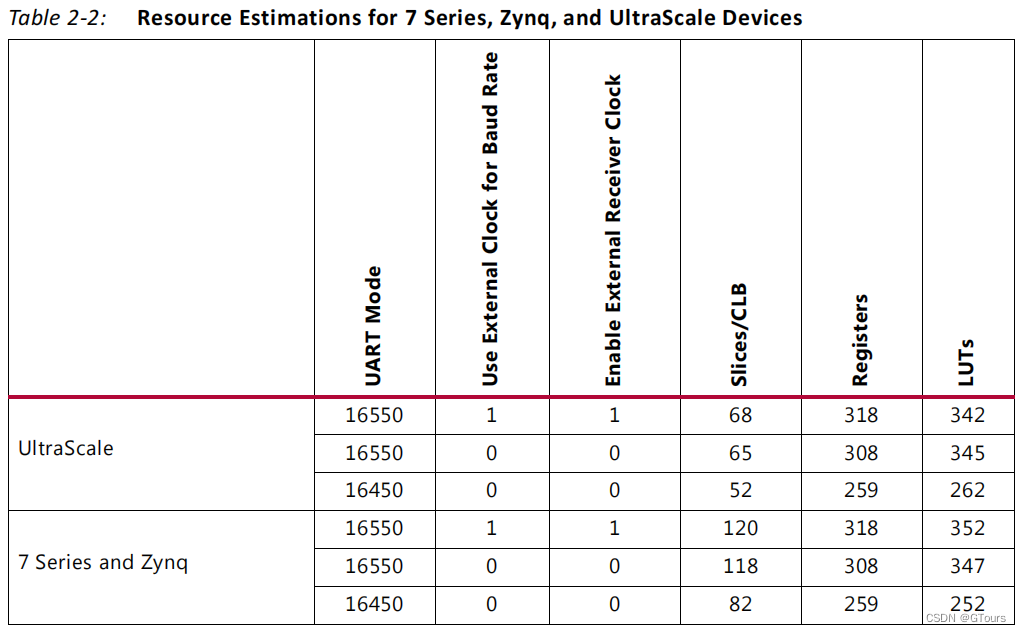

四、资源占用

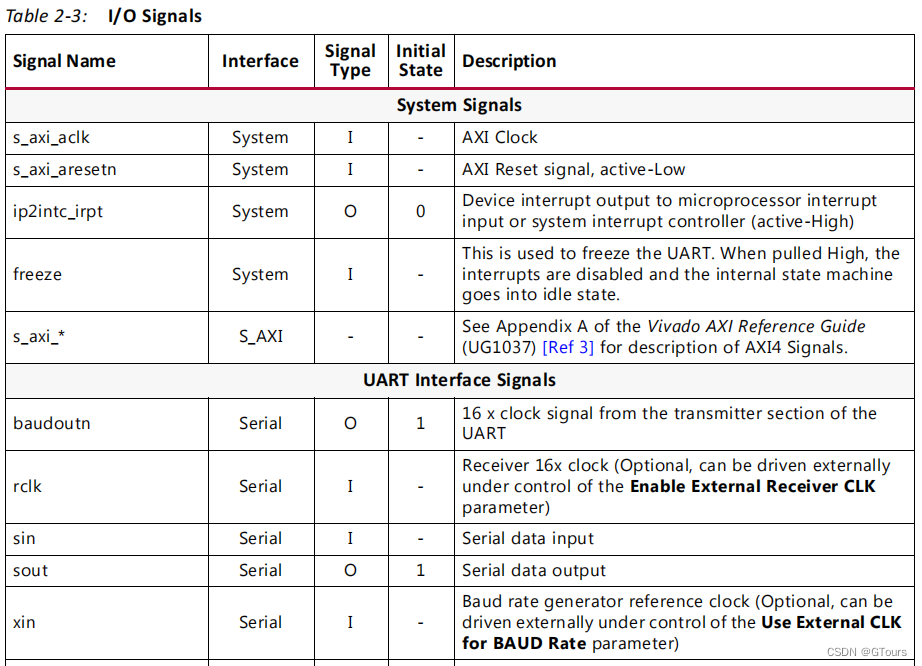

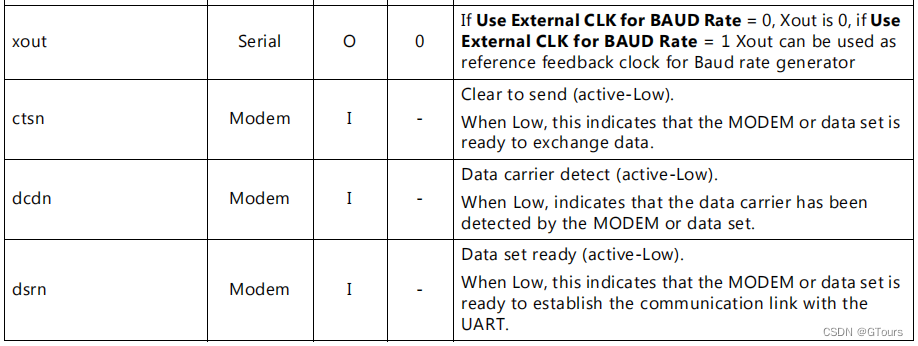

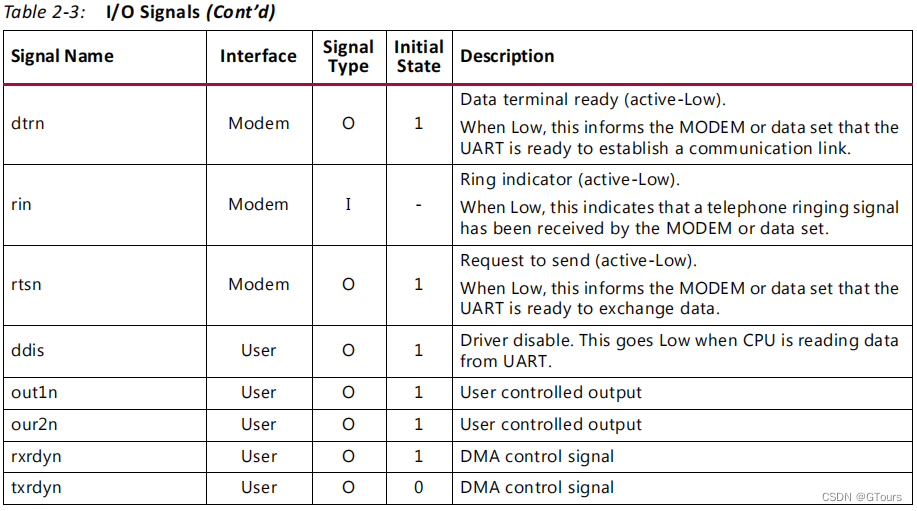

五、信号

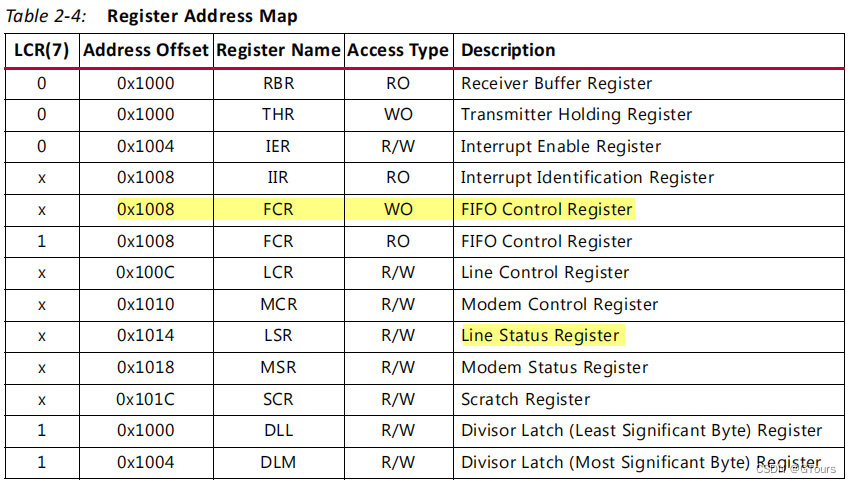

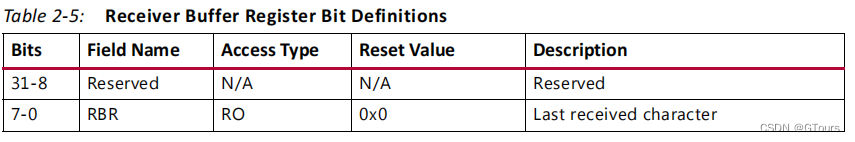

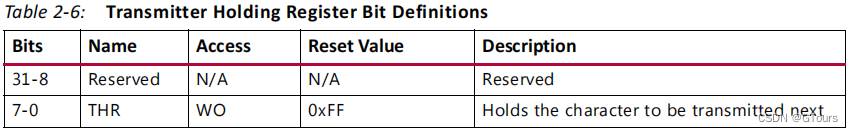

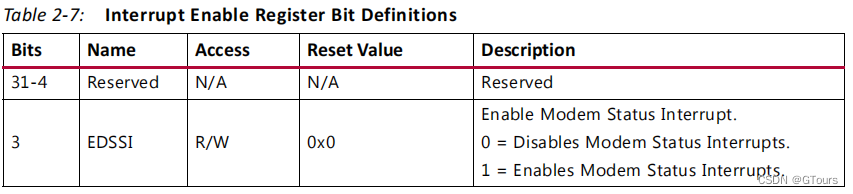

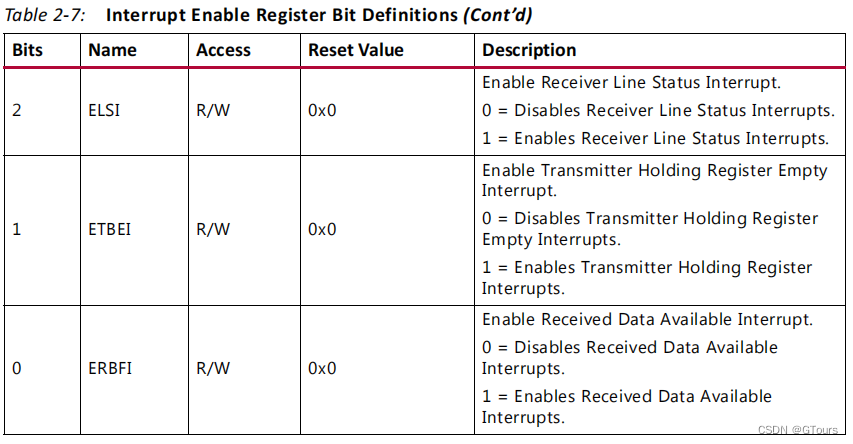

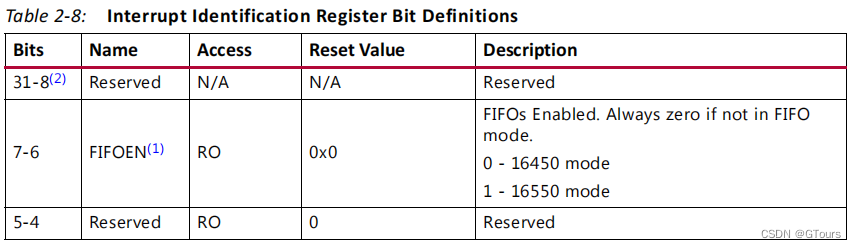

六、寄存器

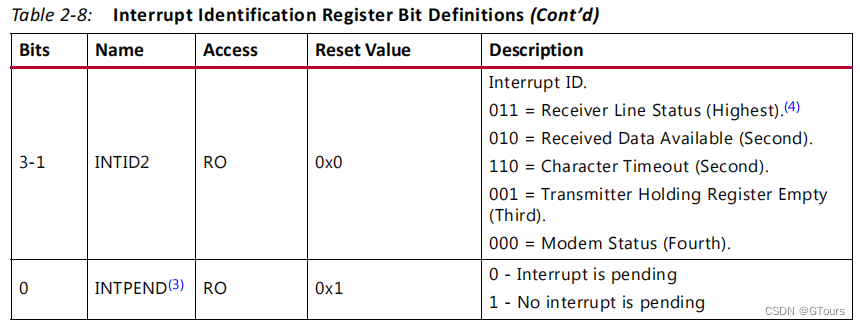

七、中断

中断类型包括:Receiver line status、 Received data available、 Character timeout、 Transmitter holding register empty、Modem status

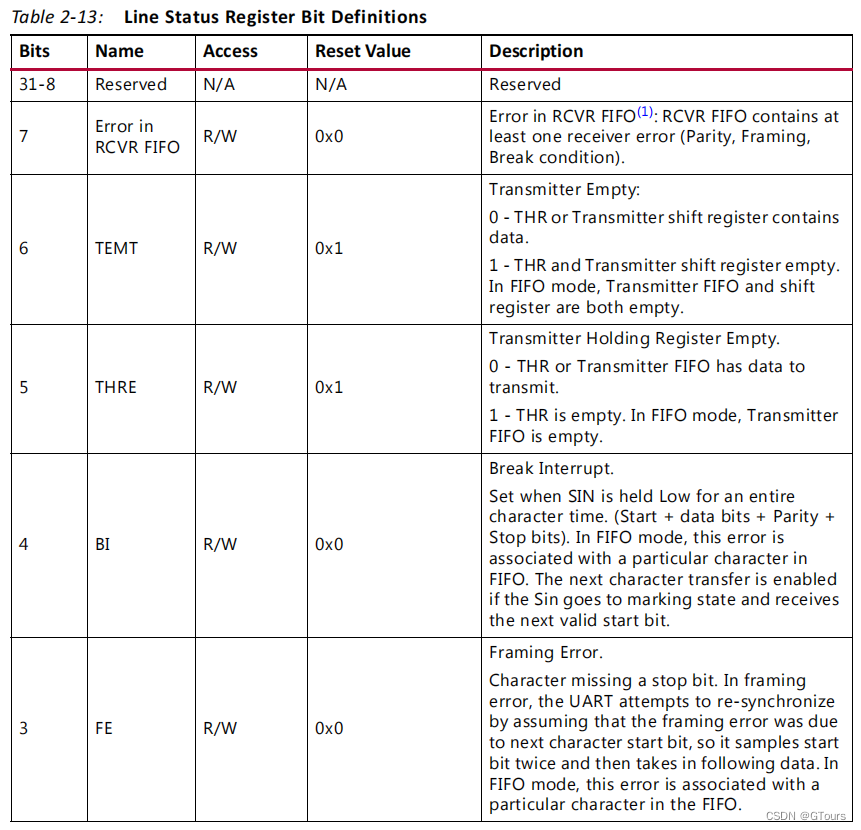

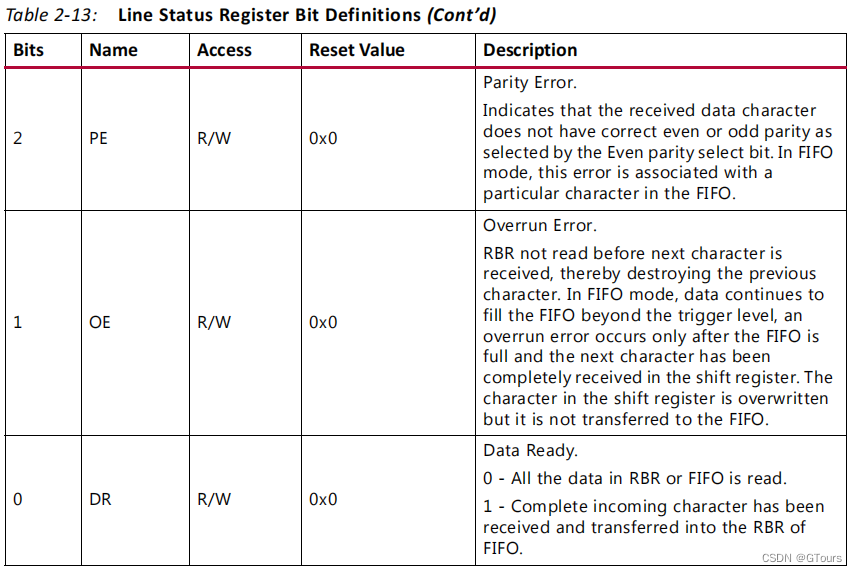

Receiver line status:溢出错误(Overrun error,非FIFO模式:当前字符未取走,下个字符又接收到;FIFO模式:fifo满了且收到新的字符)、校验错误( Parity error,校验位无效)、帧错误( Framing error,停止位无效)。这些中断信号寄存器读走之后将被清除。

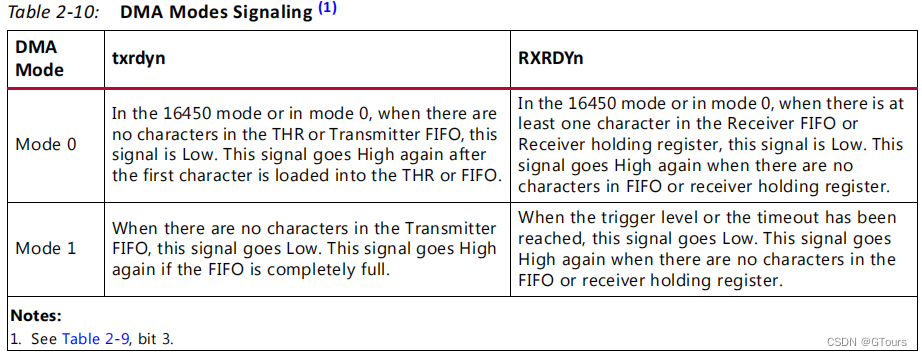

Received Data Available:接收FIFO达到触发条件(FCR bit7:6配置,1字节或4字节或8字节或14字节)。FIFO内字符数少于阈值时,中断清除。

Character timeout:字符超时:接收FIFO中至少包含一个字符,此时再等待四个字符时间一直没有数据写入或去除,则认为超时。单个字符超时时长:起始位+8个数据位+校验位+2个停止位。读取Receiver Buffer register时清除中断。

Transmitter holding register empty: Transmitter FIFO为空。读取Interrupt identification register (IIR) 或者向Transmitter holding register写入数据时清除。

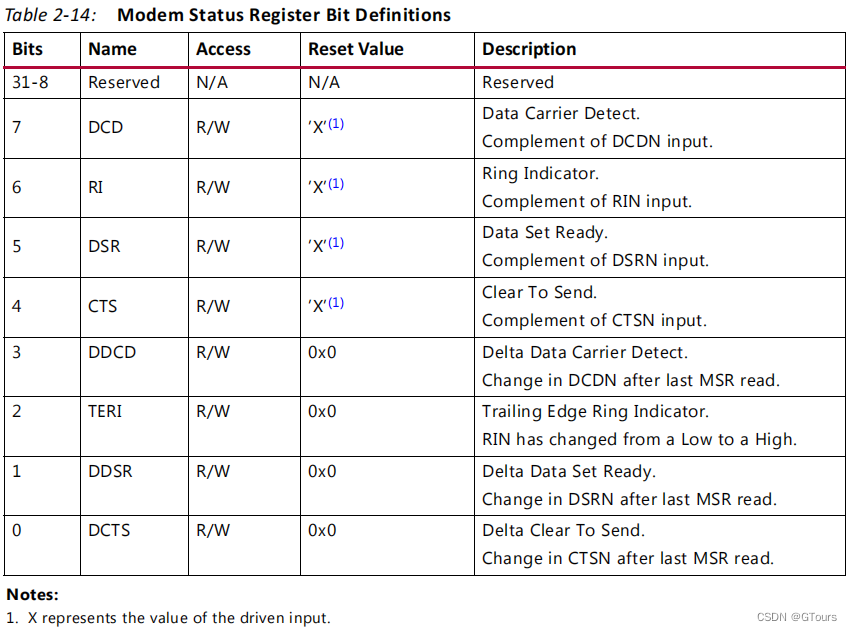

Modem Status: Clear to Send、Data Set Ready、Ring Indicator、Data Carrier Detect。读取Modem Status register时清除。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?