路科验证 Today

The following article is from 数字ICer Author 数字ICer

一、前言

最近在学习 PCIE 总线协议,本人作为一个刚开始的小白,打算写写笔记加深下自己的理解。如果你也是刚开始入门的朋友,希望能你有所帮助。水平有限,如有错误,望批评指正。本人看的书主要有两本,一本是《PCI Express 系统结构标准教材》,《pci express system architecture》的中文版,还有一本是《深入浅出SSD》,由SSD技术社区SSDFan核心成员撰写,后者对于初学者而言更为友好一点。

.

概述

PCIe是从PCI发展过来的,“e” 是 “express”的简称,是“快”的意思,PCI使用并口数据传输,PCIe使用串口传输,但是PCIe的速度更快。并口传输每次可以传送多位数据,但是为何比串口慢?这便要考虑并行总线的时钟频率问题。

在低频情况下,并口传输确实比串口要快。在对传输速度不断提升的同时,时钟频率也需要不断提高,并口传输便会有一些问题。

如上图所示,在发送端,公共时钟第一个上升沿到来时,将多位数据发送出去。数据通过传输介质到达接收端,接收端在公共时钟第二个上升沿对数据进行采集。接收端需要接收正确的数据,就必须要保证数据在传输介质中的传输时间小于公共时钟周期,传输时间还随数据线长度增大而增大。受限制于传输时间,时钟频率无法做的很高。并且由于并行传输,每位数据到达接收端的时间都不相同,存在相位偏移,必须要等到最慢的那个bit数据到达,才可以进行采集。

PCIe使用串行传输便能避免上述问题,由于是一位一位的传输,不存在相位偏移。它的时钟信息通过8/10编码或者128/130编码(这个后面会说)嵌入在数据流中,接收端可以从数据流中恢复时钟信息。但是如果使用多条串行通道并行传输,便又会存在上述问题,PCIe有相应机制解决好这个问题。

.

PCIe速度

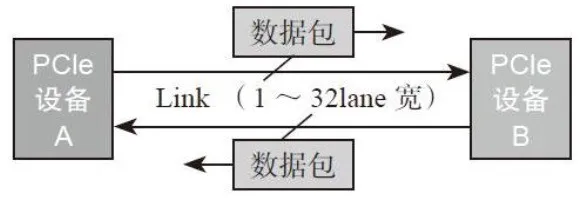

两个PCIe设备之间的连接,称为一个 Link,一个Link有两个方向,一边发送,一边接收,可以同时进行,这种通信方式称为全双工。每个方向上可以有 1~32个lane并行,每个lane 代表一对串行通道。

8/10编码:在串行通道上传输时,将 8bits数据编码为10bits数据,做一个转换,使各位数据之间有更多的 1到0 和 0到1 的跳变,以便接收设备检测这些跳变,能更容易地恢复时钟。128/130编码的原因也是类似的。

这

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

2281

2281

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?