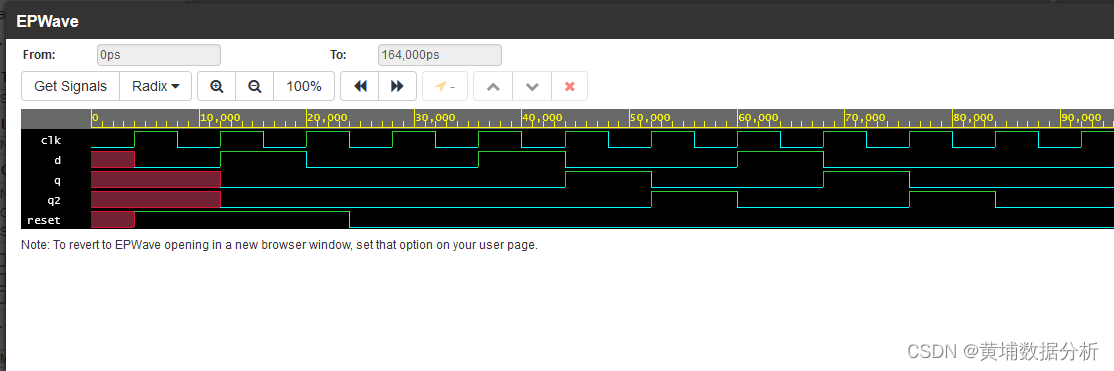

d 放在always中

`timescale 1ns/1ps

module d_ff_tb ();

reg reset;

reg d;

wire q,q2;

reg [7:0] cnt;

reg clk;

always #4 clk <= ~clk;

initial

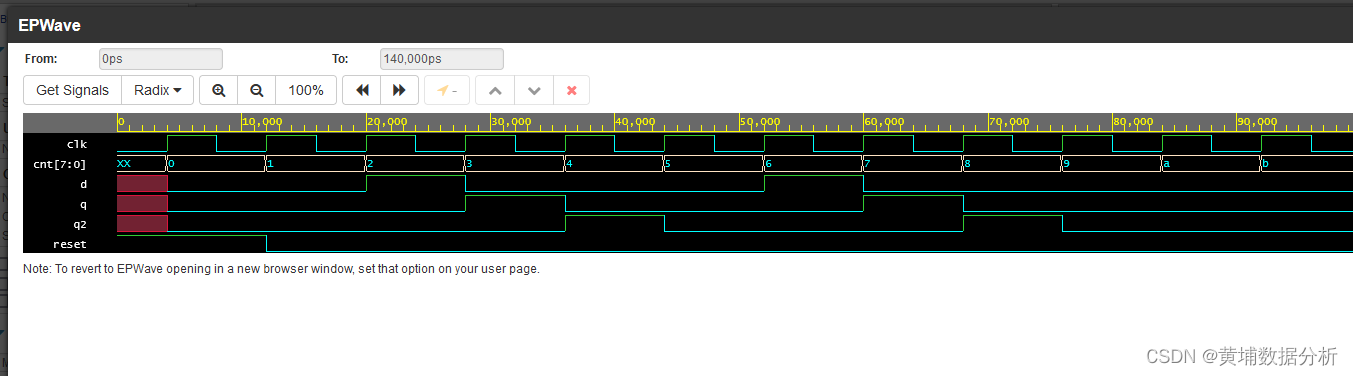

d 放在always中

`timescale 1ns/1ps

module d_ff_tb ();

reg reset;

reg d;

wire q,q2;

reg [7:0] cnt;

reg clk;

always #4 clk <= ~clk;

initial

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?