写在前面

- 个人微信公众号: FPGA LAB

- 个人博客首页

- 注:学习交流使用!

本文我们将讨论两个问题:

- 什么是锁存器?

- 如何避免生成锁存器?

正文

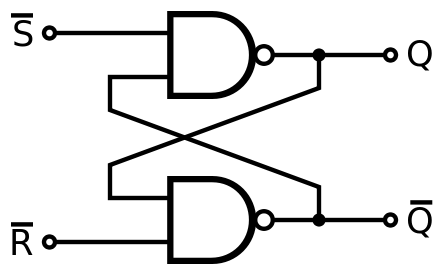

在FPGA设计中永远不要使用锁存器!但好像没人在FPGA设计中故意设计锁存器,那为什么要讨论锁存器呢? 话虽如此,虽然你没有有意设计锁存器,但你能保证你的代码中没有锁存器了吗? 综合工具(将Verilog或VHDL代码转换为低级FPGA组件的工具)生成的常用锁存器是 门控D型锁存器。但是,还有其他类型的锁存器:SR锁存器,D锁存器,JK锁存器和Earle锁存器。这些类型的锁存器不在本文讨论范围内,如需了解,可以自行查询资料。

什么是D锁存器?

门控D锁存器有两个输入和一个输出。框图如下所示。输入D是您的数据输入。输入E是你的输入输入。仅当Enable为1时,输出Q才会获得D上的值。当Enable为0时,无论输入D在做什么,输出都不会改变,即保持。它保持其先前的值,因此为什么将其称为锁存器! 当使能为低电平时,输出被锁存。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

2万+

2万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?