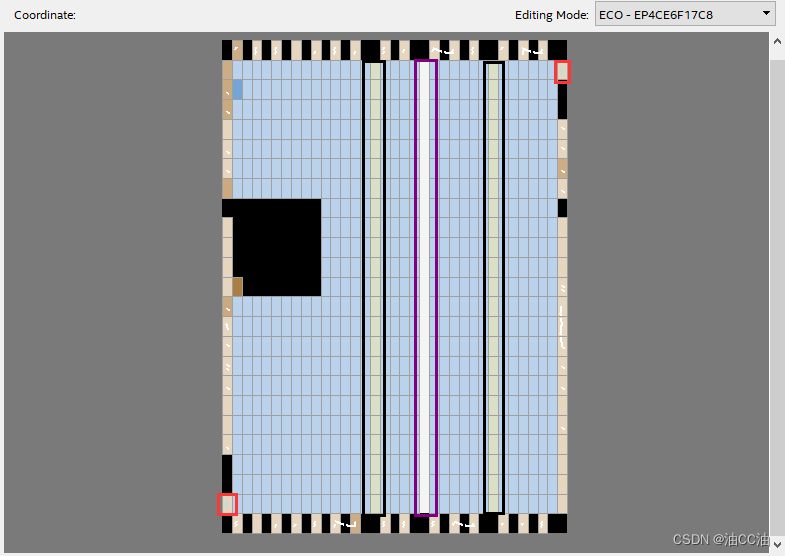

FPGA内部资源结构——以Altera CycloneⅣ 为例

FPGA基础结构

在Altera的CycloneⅣ芯片中,有以下基础组成部分:

1、LAB(Logic Arry Block):逻辑阵列块;(图中的浅蓝色小方格)

2、可编程输入输出单元:IOB;(图中周围浅色部分)

3、嵌入式块RAM;(图中黑色方框部分)

4、丰富的布局布线资源;

5、时钟资源;

6、底层嵌入功能单元。(PLL图中红色部分、DSP图中紫色部分)

逻辑阵列块LAB/可配置逻辑块(CLB)

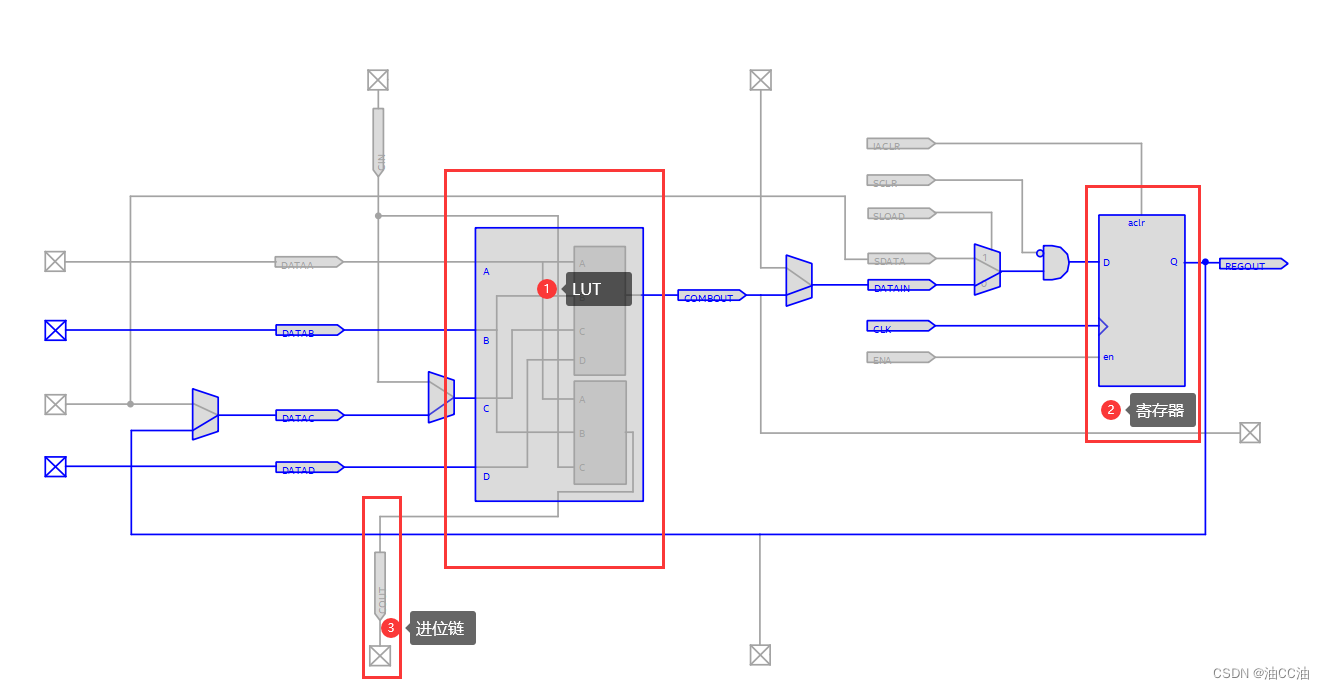

1个LAB由16个LE(Logic Elcment)组成,LE是完成用户逻辑的最小单元。LE主要由:一个4输入的查找表(LUT)、一个寄存器 (Register)、一条LE之间的进位链、寄存器级联链等连线与控制资源组成;而查找表和多路选择器用于实现组合逻辑功能,再加入了寄存器之后实现了时序逻辑功能。LE内部结构如下图:

当前主流FPGA都采用基于SRAM工艺实现查找表功能。FPGA开发软件会自动计算经HDL设计的逻辑电路的所有可能结果,并将其列成一个真值表,并最终将真值表存入LUT,每当输入一个信号进行逻辑运算时,就相当于输入一个地址进行查表,根据输入,找到对应地址存储的内容输出。上图使用的是4输入1输出的LUT,及存储容量是16×1bit。

可编程输入输出单元:IOB

为使FPGA具有更灵活的应用,目前大多数FPGA的I/O单元被设计为可编程模式,即通过软件的灵活配置,可适应不同的电器标准与I/O物理特性;可以调整匹配阻抗特性,上下拉电阻、输出驱动电流的大小等。

嵌入式块RAM(Block RAM)

嵌入式块RAM可以配置为单端口RAM、双端口RAM、伪双端口RAM、CAM、FIFO等存储结构,在存储少量数据或进行跨时钟域通信处理时常用,Block RAM 由一定数量固定大小的存储块构成的,使用 Block RAM 资源不占用额外的逻辑资源,并且速度快。但是使用的时候消耗的 Block RAM 资源是其块大小的整数倍。

丰富的布局布线资源

布线资源连通 FPGA 内部所有单元,连线的长度和工艺决定着信号在连线上的驱动能力

和传输速度。布线资源的划分:

(1) 全局性的专用布线资源:以完成器件内部的全局时钟和全局复位/置位的布线;

(2) 长线资源:用以完成器件 Bank 间的一些高速信号和一些第二全局时钟信号的布线;

(3) 短线资源:用来完成基本逻辑单元间的逻辑互连与布线;

(4) 其他:在逻辑单元内部还有着各种布线资源和专用时钟、复位等控制信号线

时钟资源

专用输入时钟引脚、锁相环(PLL)、时钟控制模块(选择时钟以提供时钟布线网、可启用/

禁用时钟以节能)、时钟布线网络(全局时钟网络驱动整个设备、局部时钟网络驱动特定的

设备区域)

底层嵌入功能单元

底层嵌入功能单元是指通用程度较高的嵌入式功能模块。如锁相环(Phase Locked Loop,PLL)、DLL(Delay Locked Loop)、DSP(Digital Signal Processing)和 CPU 等。 PLL的参考时钟输入都是由专用时钟管脚上的晶振进来的,用以完成时钟的高精度、低抖动的倍频、分频、占空比调整、相移等功能。PLL出来的时钟都会连接到全局时钟网络上,通过全局时钟网络扇出到每个寄存器上的时钟线,全局时钟网络保证时钟的质量,减小时钟偏斜(Skew)和抖动(Jitter)。DSP、CPU等主要用于各种复杂的数学运算,乘法、除法以及常用的功能函数如:有限冲激响应滤波器(FIR),无限冲击响应滤波器(IIR),快速傅里叶变换(FFT),离散余弦变换(DCT)等,这些功能函数在运算时会消耗很多逻辑资源,而FPGA中的LUT和寄存器资源有限,这时候使用嵌入式乘法单元这部分资源就不会造成逻辑资源的浪费

597

597

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?