我们介绍完中断异常后,将介绍RISCV的软件开发---->verilog硬件设计语言---->modelsim仿真---->安路科技的国产FPGA、高云的国产FPGA---->针对明年电子竞赛国赛专门设计的国产FPGA板子(riscv处理器实现、freertos移植、电机控制、常见的通信调制解调、图像采集识别、高速数据采集等内容),我们将沿着这条主线以国产FPGA+RISCV处理器+明年国赛准备,为童鞋们介绍RISCV处理器的应用。因为国赛,不是所有童鞋都愿意或有能力使用国产FPGA+自己设计的处理器参赛,我们同时在微信公众号"电路与电测"中推出另一个系列推文:stm32cube库函数编程。

1.跳转到mtvec指示的PC地址重新取指令执行

....见前一个推文.....

2.更新CSR寄存器mcause

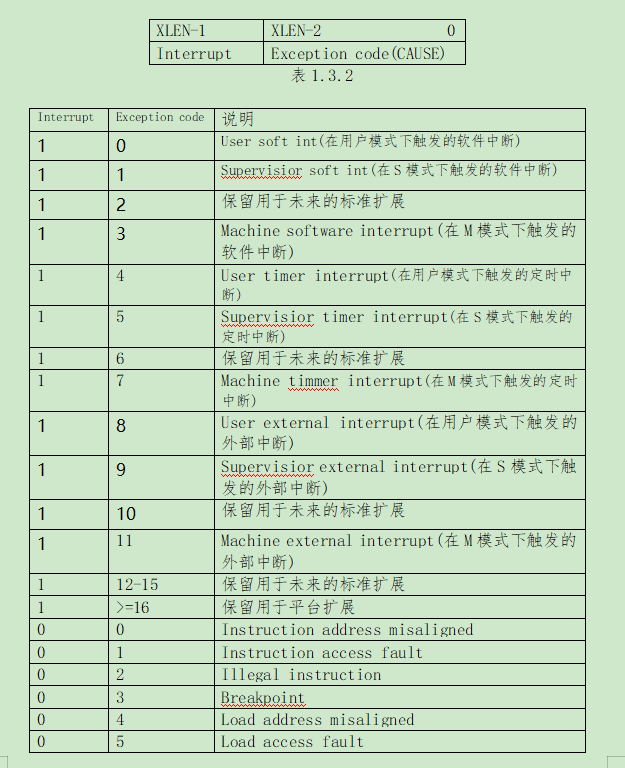

RISC-V架构处理器在进入异常时,机器模式异常原因寄存器mcause (Machine CauseRegister)已经被更新,其记录了当前的异常类型,软件可以通过读此寄存器查询造成异常的具体原因。mcause寄存器的详细格式如表1.3.2所示,其中最高1位为Interrupt域,低31位为异常编号(Exception code)域。 此两个域的组合表示值如表1.3.3所示,共计12种中断类型和16种异常类型。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

674

674

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?