【芯人类】EDA 是芯片之母是IC设计最上游、最高端的产业。也是中国集成电路产业最薄弱的环节。为向集成电路专业师生和从业者中系统介绍EDA技术的前沿进展,芯人类将分多期全文引入《电子报》EDA前沿技术专栏。专栏特邀行业多位专家,全面系统地介绍国内外EDA 的状况和国产EDA 的发展。本文为电子报授权发表。

1

引 言

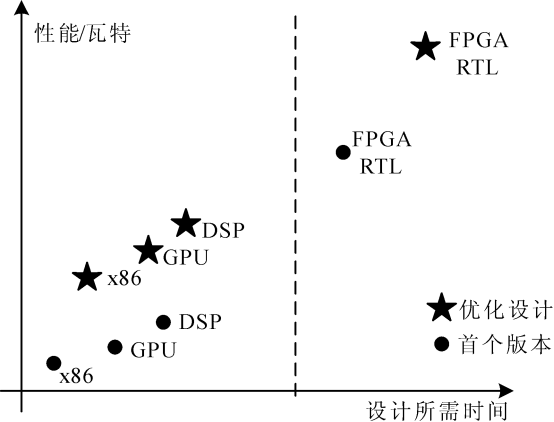

近年来,电子系统设计日益复杂。一个典型的电子系统通常包括不止一个基于嵌入式处理器和FPGA,还需要一个基于通用处理器或者高性能嵌入式处理器的图形界面系统进行前台处理、显示、调试。以星载北斗导航接收机的设计为例,嵌入式处理被用于导航解算和遥控遥测处理,FPGA被用于导航信号处理,包括信号的快速捕获和跟踪;而通用处理则至少被用于遥控遥测的显示和过程调试。不同的处理平台的灵活性和设计工具不同,所需的设计时间和应用性能也不同,其定性比较如图1。基于处理器的设计平台(包括x86、GPU和DSP等)通常能够提供非常高的软件灵活性和较短的设计时间,但其局限性是体积大、功耗大,对外接口受限;基于FPGA的设计能够提供良好的接口灵活性和最高的应用性能,但设计所需时间远远超过基于处理器的平台。

图1不同处理平台所需设计时间和应用性能比较

在现代航天系统中,为确保计算能力,并降低空间环境对系统可靠性的影响,通常采用多个嵌入式处理器加FPGA的计算处理平台,在可靠性和性能之间实现有效平衡。多处理器和FPGA带来的首要问题就是设计变得更加复杂。在传统的设计流程中,整个系统的设计需要经历系统设计、处理器软件设计、FPGA设计、系统调试、系统测试等流程。通常,这一设计过程是一个迭代过程。传统的系统设计阶段通常以文档形式形成概要设计和详细设计文档。为了降低设计风险,通常采用比需求高得多的处理器和大规模FPGA,这种方法导致了很多系统的过设计。而且,复杂算法也难以通过文档清晰表述,算法设计专家所设计的算法通常以C/C++甚至MATLAB表述,实现工程师理解算法通常需要时间,且往往会出现偏差。

对于多数项目而言,FPGA的设计通常是最大设计延迟路径和工程难点。近年来,为提升设计效率,设计语言不断发展,System Verilog、SystemC比原有的Verilog/VHDL具有更高设计输入效率,高层次综合(High Level Synthesis)、系统IP生成(System Generator)等工具和UVM、OVM等验证方法学进一步提高了FPGA的设计效率。就整个电子系统而言,能否用一种统一的语言描述从系统设计规范到RTL的整个设计,并能够自动通过工具自动翻译为FPGA设计,能够直接使用的RTL级设计、脚本,以及处理器编译器所需C/C++设计?在

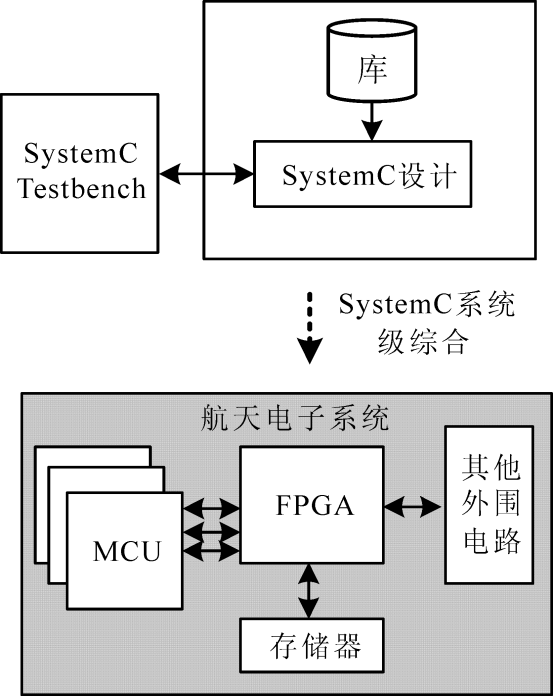

本文中,我们面向Xilinx FPGA设计,探讨基于SystemC的电子系统级设计方法在多处理器航天电子系统中的应用。该方法针对航天电子系统的特点,采用SystemC作为整个电子系统的统一设计语言,在系统层次描述和评估整个系统的行为。设计完成的SystemC设计进一步通过工具自动翻译为处理器所需要的C++代码和Xilinx Vivado FPGA设计工具所需要的设计输入。这种方法可有效提升复杂电子系统的设计效率。

GA带来的首要问题就是设计变得更加复杂。在传统的设计流程中,整个系统的设计需要经历系统设计、处理器

2

基于SystemC的电子系统级设计

2.1SystemC介绍

SystemC始于1999年,是一种基于C++的硬件描述库,并于2005年成为IEEE Std 1666标准,是与VHDL/Verilog/System Verilog并列的硬件描述语言。由于是基于C++的标准,因此SystemC可以描述系统级、事务处理级、寄存器传输级、门级、模拟级各个等级的电子系统,SystemC还定义了专门的验证库和事务处理库。尽管如此,SystemC的最佳实践是建模系统级、事务处理级和算法级的设计。在新一代的设计语言中,System Verilog大大提高了RTL设计效率、设计准确性和验证效率,而SystemC更擅长描述

复杂的算法和控制流程,描述整个复杂的电子系统的复杂行为。由于设计工具仍然在发展中,SystemC的应用主要在大型设计中,因此不如语言System Verilog应用广泛。近年来,常见的电子设计自动化工具如Vivado、Catapult都支持SystemC,在设计仿真阶段,也可以使用Visual Studio作为工具开发SystemC设计。

2.2目标设计平台

如下图所示,本文所描述的基于SystemC的电子系统级设计面向目标多处理器+FPGA,航天硬件电路包括CPU子系统、FPGA、存储器和其他外围电路。与地面系统不同的是,为了兼顾计算性能和可靠性,低成本航天系统通常采用多个处理器来构成处理器子系统,比如多个ARM单片机来构成处理器子系统,每一个单片机都具有独立的内置Flash和SRAM,都支持浮点运算,且典型主频不低于300MHz。

图2基于SystemC的航天电子系统级设计框架

在图2所示的框架中,系统的详细设计以SystemC的形式体现,包括软件、算法和FPGA外围电路的行为。SystemC代码可以像传统C++可执行文件的方式执行,既可以生成波形文件,也可以输出MATLAB可读的数据文件。在SystemC设计时,可以调用各种事务处理级的抽象模型,如存储器模型、各种通信接口。

(未完待续)

李挥 陈曦

来源:电子报

【免责声明】本文仅代表作者观点,不代表本公众号立场。本公众号转载此文出于传播资讯与分享知识之目的,如有侵权或违规之处请及时联系,将立即予以修正或删除

往期精选

提升 EDA 软件水平应从建立“工业软件意识”开始

ASML光刻机揭秘

刻蚀机揭秘

漫谈EDA产业投资(一)

漫谈EDA产业投资(二)

漫谈EDA产业投资(三)

2万+

2万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?