题目来源于:

https://hdlbits.01xz.net/wiki/Count_clockhdlbits.01xz.net前言:

新手入门,以下内容主要记录学习过程,便于后期改正。新人对语法、结构理解还欠缺,欢迎指出。

进入正题:

题目描述:

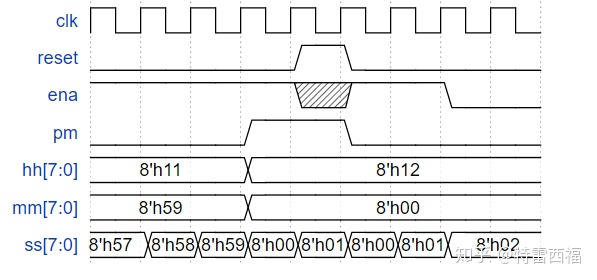

Create a set of counters suitable for use as a 12-hour clock (with am/pm indicator). Your counters are clocked by a fast-running clk, with a pulse on ena whenever your clock should increment (i.e., once per second).

reset resets the clock to 12:00 AM. pm is 0 for AM and 1 for PM. hh,mm, and ss are two BCD(Binary-Coded Decimal) digits each for hours (01-12), minutes (00-59), and seconds (00-59). Reset has higher priority than enable, and can occur even when not enabled.

大概意思:使用计数器设计一个12小时制的时钟。要求使用BCD,

本文记录了一位新手使用Verilog设计12小时制BCD计数器的过程,包括秒、分、小时的计数,其中小时计数需考虑AM/PM状态切换。设计中秒和分的计数器通过例化实现,小时计数部分单独处理,以适应12小时制的时间转换。

本文记录了一位新手使用Verilog设计12小时制BCD计数器的过程,包括秒、分、小时的计数,其中小时计数需考虑AM/PM状态切换。设计中秒和分的计数器通过例化实现,小时计数部分单独处理,以适应12小时制的时间转换。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?