1、GTH/GTY/GTM

- 一个GTH/GTY Quad=4个收发器=4个GTHE3或GTYE3单元;

- 一个GTM Dual=2个收发器=2个GTME3单元;

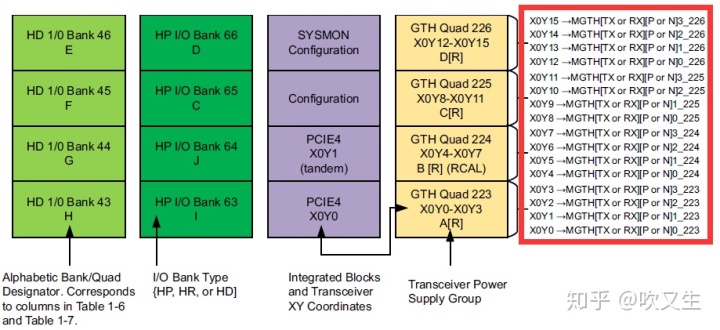

- 每个Qual/Dual中的XY坐标对应在该Qual/Dual的引脚中找到的收发信道号;如图1所示

说明:X表示集成编号,Y表示收发器编号

- 每个电源组均会标识,如_[L or R][N, UC, C, LC, or S]

2、I/O Bank

- 每个用户I/O Bank总共有52个I/O,其中48个可用作差分(24差分对)或单端I/O;其余4个仅能作为单端I/O。BANK的52个焊盘并不全是绑到引脚上。

- 数量有限的Bank只有少于52的SelectIO引脚。这类Bank被标记为partial。

- 与每个Bank相近的是物理层(PHY)包含一个CMT(时钟管理器)和其他时钟资源。

- 与每个Bank和PHY相近的是组成一个时钟区域的资源快。

- Bank间被排在列和分隔成行,这是与相近的PHY、时钟资源和GT块相匹配。

3、时钟

- 每个Bank有四对全局时钟(GC)输入用于四个差分或四个单端

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

549

549

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?