前面仿真基本没啥大问题,直接上板测试,终于到了最激动人心的时刻了。

接口定义

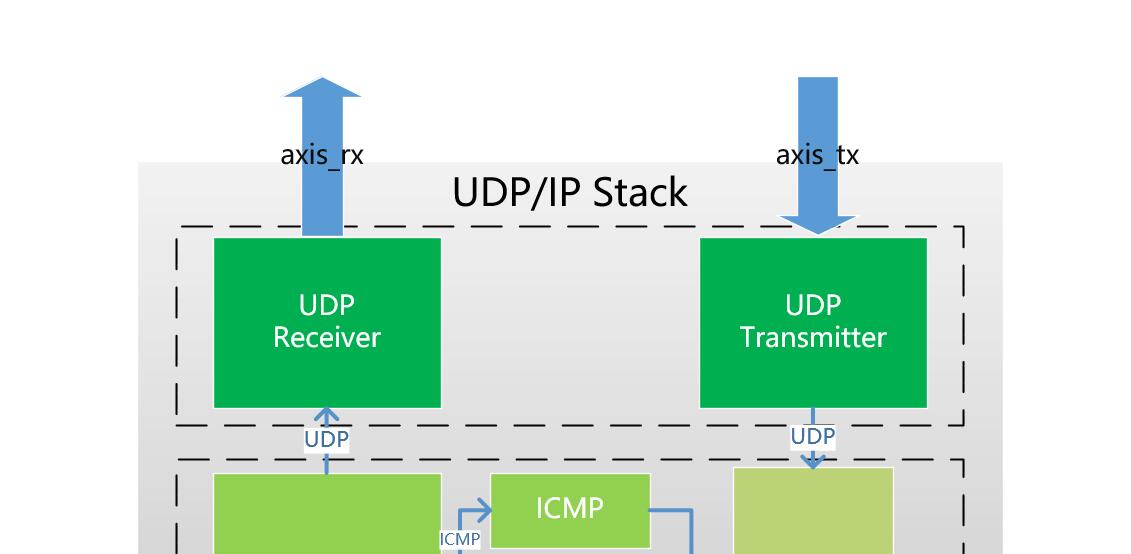

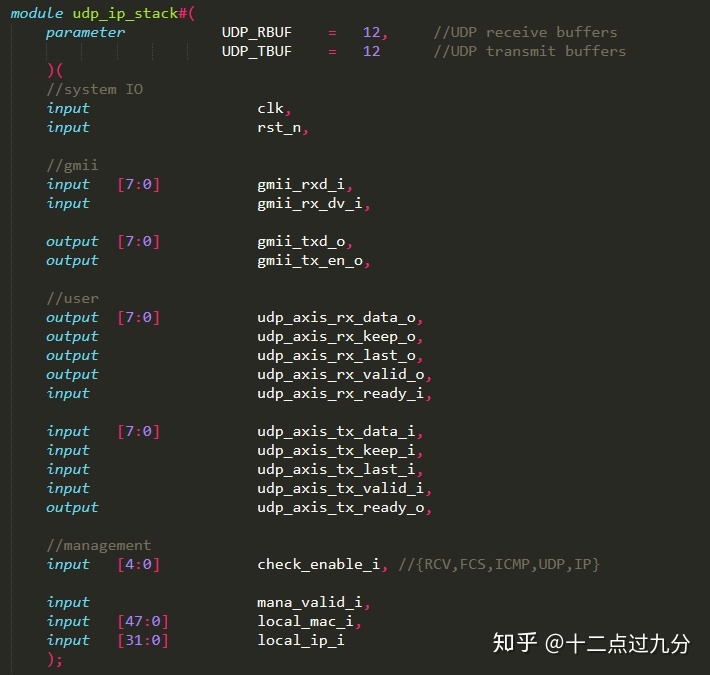

前面九篇文章依次将各模块的设计和仿真阐述完毕,终于得到了一个可用的弟弟UDP/IP协议栈,现在先说明该协议栈的接口信号的定义,如下图所示:

大致分为四类接口:

- 系统信号:包括时钟(clk)、复位(rst_n),其中时钟采用千兆以太网的125MHz时钟,复位采用低电平有效复位信号;

- GMII接口:包括接收端(Rx)、发送端(Tx)的数据信号和相应的有效信号,其中数据信号位宽为8 bit;

- 用户接口:包括接收端(Rx)、发送端(Tx),采用AXIS接口,数据位宽为8 bit;

- 管理接口:包括校验使能(checksum_enable)、本地MAC/IP地址及其有效信号,其中校验使能位宽为5 bit,分别对FCS、ICMP/UDP/IP的checksum进行使能,本地MAC/IP地址及其有效信号用于配置FPGA本机的MAC/IP地址,便于与外机通信;

此外,本协议栈可对UDP的接受和发送缓冲区大小进行配置,故采用parameter进行两个参数的配置,UDP_RBUF/UDP_TBUF分别表示接收/发送缓冲区,默认为12,即2^12 = 4096字节的缓冲区。

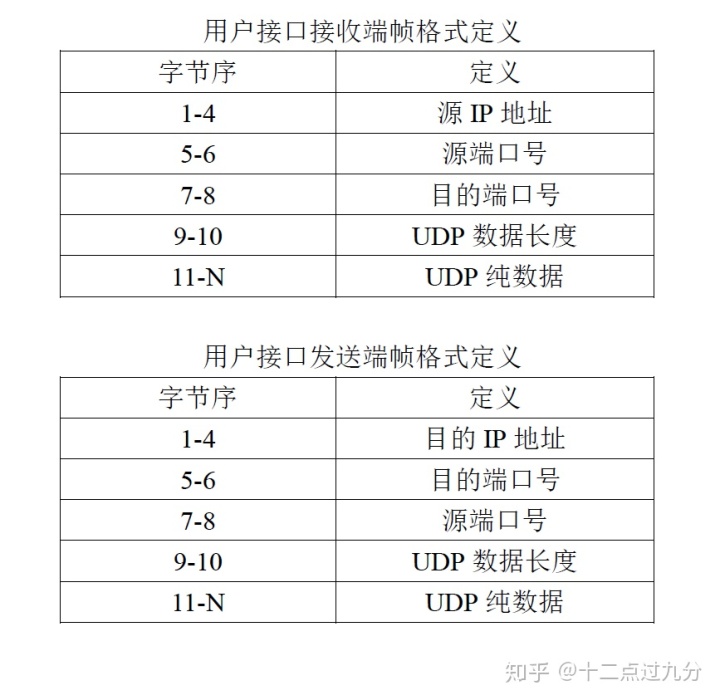

另,针对用户接口的帧格式定义如下(采用大端模式):

测试结构

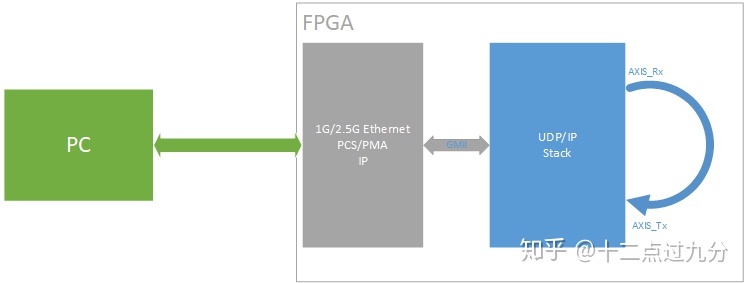

为实际上板本协议栈是否正常工作,故简单搭建了一个测试平台,基本结构如下所示:

在搭建的平台中:

- FPGA平台采用Xilinx的VC709评估版,FPGA开发平台采用Xilinx的Vivado 2018.3;

- 内部的以太网接口的PHY部分采用Xilinx的1G PCS/PMA IP,即FPGA对外的物理接口直接采用高速串行收发器,至于具体配置本文不再详细说明,可参见笔者其他文章进行配置;

- PCS/PMA IP与本协议栈模块之间采用GMII接口相连,其中不使用error信号;

- 对用户侧的接口采用回环形式,由于接口数据帧格式定义,接收端的源IP/端口等信号可直接作为发送端的目的IP/端口等;

- FPGA本地MAC地址设为48'haabb_ccdd_eeff(aa:bb:cc:dd:ee:ff),本地IP地址设为32'hc0a8_000a(192.168.0.10),校验全部使能(即接收校验正确后才进行处理,错误者直接丢弃);

- PC端的IP地址设为192.168.0.25(与FPGA在同一网段下),上位机软件使用网络调试助手进行测试;

上板测试

对于测试中的新建工程、综合、布局布线、下载bit、连线等操作,本文不再说明,下面针对本协议栈实现的功能分别进行测试

- ARP

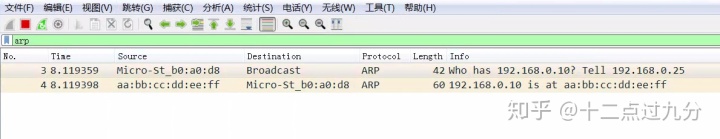

由于本协议栈针对ARP完成了请求的处理,而在使用IP协议进行通信时,主机必然将发送ARP请求进行获取MAC地址的操作,故测试该项时可进行ICMP或UDP通信间接测试ARP是否正确,例如进行ping操作,主机先发送ARP请求,wireshark抓包结果如下:

上述说明主机发送ARP请求帧到FPGA端时,可正常进行响应处理,即回复IP地址为192.168.0.10对应的MAC地址为aa:bb:cc:dd:ee:ff。

- ICMP

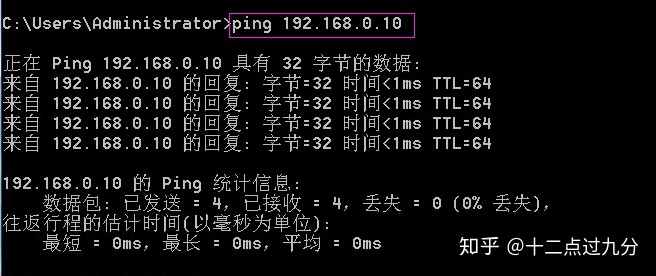

由于本协议栈针对ICMP协议只完成了回显请求(Echo)的处理,故测试该项直接打开CMD进行ping“192.168.0.10”的操作,结果如下:

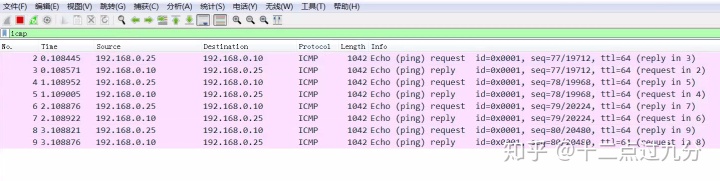

采用wireshark抓包,结果如下所示:

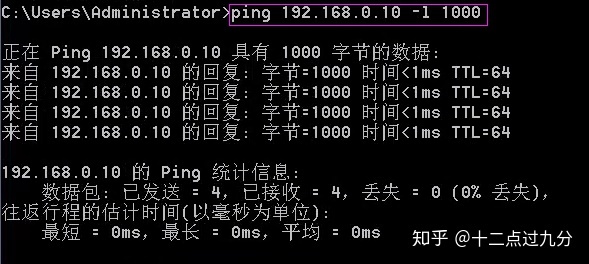

当然,可以再测试一些其他长度的ICMP报文,例如1000字节的测试情况如下:

上述测试说明,ICMP的回显请求(Echo)的处理基本没啥问题。

- UDP

由于搭建的测试平台采用的测试方式为UDP回环测试,即发送给FPGA的UDP数据帧与接收到的来自FPGA的UDP数据帧将一致,故采用网络调试助手进行简单的发包测试,即192.168.0.25:80发给192.168.0.10:81,发送一帧的测试结果如下:

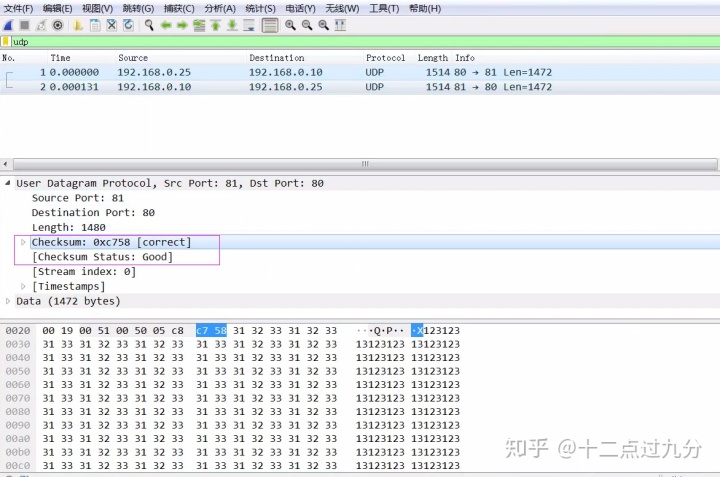

发送一帧UDP数据的wireshark抓包结果如下:

结果可知接收来自FPGA端的UDP帧,IP首部和UDP首部的Checksum均正确,故UDP处理基本无误。

由于时间原因不再作进一步吞吐量等其他的测试。

其他说明

经过简单测试,UDP/IP协议栈基本功能具备,性能凑活,算是基本达成最先的设计目标了。

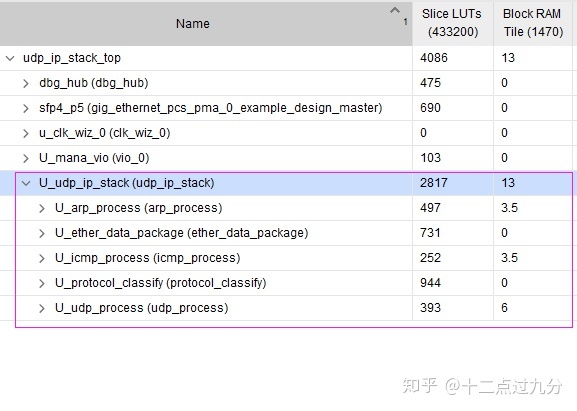

在接收和发送缓冲区均在4 KB的情况下,使用vivado 2018.3进行综合布局布线等,得到的资源利用报表如下图所示:

此外,本协议栈所有模块均直接使用Verilog编写,包括使用到的RAM和FIFO等,所以在Xilinx的FPGA平台上便于移植,基本上把模块实例化进行就可以直接使用了。

最后总结就是,基本完成UDP/IP协议栈基本功能,完成校验计算,接口定义简单,但消耗资源较多,完整协议功能未完成。

几天就撸完了代码,但是更新文章陆续花了一个多月时间,可算是更完了,经过这一波操作也算是对协议有了进一步的了解,算是收获颇多。

当然,对于协议栈逻辑的进一步优化和其他协议的完善得日后再说,反正又不是不能用,UDP/IP协议栈系列文章到此结束!

如有不足之处还望批评指正~

424

424

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?