ARM嵌入式系统硬件设计

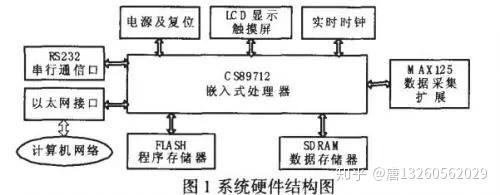

图1是系统硬件结构图“系统采用外部3.6864MHz的晶振产生内核所需要的18.432MHz、36.864MHz、49.152MHz或73.728MHz的时钟。

以下主要针对此硬件开发平台,进行结构、储存器扩展、主要接口、显示及其外设方面设计的介绍。

1、电源部分设计

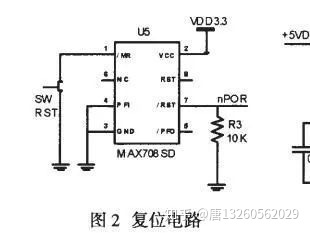

电源是系统可靠工作的保证,包括供电和复位电路部分。系统复位模块提供CS89712启动信号。系统采用nPOR信号作为复位信号,使用复位芯片产生复位信号。如图2:

整个系统的外部电源输入采用直流18V-36V,系统的供电较为复杂,电压等级多,其中CS89712芯片I/0和内核分别采用3.3V.2.5V供电,而扩展的MAX125、LCD显示器采用5V供电,同时LCD对比度调节需负电压偏置(选用MAX686芯片);而模拟量采集MAX125前向通道中滤波和电压跟随电路所用运放电源电压为正、负12V。

这里采用Ericsson的DC/DC电源模块PKC2131PI,提供隔离的正负12V和+5V,同

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

2089

2089

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?