关于这篇文章:

本文主要翻译自 RISC-V "V"(向量)扩展的官方文档,翻译版本为目前最新版的 RISC-V "V"(向量)扩展规范文档,小部分地方有删减及排版调整。

由于译者水平有限,本文可能存在谬误或不当之处,欢迎指正。

以下为正文(连载中):

8 向量 AMO 操作(Zvamo)

Note: 是否支持向量 AMO 操作在配置文件里说明。预期用于 Unix 的配置文件的基本“ V”扩展需要支持向量 AMO 操作。

如果要支持向量 AMO 指令,则必须存在标量 Zaamo 指令(标准 “A” 扩展的原子操作指令,atomic operations from the standard A extension)。

向量 AMO 指令编码使用标准 AMO 主操作码下未使用的编码。每个活跃元素可以对单个内存位置执行原子性的读、修改、写操作。

vamo-format.adoc

vs2[4:0] specifies v register holding address

vs3/vd[4:0] specifies v register holding source operand and destination

vm specifies vector mask

width[2:0] specifies size of index elements, and distinguishes from scalar AMO

amoop[4:0] specifies the AMO operation

wd specifies whether the original memory value is written to vd (1=yes, 0=no)vs2 向量寄存器保存每个元素的字节偏移量,vs3 向量寄存器为原子操作提供源数据。

除了没有 mew位(假定为零)外,AMO 与索引操作具有相同的索引 EEW 机制,因此偏移量只能有 EEW = 8、16、32、64。vs2 寄存器中字节偏移量的向量添加到 rs1 的基本标量寄存器中,从而得出 AMO 操作的地址。

数据寄存器 vs3 使用动态的 SEW 和 MUL 设置值。

如果 wd 位置1,则用内存元素的初始值写入 vd 寄存器。如果 wd 位清零,则不写入 vd 寄存器。

Note: 如果 wd 值明确的话,内存系统并不需要返回原来的内存值,vd 中的原始值将被保留。

Note: AMOs 可以部分覆盖源数据,从而对于实现寄存器重命名,可以减少总的内存管道读取端口数。同时也是为了支持与向量索引操作相同的寻址模式,并且也是由于主要用途是并行内存减少,向量 AMO 不太需要结果。

相对于同一 hart 中其他指令的排序,向量 AMO 操作就好像每个元素的 aq 和 rl 位均为零。

在同一向量 AMO 指令中的元素操作之间,向量 AMO 不提供任何顺序保证。

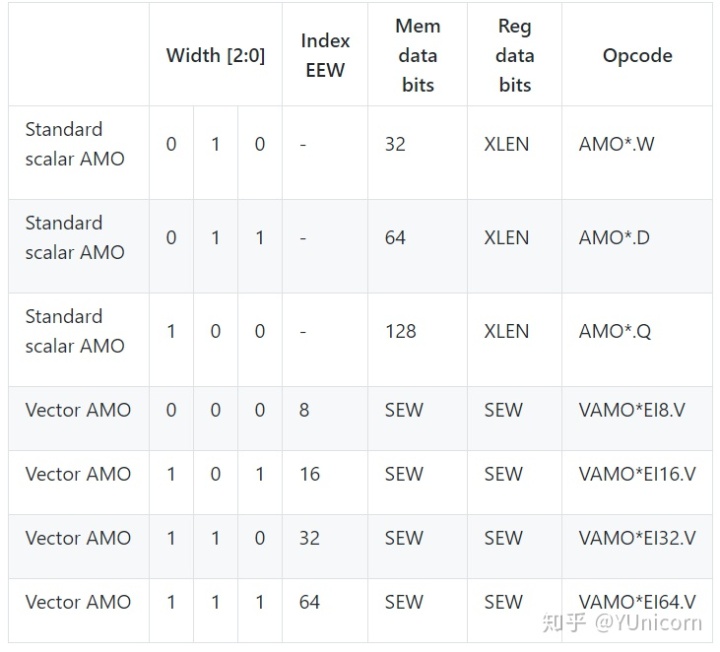

注:

索引位(index bits)是指偏移量的 EEW 。

内存位(Mem bits)是指在内存中访问元素的大小。

寄存器位(Reg bits)是指在寄存器中访问的元素的大小。

如果 EEW 小于 XLEN ,则 vs2 中的地址将加零扩展到 XLEN 。如果 EEW 大于 XLEN ,则会引发非法指令异常。

只有 AMO 支持的内存数据元素宽度才支持向量 AMO 指令。其他元素宽度会引发非法指令异常。

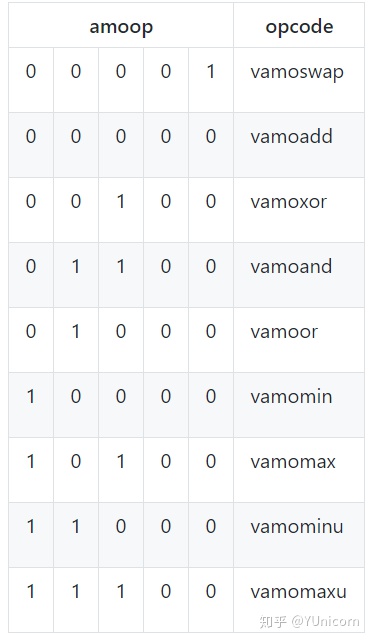

向量 amoop[4:0] 字段使用与标量5位 AMO 指令字段相同的编码,只是不支持 LR 和 SC 。

汇编语法中,目标寄存器位置使用 x0 ,表示不需要返回值( wd=0 )。

# Vector AMOs for index EEW=32

vamoswapei32.v vd, (rs1), v2, vd, v0.t # Write original value to register, wd=1

vamoswapei32.v x0, (rs1), v2, vs3, v0.t # Do not write original value to register, wd=0

vamoaddei32.v vd, (rs1), v2, vd, v0.t # Write original value to register, wd=1

vamoaddei32.v x0, (rs1), v2, vs3, v0.t # Do not write original value to register, wd=0

vamoxorei32.v vd, (rs1), v2, vd, v0.t # Write original value to register, wd=1

vamoxorei32.v x0, (rs1), v2, vs3, v0.t # Do not write original value to register, wd=0

vamoandei32.v vd, (rs1), v2, vd, v0.t # Write original value to register, wd=1

vamoandei32.v x0, (rs1), v2, vs3, v0.t # Do not write original value to register, wd=0

vamoorei32.v vd, (rs1), v2, vd, v0.t # Write original value to register, wd=1

vamoorei32.v x0, (rs1), v2, vs3, v0.t # Do not write original value to register, wd=0

vamominei32.v vd, (rs1), v2, vd, v0.t # Write original value to register, wd=1

vamominei32.v x0, (rs1), v2, vs3, v0.t # Do not write original value to register, wd=0

vamomaxei32.v vd, (rs1), v2, vd, v0.t # Write original value to register, wd=1

vamomaxei32.v x0, (rs1), v2, vs3, v0.t # Do not write original value to register, wd=0

vamominuei32.v vd, (rs1), v2, vd, v0.t # Write original value to register, wd=1

vamominuei32.v x0, (rs1), v2, vs3, v0.t # Do not write original value to register, wd=0

vamomaxuei32.v vd, (rs1), v2, vd, v0.t # Write original value to register, wd=1

vamomaxuei32.v x0, (rs1), v2, vs3, v0.t # Do not write original value to register, wd=09 向量内存对齐约束

如果通过向量内存指令访问的元素没有自然地与内存元素大小对齐,则该元素上会出现地址未对齐异常,或者该元素成功传输。

向量内存访问满足与标量内存访问相同的原子性规则。

10 向量内存一致性模型

向量内存指令似乎按程序顺序在本地HART上执行。向量内存指令在指令级别满足 RVWMO ,并且在指令内对元素操作进行排序,就像由句法独立的标量指令的元素排序序列执行一样。向量索引排序存储将元素按元素顺序写入内存。向量索引无序存储不保留单个向量存储指令中写入的元素顺序。

2698

2698

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?