目录

一、指令原理

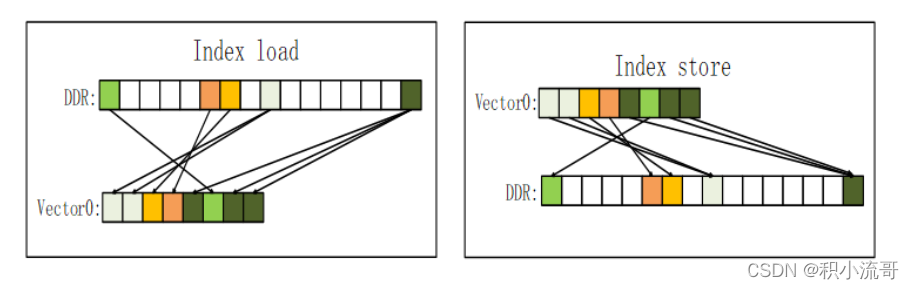

index load、index store指令用于在较大范围内完成数据gather/scatter的操作,实现难度很大。

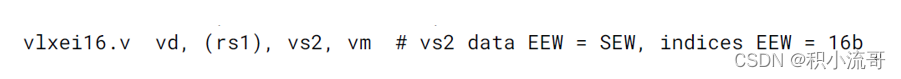

图1、RVV0.9版本的index load指令格式

图2、index load与index store指令功能示意图

index load、index store指令在VLSU(vector load store unit)中实现。

二、VLSU在系统中的位置

VLSU外接cache,内接VRF(vector register file),完成外部memory到内部register的数据搬入搬出功能。

此处之所以要特别指出VLSU的前后级关系,是因为两侧不同的访问方式,会影响到VLSU指令的实现机制。例如某种指令实现方式在多port cache结构时效率很高,但是在单port ca

本文详细介绍了RISC-V Vector Extension(RVV)中的index load指令,探讨了其在VLSU(vector load store unit)中的工作原理及其实现电路。通过地址合并优化,减少了cache访问次数,提出了适用于单port cache结构的解决方案。文章还展示了index load指令的实现流程,包括地址转换、重复地址消除和数据重排等关键步骤。

本文详细介绍了RISC-V Vector Extension(RVV)中的index load指令,探讨了其在VLSU(vector load store unit)中的工作原理及其实现电路。通过地址合并优化,减少了cache访问次数,提出了适用于单port cache结构的解决方案。文章还展示了index load指令的实现流程,包括地址转换、重复地址消除和数据重排等关键步骤。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

4625

4625

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?