前言

从结构上来讲,CPU的寄存器组,用来保存运算的中间结果,ALU(算术逻辑单元)执行逻辑运算,控制器指挥运算的各个部件。

从功能上来讲,可以理解成一个晶体管,通过电流驱动,高电压时为1,低电压时为0,形成一个开关,在这个基础上搭建积木,当CPU一秒可以执行4*10^9个指令,运算速度十分可观。

这些指令,用软件进行解释,输出到屏幕上,我们就看到了这篇文章。

一、寄存器

1.二进制加法

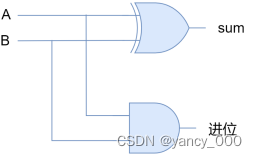

二进制相加,一个是结果(sum),一个是进位。

- 二进制相加,结果是异或门

异或门(ExOR gate):两路输入的电平不同,结果为1(高电平),输入结果相同时,结果为0(低电平)。

也就是说:

A=0, B=0,结果为0(输入A,B相同)

A=0, B=1,结果为1(输入A,B不同)

A=1, B=0,结果为1(输入A,B不同)

A=1, B=1,结果为0(输入A,B相同) - 二进制相加,进位是与门

与门(AND gate):输入同时为1(高电平)时,输出才为1,否则输出为0(低电平)。

A=0 + B=0,为0

A=0 + B=1,为0

A=1 + B=0,为0

A=1 + B=1,为1

2.记忆单元

记忆单元是存储二进制的最小存储单元,电路记得住信息,靠的是记忆单元。

-

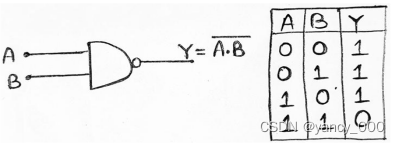

与非门(Nand门)

了解记忆单元前,先了解与非门

这个表是怎么得到的?

A=0 与 B=0 ,结果为0,取非,为1

A=0 与 B=1 ,结果为0,取非,为1

A=1 与 B=0 ,结果为0,取非,为1

A=1 与 B=1 ,结果为1,取非,为0 -

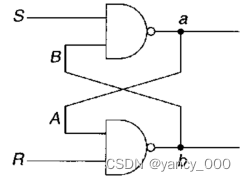

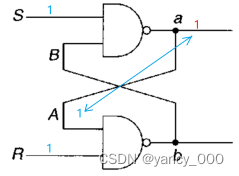

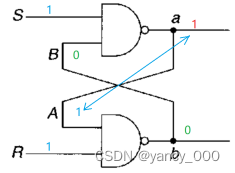

记忆单元的储值方式

假设S,R为1,a为输出端1

根据与非门的表格,可以补充出,R和A通过与非门得到的b为0,进而得到如下信息:

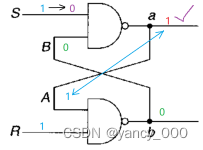

此时,S由1改变为0,则a被保存为1

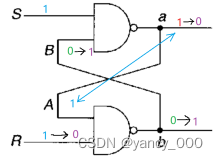

此时,改变R由1为0,b(B)改变为1,则a被保存为0

这时候,我们就把1或者0保存到电路中了

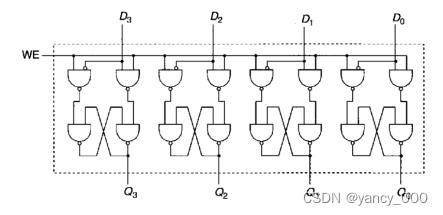

3.寄存器

记忆体的组合电路,就是寄存器,只要通电,这个电路中就保存信息,但是断电后,保存的信息就丢掉了。

二、CPU的操作

CPU从内存中取出指令,执行执行,取出下一条指令…这个过程中,涉及到了哪些硬件和逻辑呢?

1.简单流程

PC寄存器,也叫程序计数器,可以理解为存取速度更快的“内存”,存放的是指令在内存中的地址(地址默认+1)。

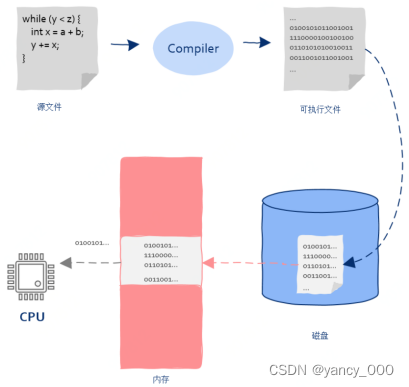

- 内存中的指令,来自于磁盘中的可执行程序

- 磁盘中的可执行程序由编译器(compiler)生成

- 编译器由我们定义的函数生成机器指令

- 函数编译后形成的第一条指令为函数入口,把它写入pc寄存器,就会被CPU执行

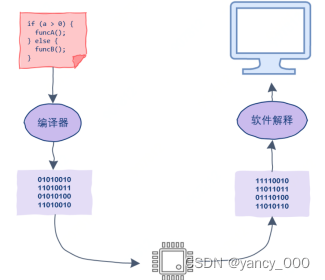

除此之外,CPU的输出需要软件的解释

2.硬件,软件

CPU读写内存过程涉及到的硬件以及硬件逻辑包括:L1 cache、L2 cache、L3 cache、多核缓存一致性协议、MMU、内存、磁盘。

软件主要包括操作系统。

3.分支预测

CPU 会猜一下 if 语句可能会走哪个分支,如果猜对了照常继续,如果猜错了,已经执行的后续指令全部作废,现代 CPU 将“猜”的这个过程称为分支预测。

4.执行函数指令

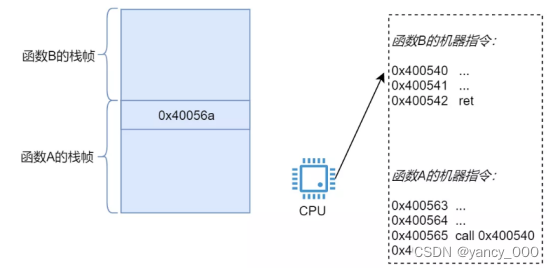

CPU执行函数A的机器指令,call 0x400540,该地址就是函数B的第一条机器指令。

把call指令的下一条指令的地址,也就是0x40056a push到函数A的栈帧中。

函数B最后一条机器指令ret,这条机器指令的作用是告诉CPU跳转到函数A保存在栈帧上的返回地址。

总结

了解到CPU的基本概念后,下一章讲讲内存。

1927

1927

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?