早些时候在实验室进行了一次 AXI 总线入门研讨,我作为 “3/16” 个 AXI 专家(笑)也分享了自己制作的一个 AXI 介绍 PPT。这里分享在网络上,欢迎读者们讨论指正。

hihi,在一个月黑风高的夜晚,感谢大家参加这次有关 AXI 总线的研讨。

我们将首先讨论总线,再介绍 AXI 协议,最后举一些 AXI 总线在 FPGA 中具体应用的例子。

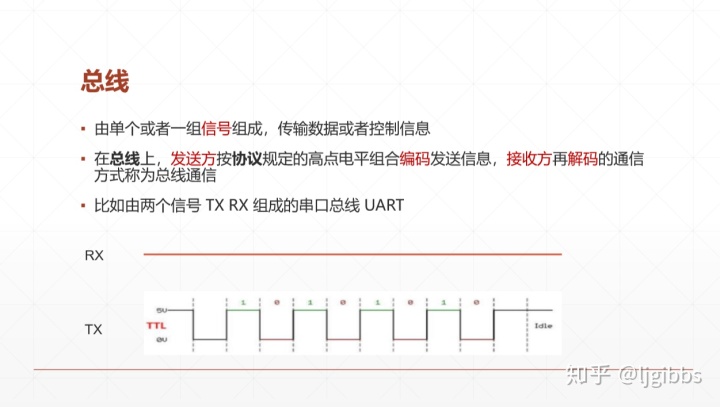

首先从总线开始

比如串口发送和接收就是在指定时刻,信号线的高电平或者低电平表示 1/0

总线一般指信号的集合,协议指的是在总线上的编解码方式

我们在后面说的时候一般不会严格地区分,可能用总线也可能用协议表示

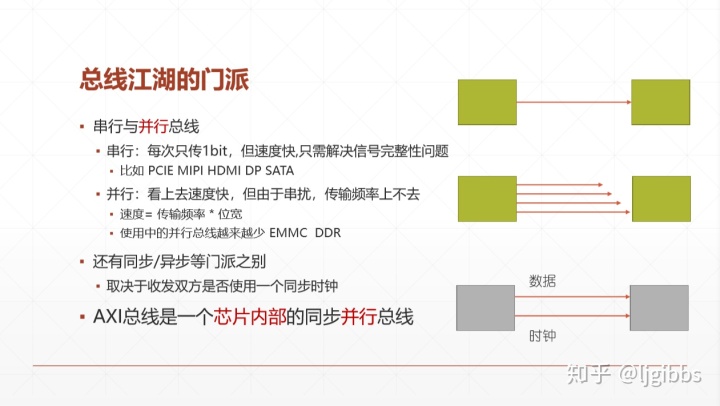

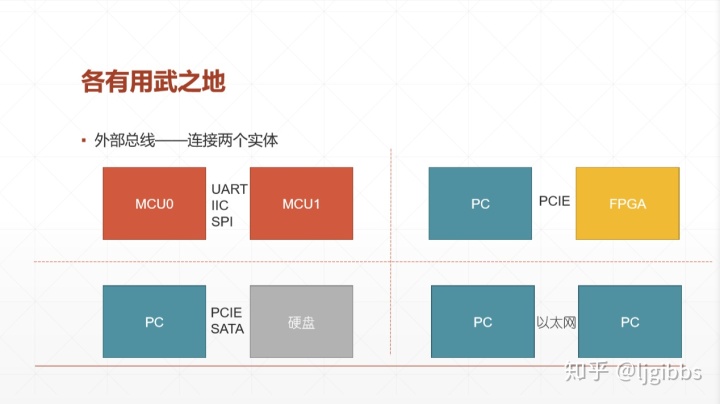

总线按照不同的特性可以分成很多流派,比如根据总线是在我们芯片内部还是外部,可以分为内部总线和外部总线两类

外部总线在一般连接在一块PCB上的两个芯片,那么由于暴露在外部,会受到很多干扰,比如外部环境的电磁干扰,连接器和PCB的损耗,在总线速度较高时,信号完整性会变差,那么会影响传输

内部总线在芯片内部总线,连接内部的不同模块,距离极短,一般不需要考虑干扰和信号完整性问题,速度就可以做得很高,然后一般也不会考虑传输错误的情况

根据总线数据传输的宽度,可以将总线分为串行,数据线位宽1bit,和并行两类,并行总线数据位宽超过 1 bit,比如 4bit 8bit 等等。

串行总线每次只能传输1bit数据,看上去很慢,但可以把这1bit的数据传输做得很快,那么这种高速的1bit总线收发器就是我们说的 SerDes 串行解串器,目前在实验室中的SerDes可以超过100Gbps ,商用也有56G的产品。(2020年 112G Serdes 也商用了)

并行总线看上去传输很快,但由于并行传输存在的串扰问题,串扰加上信号完整性问题会限制传输频率,导致最终的吞吐速率比串行总线低很多,目前仍然广泛使用的并行总线可能主要就是 DDR 了

此外根据收发双方是否使用同一个时钟,还可以分为同步/异步等门派

而我们今天讨论的 AXI 总线是一个芯片内部的同步并行总线

不同类型的总线都有自己的用武之地,对于外部总线来说,最常见的操作就是连接两个实体。

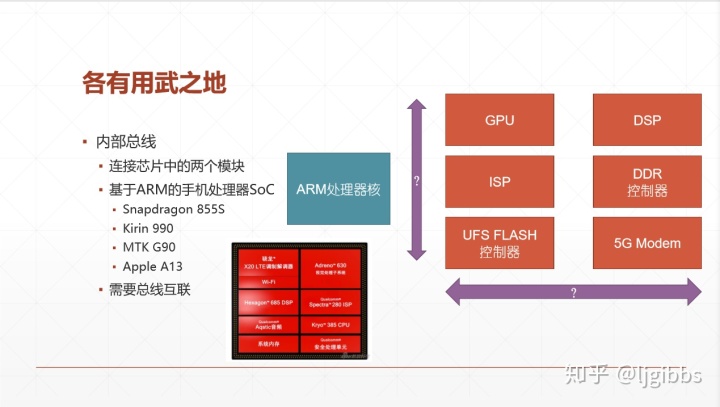

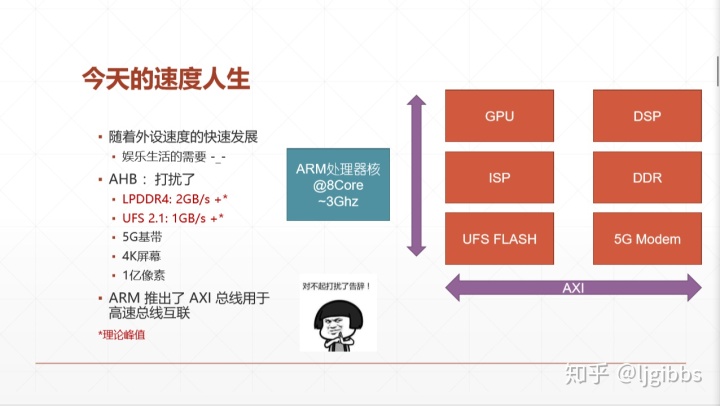

内部总线连接的是芯片内部的模块,我们以大家可能比较熟悉的基于 ARM 的手机处理器系统为例,这实际上就是我们说的 System on Chip 片上系统,在手机的芯片里有我们的处理器核,还有用于渲染画面的 GPU、处理照片的 ISP 、用于调制解调的 DSP 等等,那么这些模块之间都需要总线互联

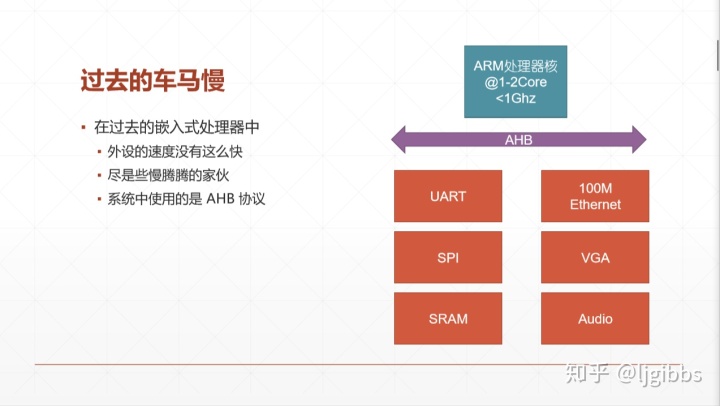

过去的嵌入式处理器中,外设的速度没有这么快,尽是些慢腾腾的家伙。系统中使用的是 AHB 或者其他协议。

但随着外围设备,尤其是存储设备速度不断提升,这也是为了满足大家娱乐生活的需要嘛,AHB总线已经不适应当前 SoC 的发展速度

所以 ARM 就推出了 AXI 总线用于处理器片上系统的高速互联

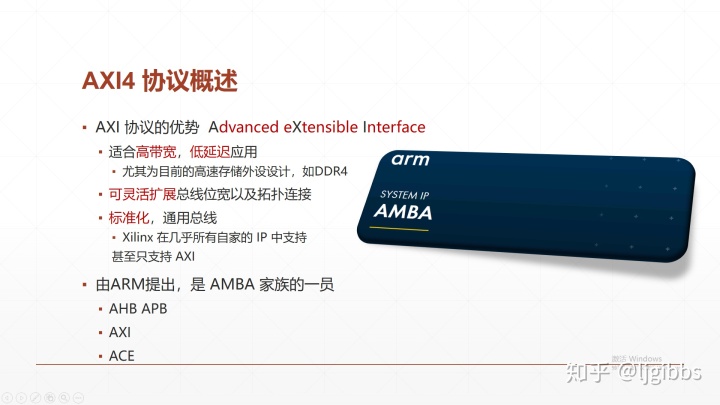

AXI 总线可以通过灵活地扩展总线宽度,拓扑结构,适应不同的高带宽,低延迟应用,并根据存储介质的读写特性设计了专用的机制,适应目前的高速存储外设。

是 AMBA 协议的一部分,由 ARM 制定,有以下几个特点:

高带宽,数据总线位宽最高可以设为1024位

低延迟,适应存储控制器特性的机制以减小读写延迟

标准化,在许多的ip核,fpga 嵌入式应用中都提供了标准的axi协议接口

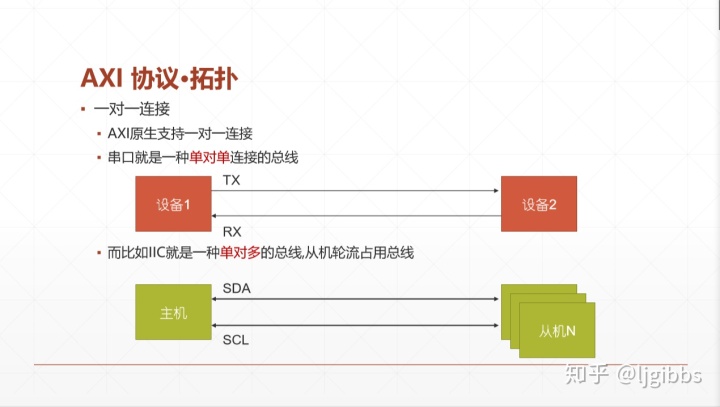

拓扑是指总线的连接方式,有一些总线支持单对单或者单对多的连接机制

AXI 原始支持的是单对单的连接方式,

就好比串口,左边设备的输出信号就对应右边设备的输入信号

那么还有一些协议支持单对多的总线结构,主机的输出信号连到多个从机输入信号,从机轮流地占用总线和主机通信

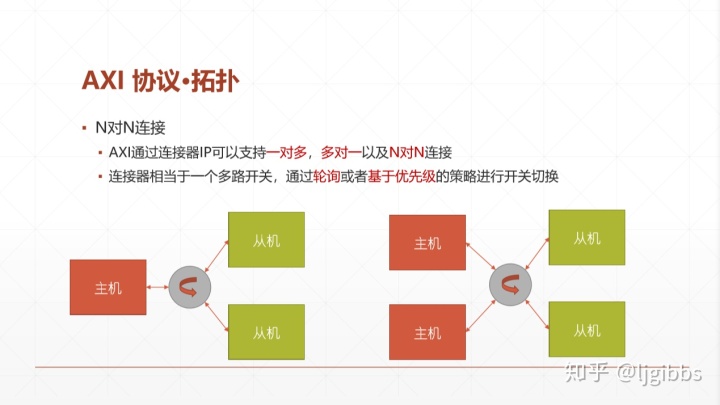

AXI 需要连接连接器 IP (interconnect)来实现N对M的连接,N,M >= 1

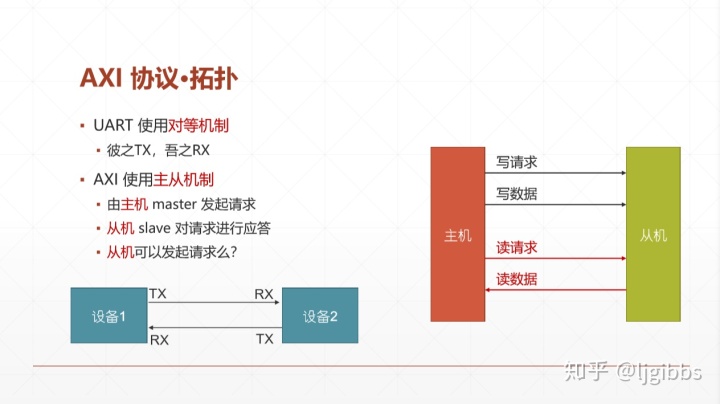

Uart 在两个设备之间是对等的,可以全双工工作

而AXI 相当于一个单工工作模式,信号需要有一个发起方,另一方作为响应方

请求和应答的两方地位实际上是不对等的,分别称为主机与从机

由主机发起请求,从机对请求进行回复。这里提了一个问题:从机是否可以发起读写请求。

那么答案是显然不行,从机压根无法驱动发起请求的信号。

我们接下来来了解 AXI 总线的接口信号

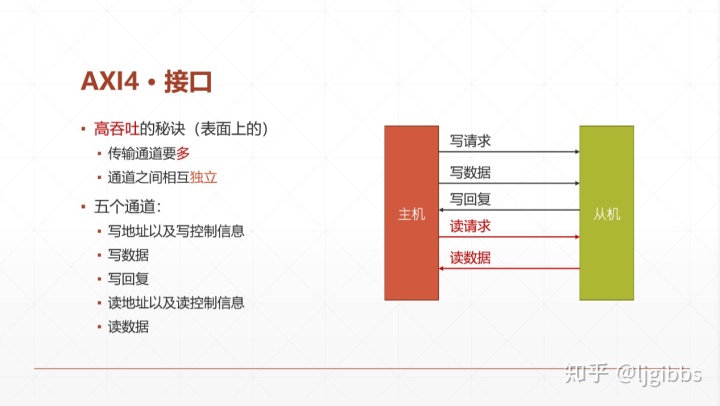

我们之前说 AXI 是一个大吞吐量的总线,那么大吞吐量是如何实现的呢

比较表面的因素有,数据位宽大,以及拥有多个独立的通道,多个通道的操作可以并行,比如同时进行读写传输。再比如在数据传输期间,可以同时发送下一次传输的地址。

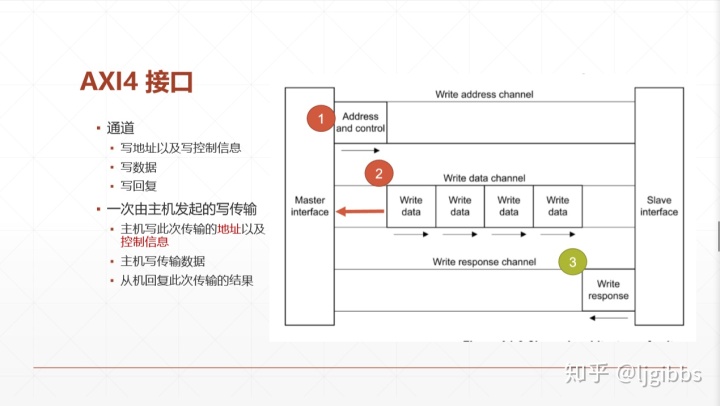

写数据共有3个通道,设置一个独立的写回复通道,这条通道与另两条通道不同,方向是从机 到主机。在一次典型的写传输中,主机写此次传输的地址以及控制信息,从机则将数据回传

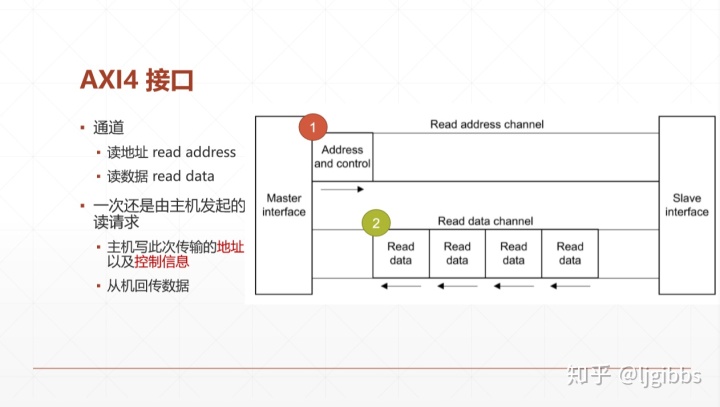

读操作和写操作类似,最大的不同在于没有独立的读回复通道,读回复也是在读数据通道上传输的,因为读回复的传输方向和读数据一致。都是由从机到主机,所以没有必要再增加一条独立通道了。

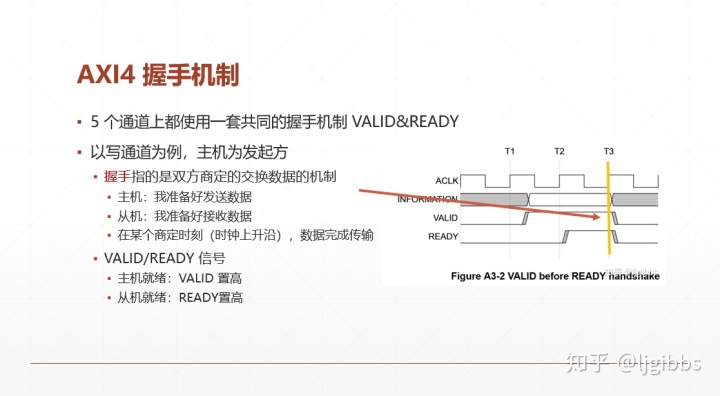

AXI 总线各个通道中都使用了一套握手机制,由 VALID/READY 两个信号构成

VALID/READY 信号的控制方是由当前的通道的发送方/接收方控制。Valid 是发送方,ready 是接收方

作为一种双向流控机制,VALID/READY 机制可以使发送接收双方都有能力控制传输速率。

这里以写通道为例(注意:PPT是以写通道为例,所以主机为发送方。之前版本的PPT没有强调这点)

发送方置高 VALID 信号表示发送方已经将数据,地址或者控制信息放到的写总线上,并保持。

接收方置高 READY 信号表示接收方已经做好接收的准备。

当双方的信息同时为高,时钟上升沿到达后,一组数据传输完成。

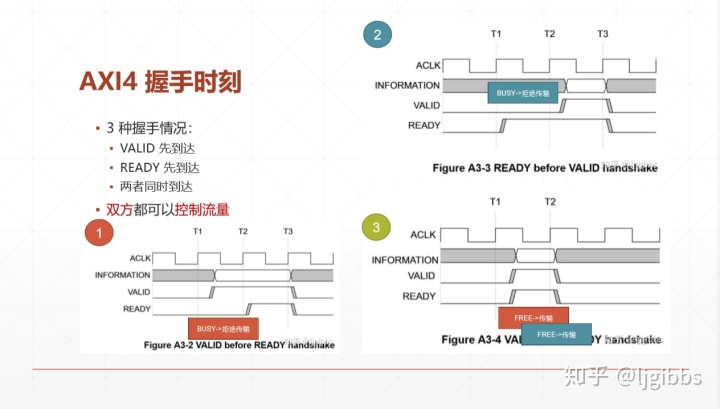

握手中有三种情况:

1.发送方 VALID 信号早早就到了,这时还不到 T2,并带来了新鲜的数据,地址或者控制信息。

但过了 T2 也没见到接收方的 READY 信号。原来是接收方还忙着,忙过了 T2 才来。

好吧,那也行,T3 时刻传输完成。

2. READY 信号提前置起

READY 信号很自由,可以等待 VALID 信号到来再做响应,但也完全可以在 VALID 信号到来前就置高,表示接收端已经做好准备了。

READY 信号与 VALID 不同,接收方可以置起 READY 之后发现:我好像还挺忙。然后拉低 READY 信号,只要这时 VALID 信号没有置起。

3.两者同时置起

同时到达就很简单,等到下一个时钟上升沿 T2,传输就这么轻松愉快地完成了,在一个时钟周期中。

概括一下,发起和接收方都可以通过置低相应的信号来表示自己很忙,从而控制流量。

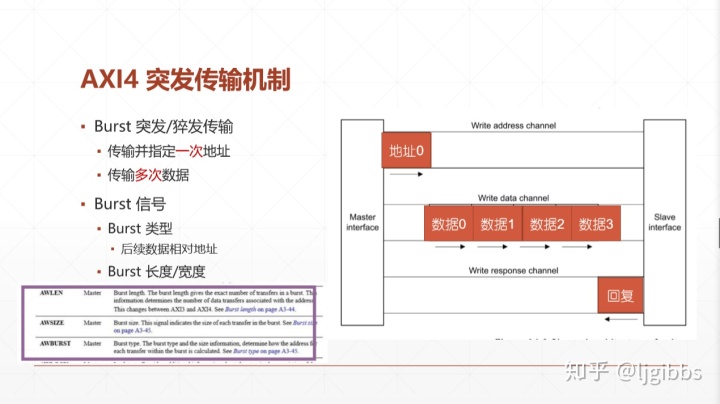

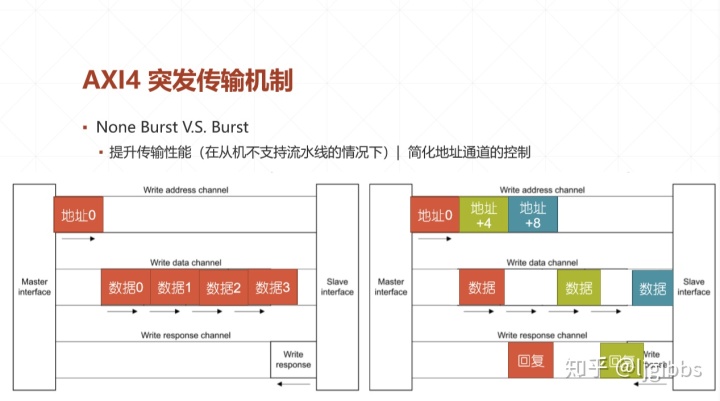

这页开始,我们讨论 AXI 的突发传输机制,burst,也有翻译成猝发传输的,但容易让人联想到猝死,我们还是用突发传输这个词吧。突发传输并不是 AXI 特有的,在 AHB 协议中同样存在。

Burst 我个人的理解是,传输一次地址及其控制信息,进行多次数据传输。

根据数据存放的地址,相较于其实地址的变化,burst 有 3种类型。此外和 burst 相关的信号还有 burst 的长度(AXLEN)以及位宽(AXSIZE)。

突发传输机制可以减少控制信号的复杂度,提高传输的效率

AXI 的三种突发传输类型,后续地址的变化不同,适用于不同的数据传输需求

时钟复位信号方面,AXI 采用同步时钟,一般也采用同步的复位

AXI 总线的 5 个通道总共可以分为 3 类,分别是地址(控制信号)、数据以及回复通道

我们首先讨论地址与控制信息通道的信号。其中读写通道类似,我们以写通道为例来看

信号包括最上方的传输ID(AWID,用于多机传输的标记地址)、地址(AWADDR)、突发传输信号(图中紫色部分)以及握手信号(图中绿色部分)

上一张 PPT 中有部分信号被故意挡住了。包括用于存储和缓存设置的信号。这部分信号用于访问系统缓存时的原子操作以及访问权限的设定。当我们初步了解 AXI 时,可以先忽略

还有一个信号 AXUSER,是一个用户自定义信号。笔者有看过别人这么用:正常的数据通道上传输来自 FIFO 的数据,使用 USER 自定义信号传输 FIFO 的控制与状态信号。这样可以避免将数据与状态信息的拼接至数据通道中

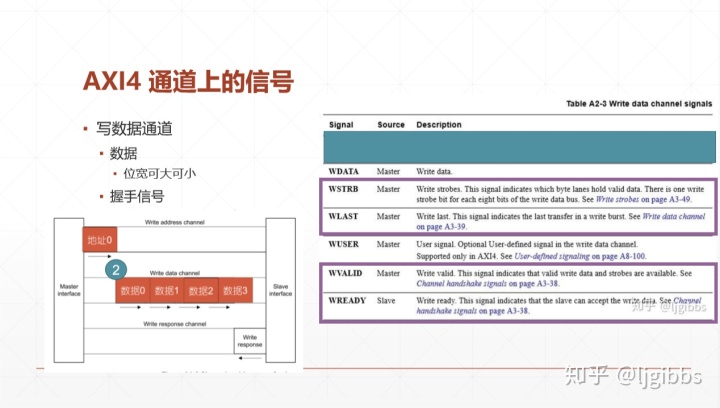

接下来是数据通道,读写数据通道差异还有点大,我们先看写通道。

写通道同样地包括握手信号、自定义信号以及数据信号。这里被挡住的是 WID 信号,这个信号存在于 AXI3,但 AXI4 把他砍掉了,因为不再支持写交织,这个我们将来再讨论。

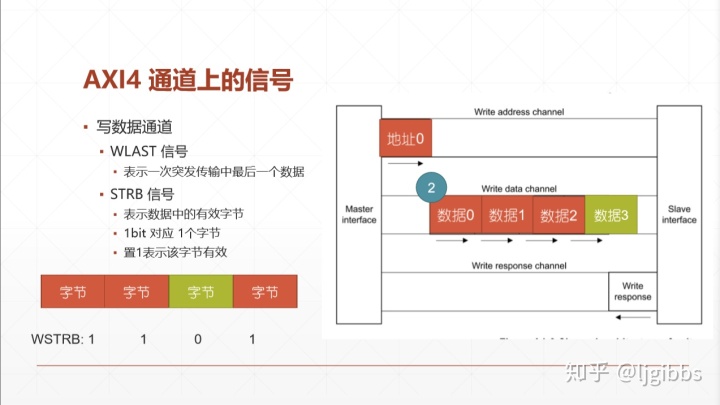

数据信号中, wstrb 信号,用1个bit 来表示1数据字节是否有效,比如数据总线宽度32bit 那么 strb信号为 4 bit 当第一个 bit 为1 时代表第一个字节有效

你说既然这个字节无效,那为啥要传呢?

其实这种情况很常见,举个例子,上位机要写入按地址顺序写入 4 个字节,根据已知信息,主机发现从机的第3个字节不需要修改,所以就可以用 WSTRB 信号通知从机,该字节不需要修改。WSTRB 信号的存在可以免去主机将数据拆分的开销。

wlast 信号代表当前的数据是一次突发传输的最后一个数据(最后一次 transfer),该数据传输结束后,一次突发传输结束。

这里有一点,有人会问:既然突发传输启动时,主机已经告知了从机突发传输长度,从机可以通过计数判断传输是否结束,为什么还需要 wlast 信号。

从协议的角度上来说,这意味着从机设计中可以不统计某次突发传输的长度,仅等待主机送出 wlast 信号即可结束此处传输接收。

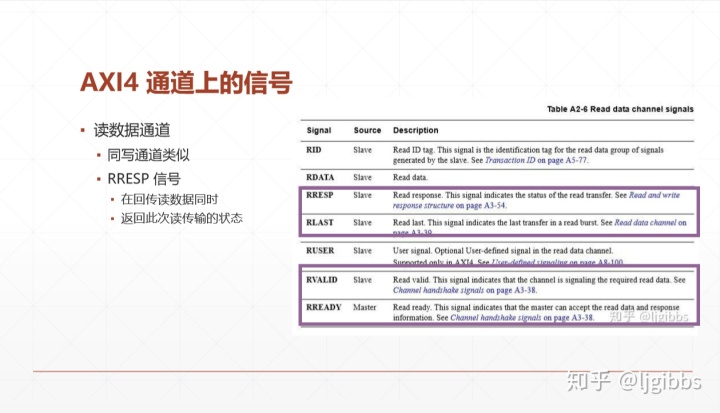

读数据通道的不同在于还包括 RRESP 信号,在传输读数据后,表示此处传输(Transfer)的状态。比如中间节点 interconnect 接收到一个不存在的地址,所以就不知道要将读事务转发给哪个从机,就会回传一个 decode error 给主机,RESP 信号对 debug 非常实用。

此外还包括 RID,用于支持读交织,这在 DDR 访存中是很常用的。

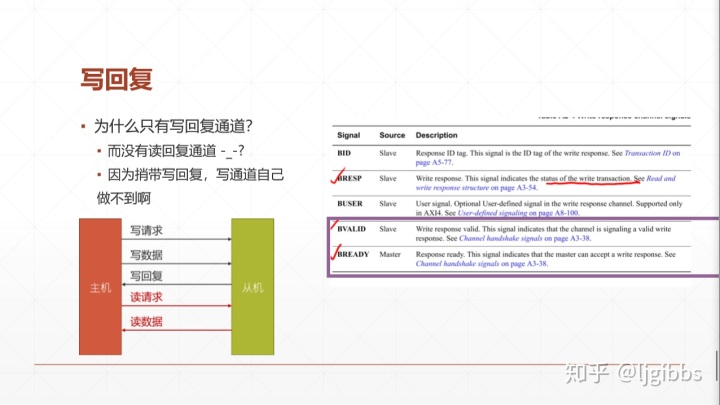

最后是回复通道,回复通道仅有写回复通道。

原因前面提到过,读回复可以通过读数据通道捎带,而写回复则因为与写数据通道方向相反,而做不到捎带。

目前 Xilinx 已经支持了大量 AXI4 总线接口的 IP,右图中都是。

这是一个 BRAM的 ip 核设置界面 分别是 传统接口(native)和 AXI 接口 的 BRAM

比较两者可以发现,AXI 接口的信号更多

但 AXI 接口使用的是一个标准总线,而且 AXI 可以进行一对多、多对多操作,通过总线相应信号实现多机通信。而如果要在 native 接口中实现这点,需要通过自定义的逻辑实现,这些逻辑通常是不利于移植的。

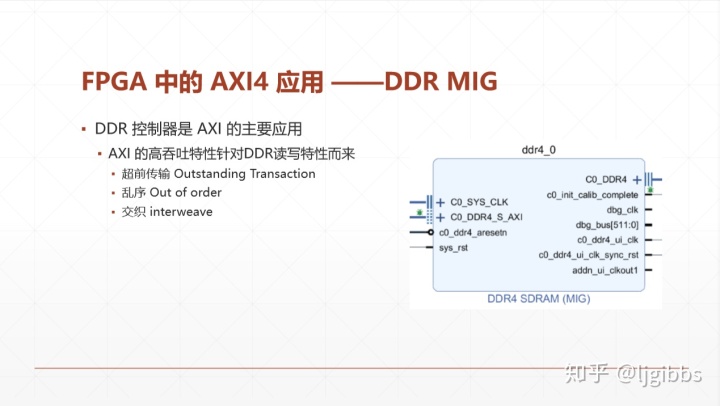

这是 Xilinx 中的 DDR 控制器,前面我们说过 AXI 针对 DDR 读写特点进行了设计,支持多种特性来提高读写 DDR 的效率,包括超前传输、乱序传输、交织传输等。

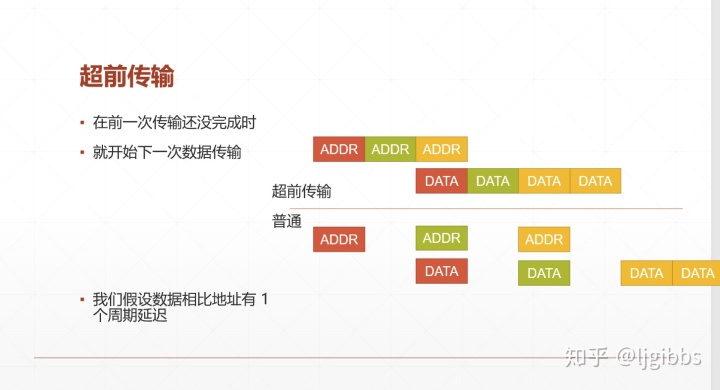

超前传输,称为 outstanding,即在前一次传输事务尚未完成时,就开始下一次传输事务。显然,这样可以提高传输效率,代价是需要缓存更多进行中的传输事务状态。

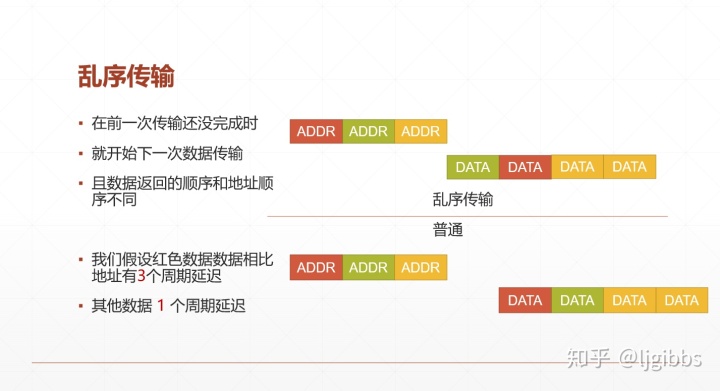

乱序传输(reorder)在超期传输的基础上进一步提高了效率。在传输事务队列中,假设顺序靠后的事务先于队列前部的事务就绪,那么就可以插队开始传输。

交织传输就是在乱序传输的基础上更进一步,插队行为更加高超,无需等待前一个事务完成,就可以将已就绪的事务插到前一个事务中间。

换句话说,乱序传输还讲点武德,如果排在前面的事务已经开始,那么会至少等待前一个事务结束。交织传输则瞅准总线空闲就上了,哪管你事务有没有完成。

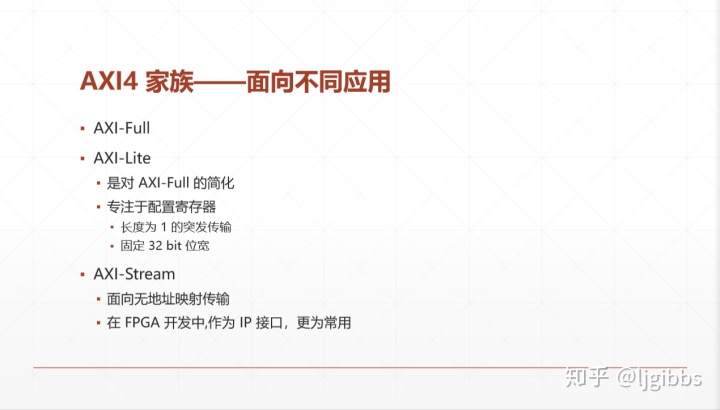

AXI 协议又被称为 AXI-Full 协议,在其基础上又衍生出一个协议家族,面向不同的应用。

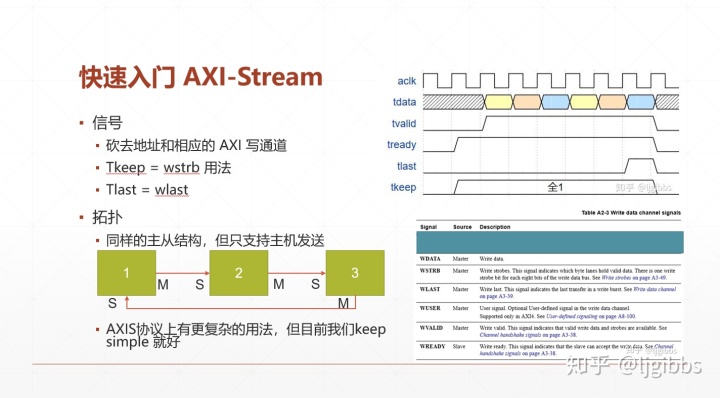

AXI-Stream 是比较常用的总线,接口比较简单,如上右图所示。如下右图的 AXI 写数据通道类似。AXI-Stream 不存在地址的概念,为单对单的拓扑结构,只支持主机发送。

数据就想流一样从 master 流到 slave,故名 stream (我猜的)

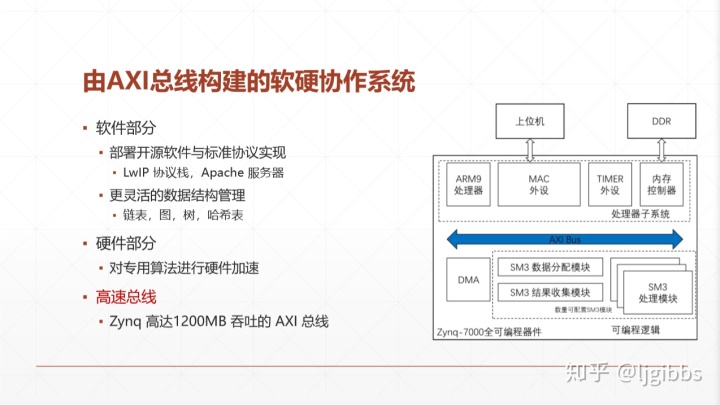

这里我们以 Xilinx Zynq 平台举例,Zynq 的 ARM 处理器系统与可编程逻辑之间通过 AXI 总线连接,处理器为主机,可编程逻辑、DDR控制器等作为外设从机

在控制层面,处理器可以使用 AXI-Lite 总线配置逻辑模块的寄存器

数据层面,处理器可以通过 AXI 总线访问我们在逻辑上实现的算法 IP 或者外部的 DDR,数据的搬运一般由 DMA 完成。

那么通过 AXI 总线起到高速互联作用,我们就可以建立一个软硬协作的系统,充分发挥软硬件的优势。

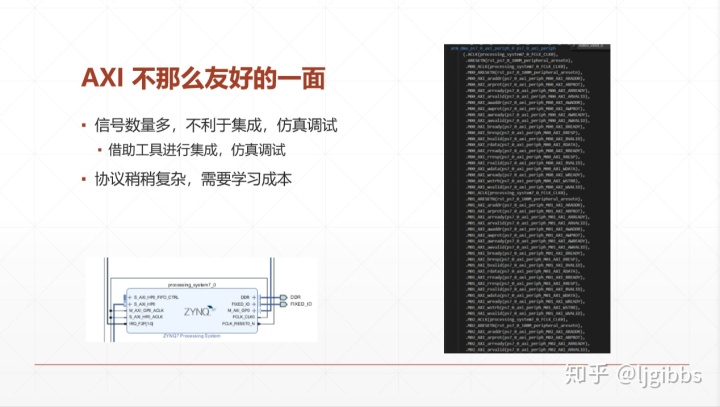

另外,AXI 总线实现的面积比较大。

说实话我好像忘记当天晚上大家提了什么问题了。欢迎读者在下方评论区留言。

505

505

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?